Xilinx Virtex-5 PCIe Endpoint Plus Design with XUPV5-LX110T Tuto...

本篇文档详细介绍了使用Xilinx Virtex-5系列的XUPV5-LX110T PCIe x1 Endpoint Plus Design Creation教程,针对的是Xilinx FPGA(现场可编程门阵列)在PCI Express (PCIe)接口设计中的应用。主要内容包括:

1. **软件要求**:

- 使用的是Xilinx ISE 10.1i SP3版本,这是用于Virtex-5 FPGA的设计和仿真环境。

- 另外,还提到了Xilinx Coregen 10.1i IP Update 3的安装,这是一个用于快速创建和定制核心逻辑的工具。

2. **硬件设置**:

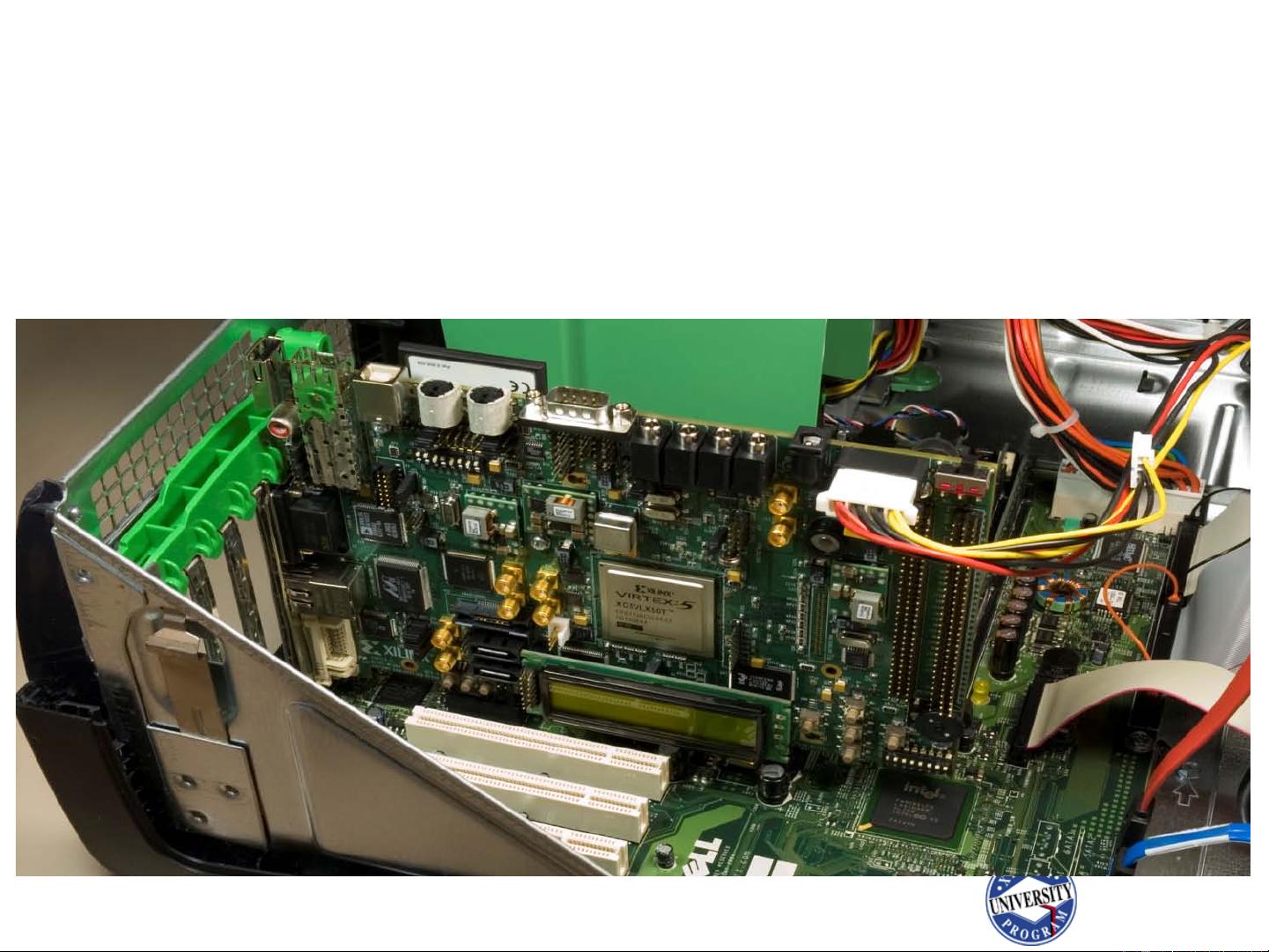

- XUPV5-LX110T板卡需要插入PCIe x1插槽,可以连接PC电源或者使用附带的XUPV5-LX110T专用电源适配器。

- 系统ACED跳线设置,SW3被设置为11010101(1代表开启),这可能涉及到板卡的配置选项。

- SW8的第7位和第8位被设置为AR24826,这是与特定功能或配置有关的设置。

3. **设计创建过程**:

- 通过启动Xilinx ISE 10.1i,进入COREGenerator工具,用户需创建新的项目并选择相应的文件导入或创建PCIe Endpoint逻辑。

4. **PCIe Transceivers**:

文档强调了Virtex-5芯片的Rocket I/O TMGTP/GTX传输器在设计中的关键作用,这些是高速串行通信接口,对于PCIe数据传输至关重要。

5. **测试设计**:

除了设计工具,还推荐使用PciTree Bus Viewer作为辅助工具,可以从指定网站免费下载,并确保将HLP.SYS驱动程序复制到Windows系统目录。

本教程提供了使用Xilinx Virtex-5 LX110T开发PCIe接口设计的完整流程,涵盖了软件安装、硬件配置、设计创建和测试等方面,旨在帮助开发者高效地实现PCIe功能在FPGA中的集成和验证。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2015-07-04 上传

2014-05-18 上传

2014-02-27 上传

2024-11-02 上传

2024-11-02 上传

2024-11-02 上传

chanjoe525

- 粉丝: 1

- 资源: 5

最新资源

- 常用SQL语句+实例

- Flex与Yacc入门

- 08年下 软件设计试卷

- 28套空白个人简历模板.doc

- S3C2410完全开发流程

- sql server 2000中的语句

- S7-300 400的系统软件和标准功能参考手册

- GNU make中文手册

- BGA是PCB 上常用的组件,通常CPU、NORTH BRIDGE、SOUTH BRIDGE、

- Oracle9i数据库管理实务讲座

- 电热锅炉温度控制器 AD590 MCS-51单片机

- 明明白白C指针(很不错哦)

- JavaScript Step By Step

- UML入门与精通(pdf高清晰版)

- Installshield入门指南

- OpenDoc-IntroduceToSpringFramework.pdf