嵌入式系统ARM技术中的FPGA/EPLD黄金组合设计

181 浏览量

更新于2024-08-30

收藏 133KB PDF 举报

"嵌入式系统/ARM技术中的Top Down FPGA/EPLD设计的黄金组合"

在电子技术日新月异的今天,嵌入式系统/ARM技术的发展对中国电子设计工程师们提出了新的挑战和压力。中国电子设计技术仍远远落后于发达国家水平,尤其是在电子技术的基础产业,即IC/ASIC方面。然而,FPGA/EPLD的发展正逐步取代越来越多的ASIC市场,具有可重复使用、小批量、低投入、高性能、高密度、开发周期短等诸多优点,国内更多的工程师们乐于采用。

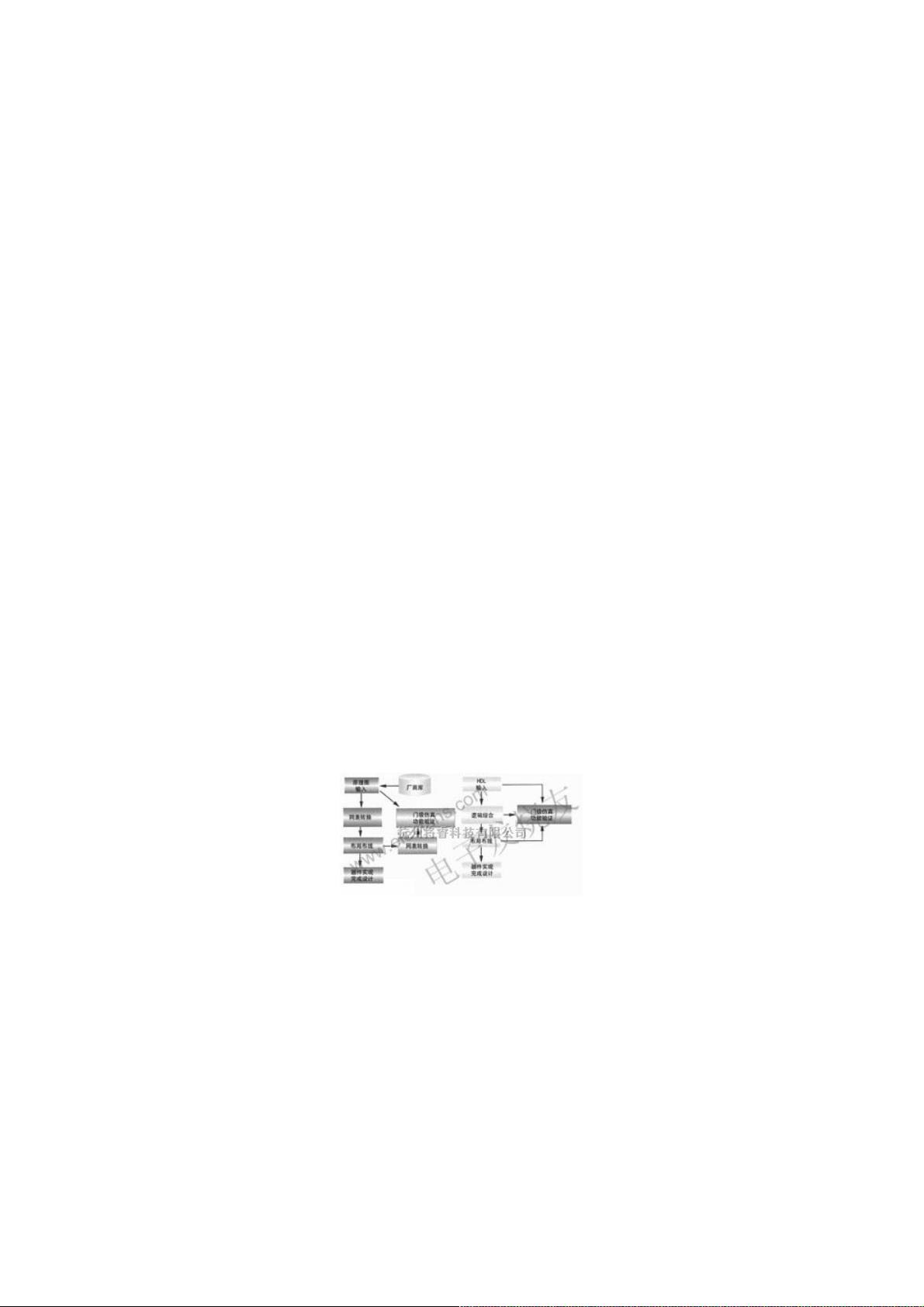

FPGA/EPLD的自上而下(Top-Down)设计方法是当前嵌入式系统/ARM技术中的一种黄金组合。这种设计方法可以降低诸多产业投资成本,也可以培养一大批国内的Top-Down设计人才,从而提高国内Top-Down设计的整体水平,为将来国内ASIC产业的快速、健康发展打下坚实的基础。

Top-Down设计方法的优点包括:

* 可重复使用:FPGA/EPLD可以重复使用,减少了设计和制造的成本。

* 小批量:FPGA/EPLD可以满足小批量生产的需求,降低了投资成本。

* 低投入:FPGA/EPLD的设计和制造不需要大量的投资,降低了成本。

* 高性能:FPGA/EPLD具有高性能,可以满足复杂的设计需求。

* 高密度:FPGA/EPLD具有高密度,可以满足小型化的设计需求。

* 开发周期短:FPGA/EPLD的设计和制造周期短,可以快速满足市场需求。

FPGA/EPLD的发展对中国电子设计技术的发展具有重要意义。通过引进先进的FPGA Top-Down设计工具,中国电子设计工程师们可以降低设计和制造的成本,提高设计的效率和质量,提高国内ASIC产业的竞争力,为将来国内ASIC产业的快速、健康发展打下坚实的基础。

FPGA/EPLD的自上而下(Top-Down)设计方法是当前嵌入式系统/ARM技术中的一种黄金组合,对中国电子设计技术的发展具有重要意义。

2020-10-22 上传

2020-11-19 上传

2020-10-19 上传

2020-11-07 上传

2022-11-29 上传

2022-11-29 上传

点击了解资源详情

点击了解资源详情

weixin_38731385

- 粉丝: 2

- 资源: 871

最新资源

- Aspose资源包:转PDF无水印学习工具

- Go语言控制台输入输出操作教程

- 红外遥控报警器原理及应用详解下载

- 控制卷筒纸侧面位置的先进装置技术解析

- 易语言加解密例程源码详解与实践

- SpringMVC客户管理系统:Hibernate与Bootstrap集成实践

- 深入理解JavaScript Set与WeakSet的使用

- 深入解析接收存储及发送装置的广播技术方法

- zyString模块1.0源码公开-易语言编程利器

- Android记分板UI设计:SimpleScoreboard的简洁与高效

- 量子网格列设置存储组件:开源解决方案

- 全面技术源码合集:CcVita Php Check v1.1

- 中军创易语言抢购软件:付款功能解析

- Python手动实现图像滤波教程

- MATLAB源代码实现基于DFT的量子传输分析

- 开源程序Hukoch.exe:简化食谱管理与导入功能