Spartan-6 FPGA Configuration User Guide www.xilinx.com 17

UG380 (v2.1) February 22, 2010

Design Considerations

The Low-Cost Priority Solution

The option with the lowest cost varies depending on the specific application.

• If there is spare nonvolatile memory already available in the system, the bitstream

image can be stored in system memory. It can even be stored on a hard drive or

downloaded remotely over a network connection. If so, one of the downloaded

modes should be considered: Slave SelectMAP Mode, Slave Serial Mode, or JTAG.

• If nonvolatile memory is already required for an application, it is possible to

consolidate the memory. For example, the FPGA configuration bitstream(s) can be

stored with any processor code for the board. If the processor is a MicroBlaze

™

embedded processor in the FPGA, the FPGA configuration data and the MicroBlaze

processor code can share the same nonvolatile memory device.

• Spartan-6 FPGAs optionally configure directly from commodity SPI serial flash and

parallel NOR flash memories. See Chapter 2, Configuration Interface Basics. Also see

XAPP973

, Indirect Programming of BPI PROMs with Virtex-5 FPGAs, and XAPP974,

Indirect Programming of SPI Serial Flash PROMs with Spartan-3A FPGAs.

The High-Speed Priority Option

Some applications require the logic to be operational within a short time. Certain FPGA

configuration modes and methods are faster than others. The configuration time includes

the initialization time plus the configuration time. Configuration time depends on the size

of the device and speed of the configuration logic. For example, configuring at 33 MHz

with a 4-bit data bus, a Spartan-6 XC6SLX16 FPGA requires ~28 ms to receive its 3.6 Mb of

configuration data.

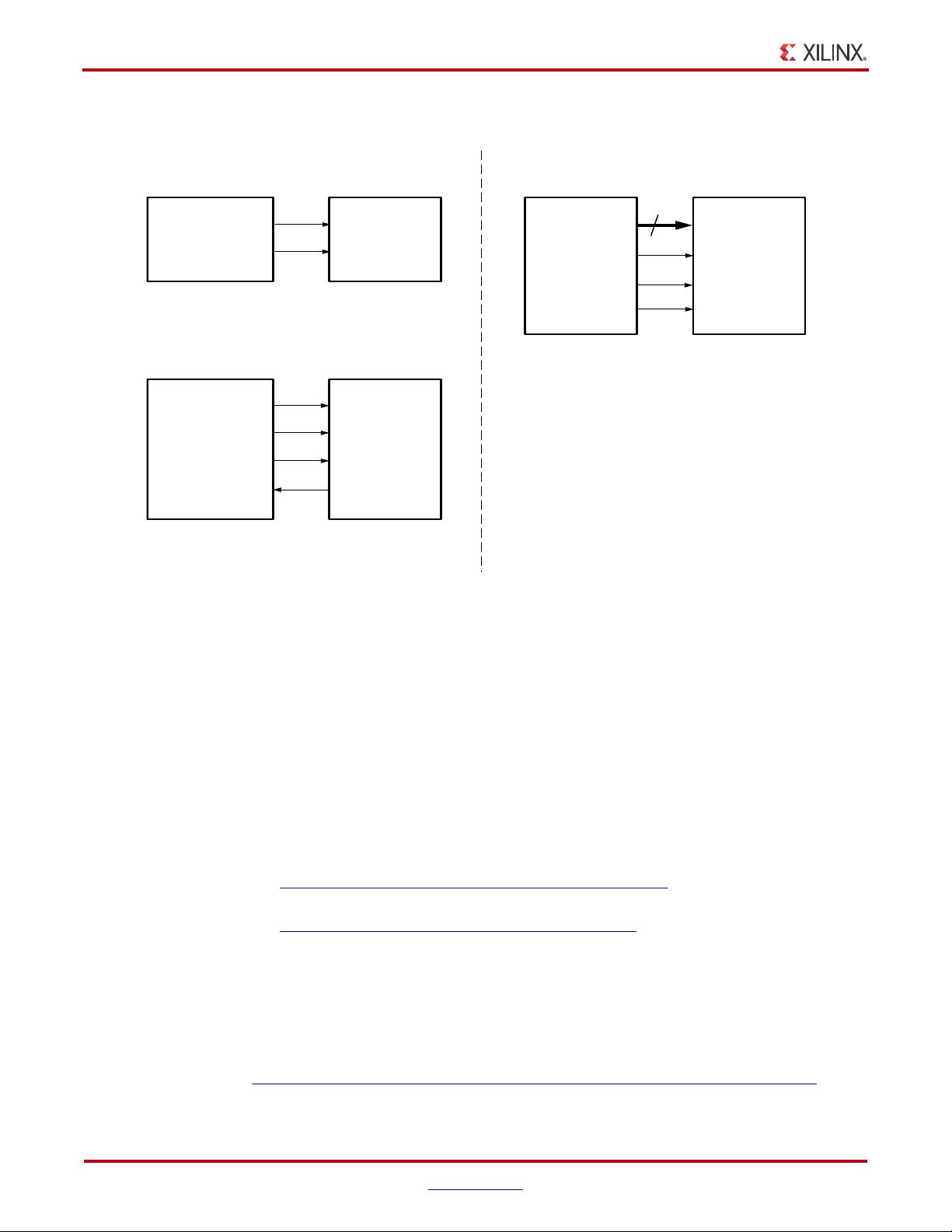

• At the same clock frequency, parallel configuration modes are inherently faster than

the serial modes because they program multiple bits at a time.

• Configuring a single FPGA is inherently faster than configuring multiple FPGAs in a

daisy-chain. In a multi-FPGA design where configuration speed is a concern, each

FPGA should be configured separately and in parallel.

• In Master modes, the FPGA internally generates the CCLK configuration clock signal.

By default, the CCLK frequency starts out low but can be increased using the

ConfigRate bitstream option. The maximum supported CCLK frequency setting

depends on the read specifications for the attached nonvolatile memory. A faster

memory enables faster configuration. The FPGA's CCLK output frequency varies

with process, voltage, and temperature. The fastest guaranteed configuration rate

depends on the slowest guaranteed CCLK frequency, as shown in the Spartan-6 FPGA

data sheet. If an external clock is available on the board, it is also possible to configure

the FPGA in Slave mode while using Xilinx Platform Flash.

• If an external clock is available on the board, the FPGA supports the ability to connect

and use an external clock source during Master mode configuration. It is also possible

to use an external clock source to configure the FPGA in a slave mode while using

Xilinx Platform Flash. The external clock source during configuration enables

predictable configuration times to be achieved in Master modes as well as Slave

modes.

Conforming to PCI Link Activation Requirements

The PCI™ Local Bus Specification, Revision 3.0 (“the PCI specification”) defines a number

of power and reset requirements. These requirements, when considered in an FPGA

implementation, create several challenges that must be addressed for long term reliability