VHDL基础与EDA技术应用详解

版权申诉

45 浏览量

更新于2024-07-03

收藏 1.32MB PPT 举报

"EDA技术与应用:第3章 VHDL.ppt"

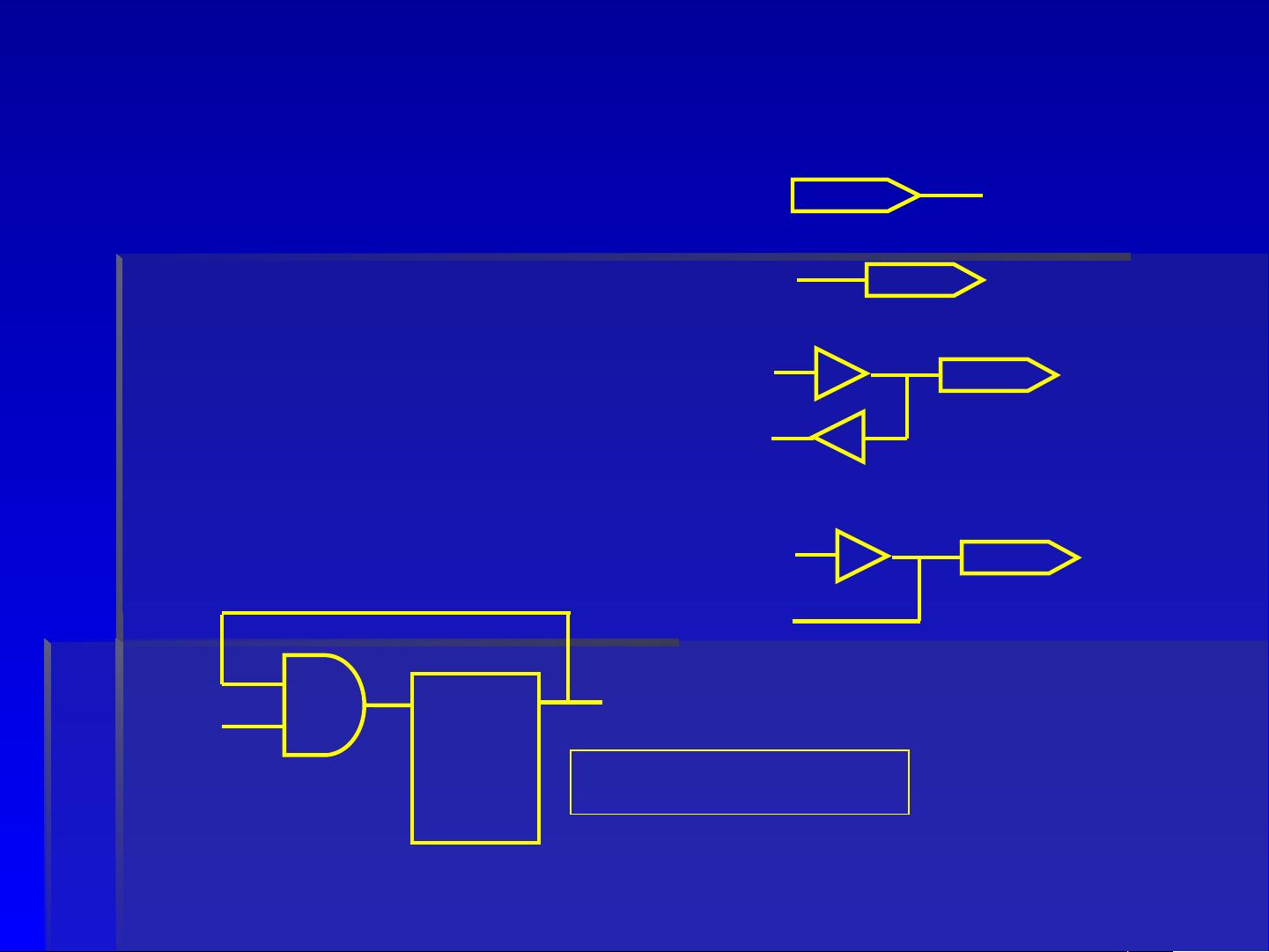

VHDL,全称为Very High-Speed Integrated Circuit Hardware Description Language,是一种广泛应用于电子设计自动化(EDA)领域的硬件描述语言。它允许工程师以文本形式描述数字系统的结构和行为,支持从概念到实现的全过程,包括设计、仿真、综合、验证和布局布线。本章主要介绍了VHDL的基本知识、语言要素、设计实体结构以及使用VHDL描述数字逻辑电路的方法。

VHDL的设计实体是其核心组成部分,它由实体(ENTITY)、结构体(ARCHITECTURE)和配置(CONFIGURATION)组成。实体定义了设计模块的外部接口,包括输入、输出信号和时钟等;结构体则描述了实体内部的逻辑功能,可以包含进程(PROCESS)和其他并行结构。配置部分用于指定特定实体如何映射到实际的硬件资源。

在VHDL编程中,库(LIBRARY)是存放预设计好的程序包和实体的地方,这些程序包通常包含了常用的功能模块和宏定义,能够方便地被其他设计引用。程序包(PACKAGE)则用来组织和重用代码,它可以封装常量、类型定义、函数和过程等,提高代码的可读性和复用性。

VHDL语言要素包括数据类型、运算符、实体声明、结构体定义、进程声明等。数据类型如BIT、STD_LOGIC及其矢量类型,支持位操作和逻辑运算。运算符涵盖了算术、比较和逻辑操作。实体声明定义了设计实体的输入、输出端口,而结构体定义则描述了这些端口之间的关系和操作。

VHDL设计流程一般包括以下几个步骤:先进行系统级描述,然后进行功能仿真验证,接着通过综合工具将VHDL代码转换成门级网表,最后进行布局布线生成物理设计。VHDL的仿真功能允许在设计的不同阶段进行行为和时序验证,确保设计的正确性。

VHDL支持多种描述风格,如数据流、行为和结构化描述,这使得它能够灵活地适应不同复杂度和粒度的电路设计。例如,可以使用过程描述复杂的时序逻辑,用并行结构描述组合逻辑,或者用类C语言风格的行为描述高级算法。

为了提高代码的可读性和维护性,VHDL编程遵循一定的规范,如使用层次缩进来展示代码结构,关键字大写以突出重要性,注释使用双横线"--"标识。在编译和综合过程中,VHDL编译器并不区分大小写,但建议使用标准格式以增加代码的可读性。

总结起来,VHDL是电子设计中不可或缺的工具,它提供了一种强大且灵活的方式,帮助工程师精确地描述和实现数字系统。理解和掌握VHDL语言及其设计方法,是现代电子工程师必备的技能之一。

2022-06-18 上传

2022-06-10 上传

2022-06-11 上传

378 浏览量

168 浏览量

198 浏览量

112 浏览量

1089 浏览量

266 浏览量

智慧安全方案

- 粉丝: 3847

- 资源: 59万+

最新资源

- SQL SERVER实用经验技巧集

- 程序设计需求分析模板

- 15天学会jQuery(0-5).15天学会jQuery(0-5).

- Android编程指南(en)

- White-Box Testing

- mtk经典方案pdf

- Java 程序语言设计

- signaling 7

- AT91RM9200 中断控制器详解(AIC)

- ADO.Net完全攻略.pdf

- Building embeded Linux

- Class Discussion 2 - HP

- 《计算机软件文档编制规范》GB-T8567-2006 (文档结构已整理,word版)

- 数字功率放大器数字PWM线性化技术

- 2008惠普的一次考试题

- UNIX系统操作命令