于博士分享清晰CADENCE原理图:CS4272接口详解

需积分: 9 12 浏览量

更新于2024-09-04

1

收藏 118KB PDF 举报

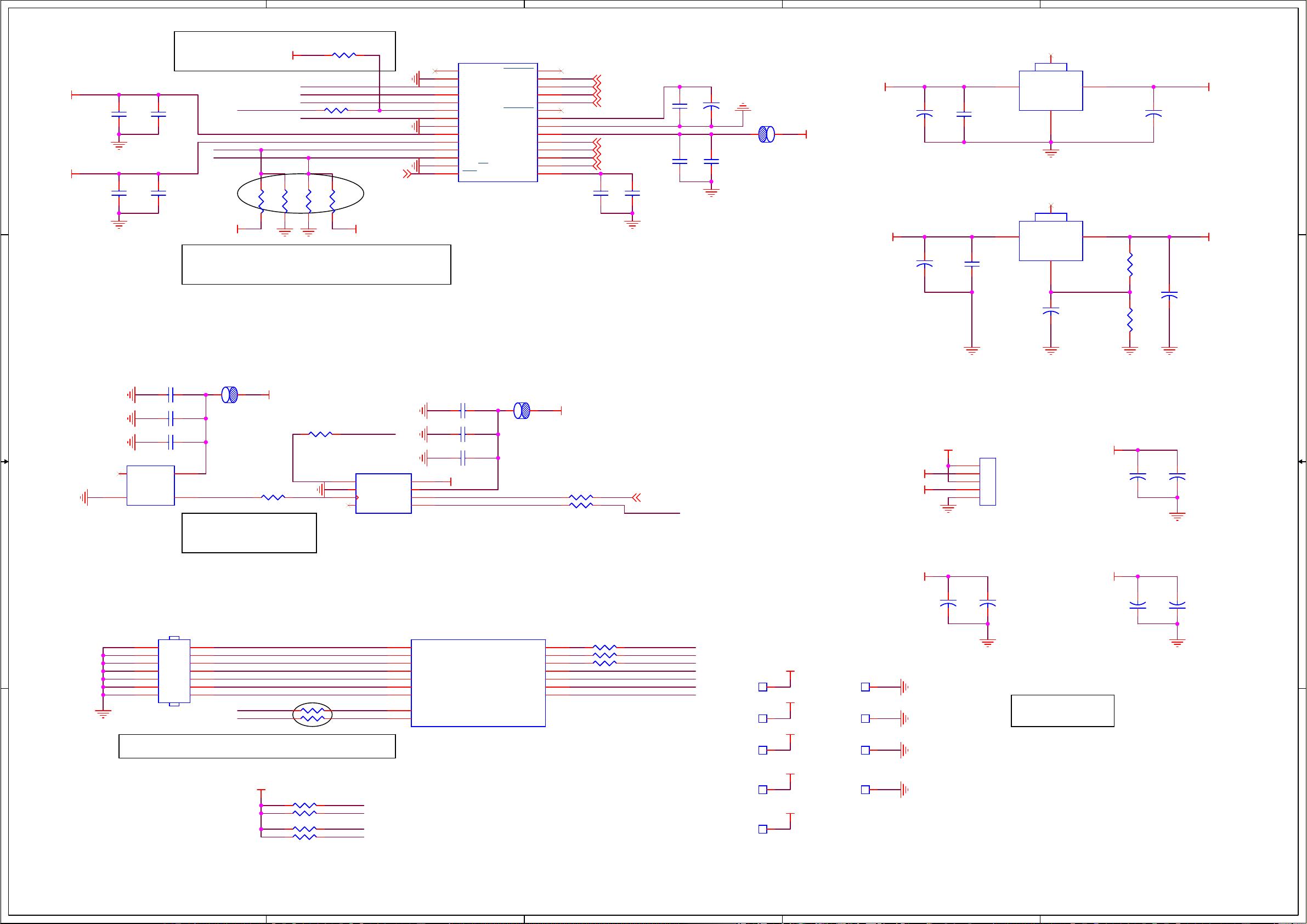

"这是一份名为《于博士原理图文件.pdf》的CADENCE相关教程资料,由网友分享,旨在帮助学习者理解和掌握CADENCE设计工具中的原理图绘制。文件详细列出了CS4272音频编解码器的电路图,包括各种接口信号如MCLK、LRCLK、SCLK、SDIN/SDOUT等,以及电源连接和去耦网络。其中特别强调了电路设计的关键要点:

1. 信号时钟:MCLK(主时钟)、LRCLK(低速率时钟)和SCLK(系统时钟)是音频处理的核心时序,它们的连接对芯片功能至关重要。

2. 数据接口:SDA_M1、SCL_M0用于串行数据传输,SDA0和SCL0是可能的备用或辅助接口。

3. 电源管理:VCC电压等级丰富,包括3.3V、5V和12V,确保了不同组件的供电需求。外部电源滤波和去耦电阻的使用对于电源完整性至关重要,应根据芯片工作模式进行调整。

4. 复位与控制:CS4272_RESET引脚的复位操作由DSP控制,通常在MCBSP_CLKIN时钟稳定后再执行,以确保正确初始化。

5. 工作模式选择:Standalone模式下,可能需要配置电阻来实现主从工作模式,而在MasterMode下,SlaveMode不应被安装。

6. 模拟滤波和去耦:C15、C17和L1等电容和电感元件用于滤波和减少噪声,确保信号质量。

7. XNET:XNET中的一些引脚可能需要配置馈线返回输入,如TP8,以优化信号传输。

8. 注意事项:电源完整性、局部管脚去耦以及复位信号的控制都是设计过程中不可忽视的细节,确保了系统的可靠性和稳定性。

这份文档对于理解CADENCE设计原理和实践应用具有很高的价值,特别是对于学习音频编解码器硬件设计的同学来说,提供了宝贵的参考资源。"

156 浏览量

386 浏览量

1679 浏览量

167 浏览量

291 浏览量

642 浏览量

165 浏览量

208 浏览量

555 浏览量

daydayup!!

- 粉丝: 1843

最新资源

- 项目管理词汇英汉对照索引:推动国内发展的关键工具

- Microsoft Visual C++ 6.0 MFC类库详解与配套资源

- ASP.NET中datalist的嵌套使用

- 安全清理C盘:优化硬盘空间的全面指南

- Eclipse中文入门:平台与基本操作详解

- 武大吉奥GeoSurf5.2:国产WebGIS平台,跨平台服务与开发利器

- RK2706 USB设备升级教程

- WebGIS入门与发展趋势:互联网驱动的GIS普及

- ARM 编程技巧:编译器优化和编程指南

- 802.11无线局域网组网与移动性分析

- 解决Windows多重引导故障全攻略

- Java编程规范与最佳实践

- 硬盘安装Linux:步骤详解与分区指南

- 萨师煊版《数据库系统概论》习题解析

- PC汇编语言入门:32位汇编基础

- SAP R/3系统详解:企业全面管理解决方案