FPGA设计实践:IP核使用与ASIC优化

需积分: 16 70 浏览量

更新于2024-07-21

收藏 1.89MB PDF 举报

"fpga设计IP核使用"

在FPGA设计中,IP( Intellectual Property)核是一个关键的组成部分,它代表了预先设计并验证过的数字逻辑功能模块。这些模块可以是简单的逻辑门,也可以是复杂的处理器内核或者接口控制器。使用IP核可以显著提高设计效率,减少开发时间和成本。

首先,理解IP核的使用方法至关重要。IP核通常以库的形式提供,设计师可以通过选择合适的IP核,将其集成到自己的FPGA设计中。这涉及到配置、连接和验证等步骤。配置是指根据具体需求调整IP核的参数;连接则是在顶层设计中将IP核与其他模块正确互联;验证则是确保IP核在系统中的功能和性能满足预期。

在FPGA编程设计中,有多种思路可以采用。例如,可以使用硬件描述语言(如VHDL或Verilog)从底层构建逻辑,也可以利用高级综合工具,如SystemVerilog或SystemC,以更接近软件的方式来描述设计。此外,还有基于图形化界面的IP Integrator等工具,允许设计师通过拖拽和连接来构建系统级设计。

在设计案例中,我们经常遇到以下问题:

1. ASIC目标:设计的目标可能是最终转化为ASIC(Application-Specific Integrated Circuit),这意味着FPGA设计需要考虑可移植性和优化,以适应大规模集成电路的制造工艺。

2. 所见非所得:在FPGA设计中,逻辑综合和布局布线的过程可能导致实际实现的性能与预期有所不同,因此需要对设计进行充分的仿真和验证。

3. 面积与速度的协调:在资源有限的FPGA上,需要平衡设计的面积(占用的逻辑资源)和速度(运行速度),以达到最优性能。

4. 测试向量生成:为了确保设计的可靠性,需要生成测试向量进行功能和性能测试,这通常需要专门的激励生成工具和技术。

5. 系统基本结构:设计中会涉及各种基本结构,如计数器、加法器、乘法器和除法器,这些都是构建复杂系统的基础。

6. CORDIC算法:在处理非线性计算时,如角度转换和浮点运算,CORDIC(Coarse RODIC, Coordinate Rotation Digital Computer)方法是一种高效且节省硬件资源的算法。

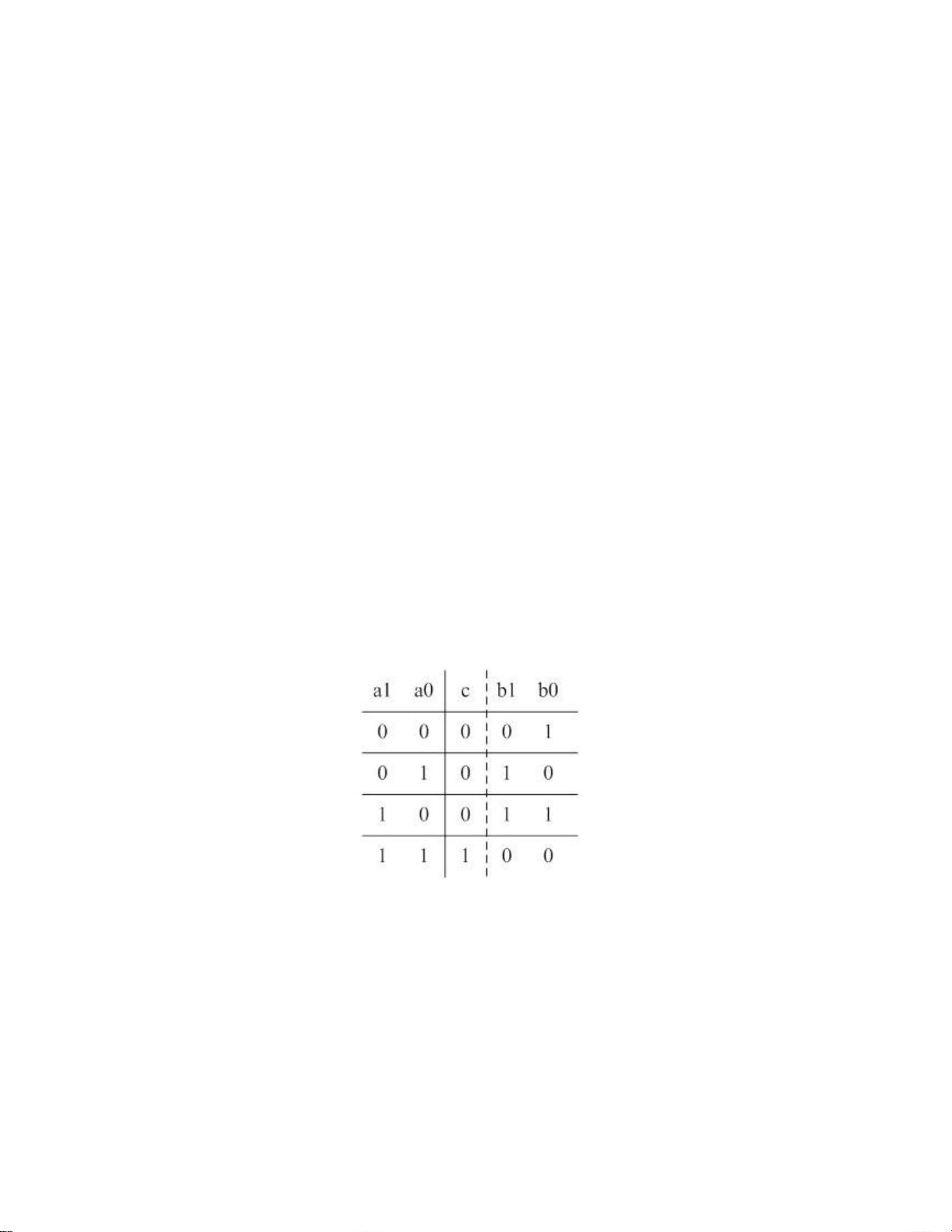

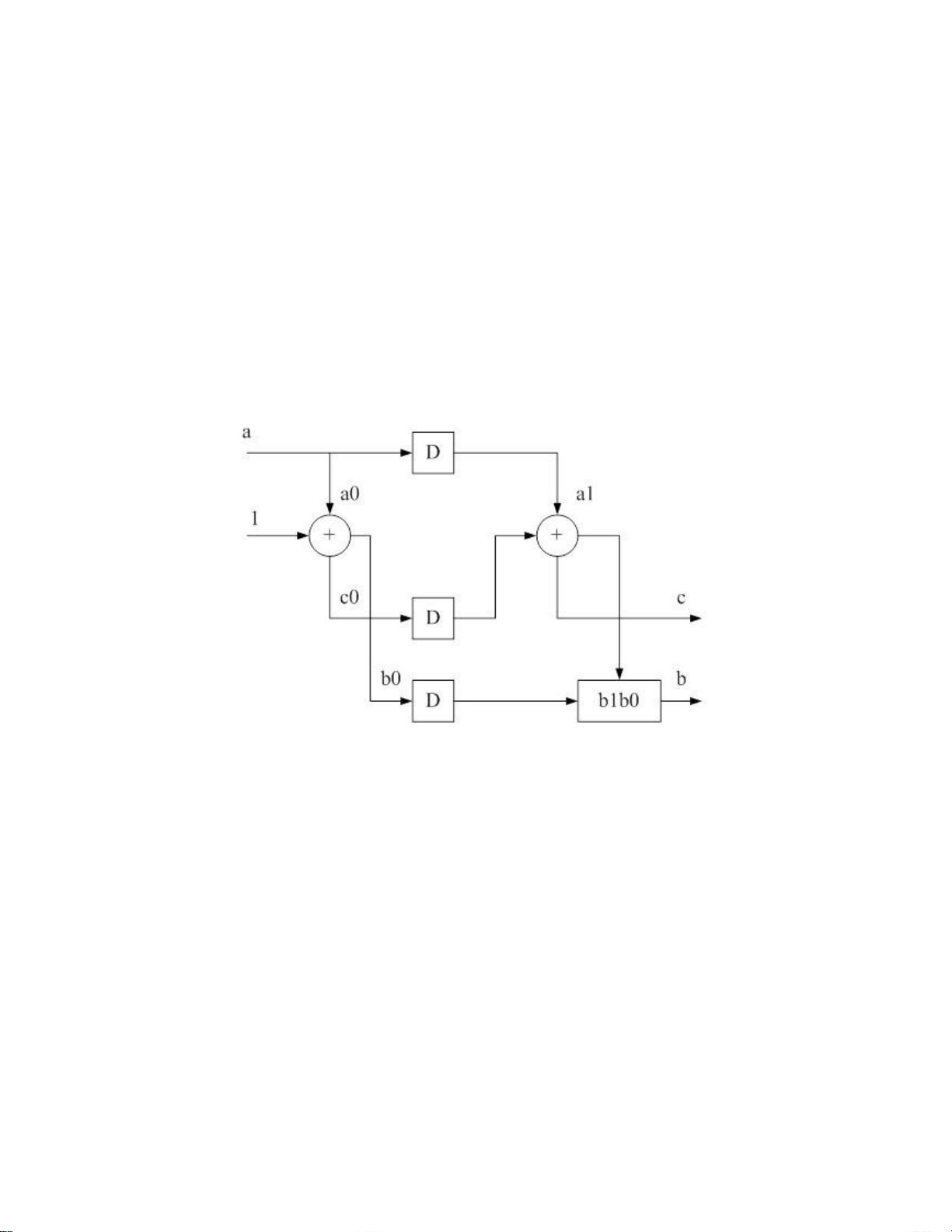

7. 触发器链和其他串行结构:在设计中,可能需要构建串行数据处理链,如D触发器链,来实现特定的数据流控制和存储功能。

每个设计案例都提供了深入理解和解决FPGA设计问题的机会,从基础的逻辑单元到复杂的系统架构,不断积累经验,提升设计能力。通过实践这些案例,设计师可以更好地掌握IP核的使用,优化FPGA设计,从而实现高效、可靠的系统解决方案。

1384 浏览量

120 浏览量

215 浏览量

287 浏览量

433 浏览量

281 浏览量

2020-10-19 上传

1002 浏览量

guyu154

- 粉丝: 0

- 资源: 2

最新资源

- FLASH脚本讲解,FLASH脚本讲解,FLASH脚本讲解

- 阿虚嵌入式linux移植笔记

- ASP.NET C#编码规范

- 基于J2EE的Ajax宝典.pdf

- 嵌入式Linux应用程序开发详解

- 如何做研究,如何写论文

- JSP 2.0 EL 手册 (Expression Language)

- ethereal用户手册

- JavaScript Reference Guide.pdf

- ibatis开发指南

- IBM-PC汇编语言答案

- JAVA编码规范及实践

- GCC中文手册【中文GCC帮助】

- 电力行业应用解决方案

- Beginning JSP JSF and Tomcat Web Development

- 30分钟学会STL 比较不错的东西适合初学者