FPGA设计规范与流程详解

需积分: 9 195 浏览量

更新于2024-07-24

收藏 197KB DOC 举报

"FPGA设计规范"

在电子设计领域,FPGA(Field-Programmable Gate Array)因其灵活性和高速设计验证能力而被广泛应用于原型实现和ASIC(Application-Specific Integrated Circuit)原型验证。本设计规范旨在提供一个清晰的FPGA设计流程,确保设计的合理性、一致性和高效性,并促进团队成员之间的协同工作。

1. 基于HDL的FPGA设计流程概述

设计流程通常包括以下几个关键步骤:

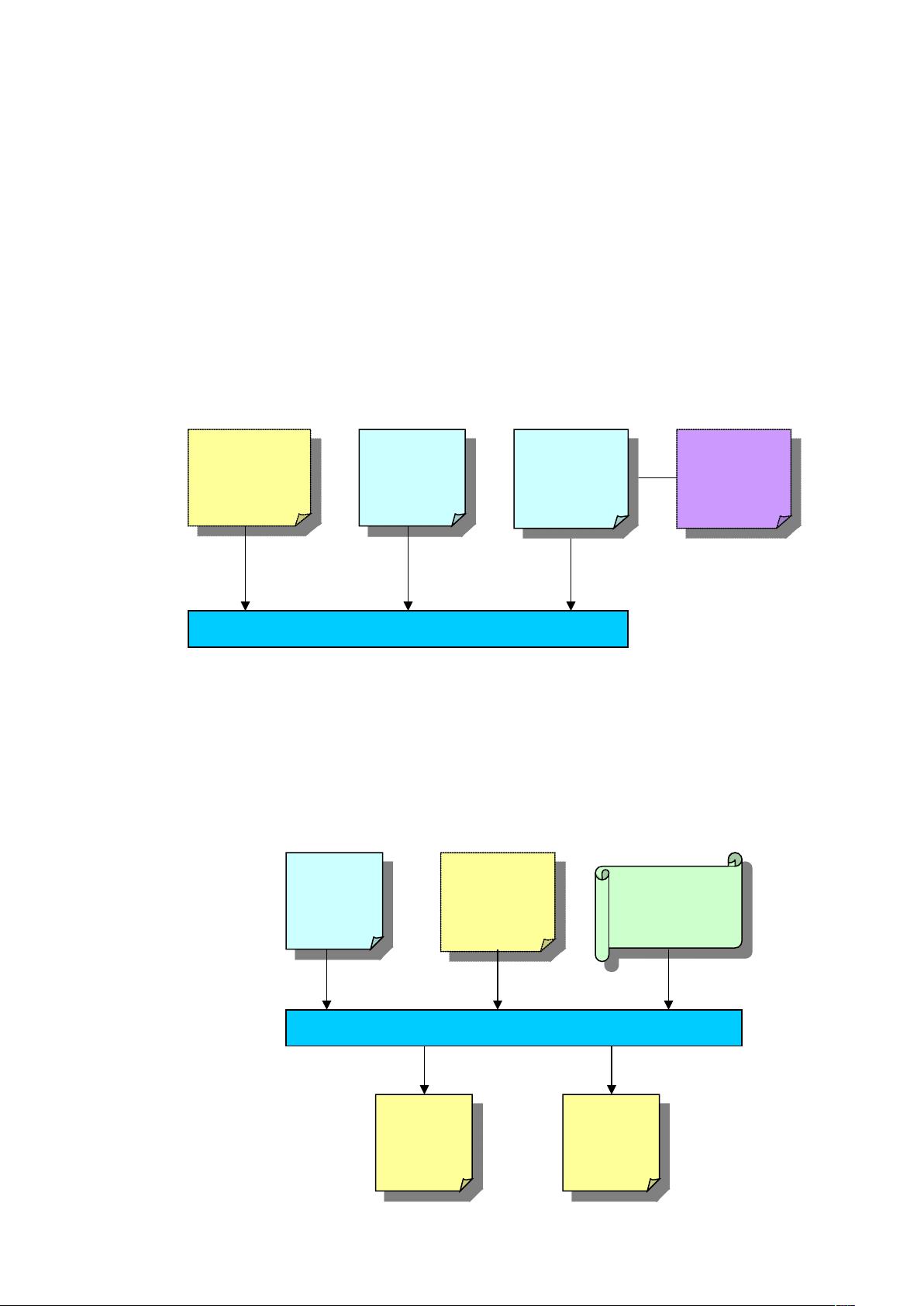

1.1 设计流程图

设计流程涵盖了从概念到实现的各个阶段,包括需求分析、功能定义、HDL编码、功能仿真、逻辑综合、布局布线、时序仿真和硬件验证。

1.2 关键步骤的实现

1.2.1 功能仿真

功能仿真使用像Modelsim这样的工具,验证设计的逻辑功能是否符合预期,这一步骤基于行为级描述(RTL)进行。

1.2.2 逻辑综合

逻辑综合是将HDL代码转换成门级网表的过程,LeonardoSpectrum等工具可以完成这项任务。综合时应考虑设计的规模和性能要求。

1.2.3 前仿真

前仿真,也称为门级仿真,是在布局布线前进行的仿真,用于验证逻辑综合结果。

1.2.4 布局布线

布局布线是将综合后的网表映射到FPGA的具体物理结构上,Altera的QuartusII等工具可以处理这一过程。

1.2.5 后仿真(时序仿真)

后仿真验证布局布线后的设计是否满足时序要求,确保设计在实际运行速度下的正确性。

2. Verilog HDL设计

2.1 编程风格要求

良好的编程风格有助于提高代码的可读性和可维护性,包括文件组织、大小写规则、标识符命名、参数化设计、空行和空格使用、对齐与缩进、注释规范,以及借鉴C语言的编程技巧。

2.2 可综合设计

设计时需注意代码的可综合特性,避免使用不可综合的语言特性,确保代码能在综合工具下顺利转换。

2.3 设计目录

合理的项目目录结构能帮助管理和组织代码,方便团队协作。

3. 逻辑仿真

3.1 测试程序(testbench)

编写测试平台以验证模块的功能,模拟输入和检查输出。

3.2 使用预编译库

利用厂家提供的预编译库可以加速设计进程,例如Altera的LPM库。

4. 逻辑综合

4.1 逻辑综合的一些原则

理解并遵循综合工具的使用指导,比如LeonardoSpectrum的优化策略,对大规模设计的处理方法,以及认真对待工具发出的警告信息。

4.1.1 关于LeonardoSpectrum

LeonardoSpectrum是一款高效的逻辑综合工具,适用于大型设计项目。

4.1.2 大规模设计的综合

对于复杂设计,需要考虑分块策略、资源分配和优化选项。

4.1.3 必须重视工具产生的警告信息

警告可能影响设计的性能和可靠性,应尽可能消除。

在进行FPGA设计时,遵循这些规范和流程,不仅可以提升设计质量,还能确保设计在不同FPGA厂家之间以及从FPGA到ASIC的顺利移植。同时,对于新员工来说,这样的流程也有利于他们快速熟悉和适应团队的工作方式。

102 浏览量

2019-01-17 上传

2010-03-29 上传

2009-10-30 上传

2009-08-10 上传

点击了解资源详情

2024-12-13 上传

2024-12-13 上传

2024-12-13 上传

cameion2013

- 粉丝: 0

- 资源: 3

最新资源

- TypeScript组件化应用实践挑战解析

- 微信小程序药店管理系统的设计与实现

- OB2PluginSample 插件开发:依赖项管理技巧

- 图像处理技术详解与实践应用

- IML++ v.1.2a:C++现代迭代方法库更新

- 开源软件实现手机GPRS连接Linux网络

- 雷达数据解析:CSV操作提取408 ARS目标物理信息

- myStudies:探索后端开发与TypeScript实践

- Matlab源代码实现DFT的cefine程序指南

- 基于用户协作过滤的推荐系统实践入门

- 童心党史系统微信小程序设计与开发

- Salesforce Markdown工作簿:掌握技术细节指南

- 高效库存管理系统的开发与应用

- Kafka与Zeebe集成新工具:Kafka-Connect-Zeebe介绍与实践

- LiteLoaderBDS:轻量级Bedrock服务器插件加载器

- Linux环境下aarch64架构ACPI表格处理工具