FPGA实现的高精度数字频率计设计

需积分: 9 83 浏览量

更新于2024-08-02

1

收藏 207KB DOC 举报

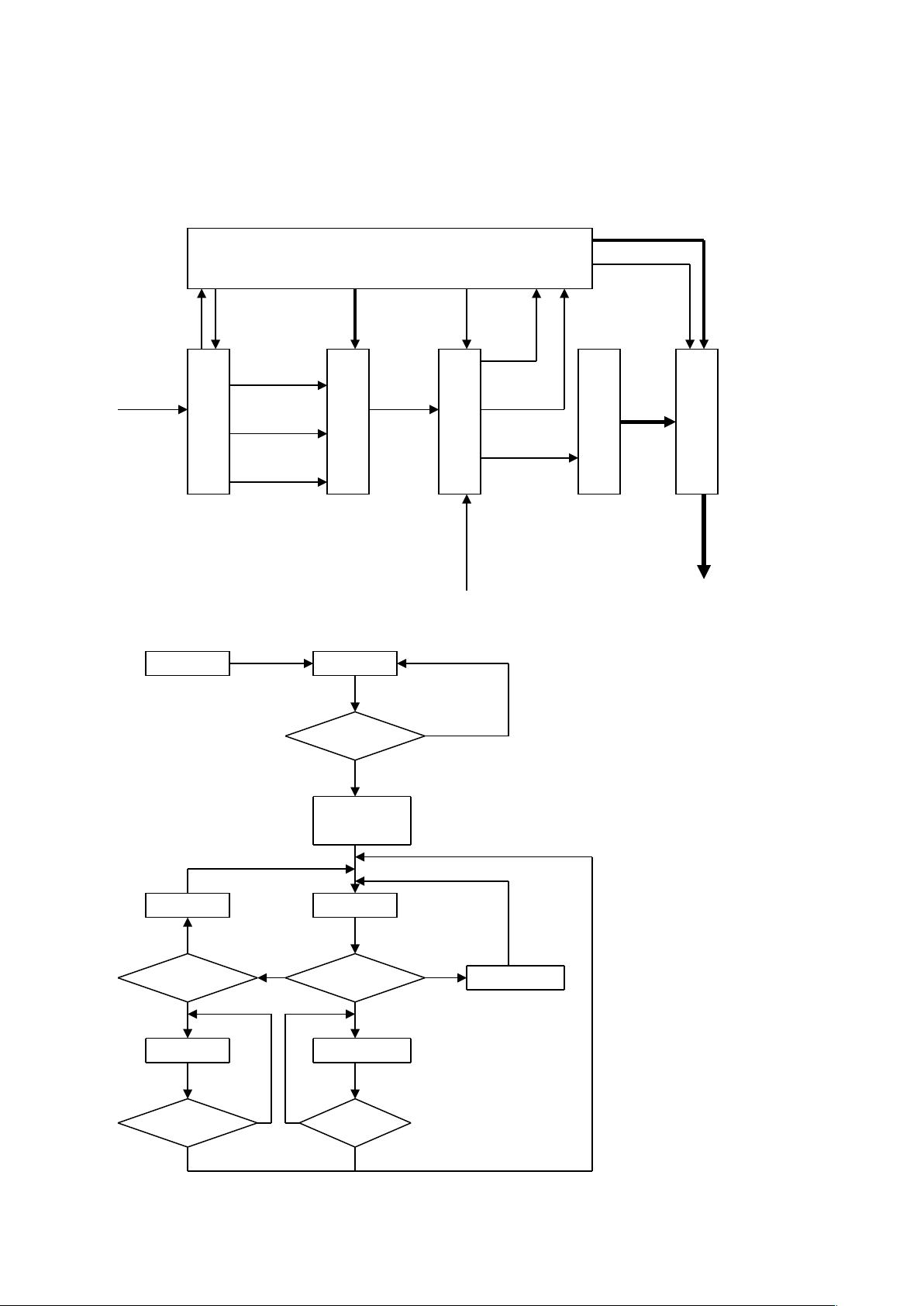

"基于FPGA的数字频率计是一种利用现代电子设计自动化技术,特别是FPGA(Field-Programmable Gate Array)技术实现的高精度、高效能电子测量设备。该设计涉及到了VHDL硬件描述语言,用于描述系统的结构、功能和接口。数字频率计的核心功能在于测量和显示信号的频率,通过分频器产生标准门控信号,计数器统计脉冲数,以及控制器进行同步控制以确保精确测量。设计要求包括宽广的测量范围(1HZ到1MHz,分三档量程),适应不同电压的输入信号,以及可调节的闸门时间,以优化测量精度。"

正文:

在当前的电子科技领域,FPGA因其可编程性和灵活性成为系统设计的重要选择。FPGA允许工程师在系统层面进行设计,通过VHDL或Verilog HDL等硬件描述语言描述系统行为,然后通过逻辑综合工具生成底层的逻辑电路,实现了自顶向下设计方法,大大缩短了设计周期并提高了设计效率。

数字频率计作为一种关键的电子测量工具,其工作原理基于在预设的时间段内统计待测信号的脉冲数量,以此计算频率。设计中,分频器生成固定时间间隔的门控信号,计数器则在这个时间段内记录脉冲数。控制器负责选择合适的门控信号,并同步控制计数器的启动与停止,确保测量的准确性和一致性。此外,为了适应不同频率的信号,数字频率计通常设有多个量程,例如10kHz、100kHz和1MHz,每个量程对应不同的最大读数,以覆盖广泛的测量需求。

设计要求方面,数字频率计需要能够处理3到5V的输入信号电压,以兼容常见的电子设备。闸门时间的设定,如0.1s、0.01s和0.001s,是为了在不同频率下提供最佳的分辨率,确保测量的精度。同时,考虑脉冲波形的峰值,设计需确保在这些参数范围内稳定工作,提高测量的可靠性。

基于FPGA的实现,使得数字频率计可以实现更高的集成度,降低系统体积,减少成本,同时提高测量速度和系统稳定性。由于FPGA的并行处理能力,它可以快速处理大量数据,从而在高频测量中表现出色。在实际应用中,这种基于FPGA的数字频率计广泛应用于实验室测试、科研项目、工业自动化等领域,为精确测量和故障排查提供了强大的工具。

2011-11-24 上传

2020-07-12 上传

2008-10-16 上传

2013-03-03 上传

2008-11-30 上传

2021-10-03 上传

2023-05-24 上传

2023-06-01 上传

2022-07-13 上传

匿名小跟班

- 粉丝: 1

- 资源: 17

最新资源

- Java集合ArrayList实现字符串管理及效果展示

- 实现2D3D相机拾取射线的关键技术

- LiveLy-公寓管理门户:创新体验与技术实现

- 易语言打造的快捷禁止程序运行小工具

- Microgateway核心:实现配置和插件的主端口转发

- 掌握Java基本操作:增删查改入门代码详解

- Apache Tomcat 7.0.109 Windows版下载指南

- Qt实现文件系统浏览器界面设计与功能开发

- ReactJS新手实验:搭建与运行教程

- 探索生成艺术:几个月创意Processing实验

- Django框架下Cisco IOx平台实战开发案例源码解析

- 在Linux环境下配置Java版VTK开发环境

- 29街网上城市公司网站系统v1.0:企业建站全面解决方案

- WordPress CMB2插件的Suggest字段类型使用教程

- TCP协议实现的Java桌面聊天客户端应用

- ANR-WatchDog: 检测Android应用无响应并报告异常