DC综合详解:ASIC设计的关键

"DC概论全总结_ASIC必备"

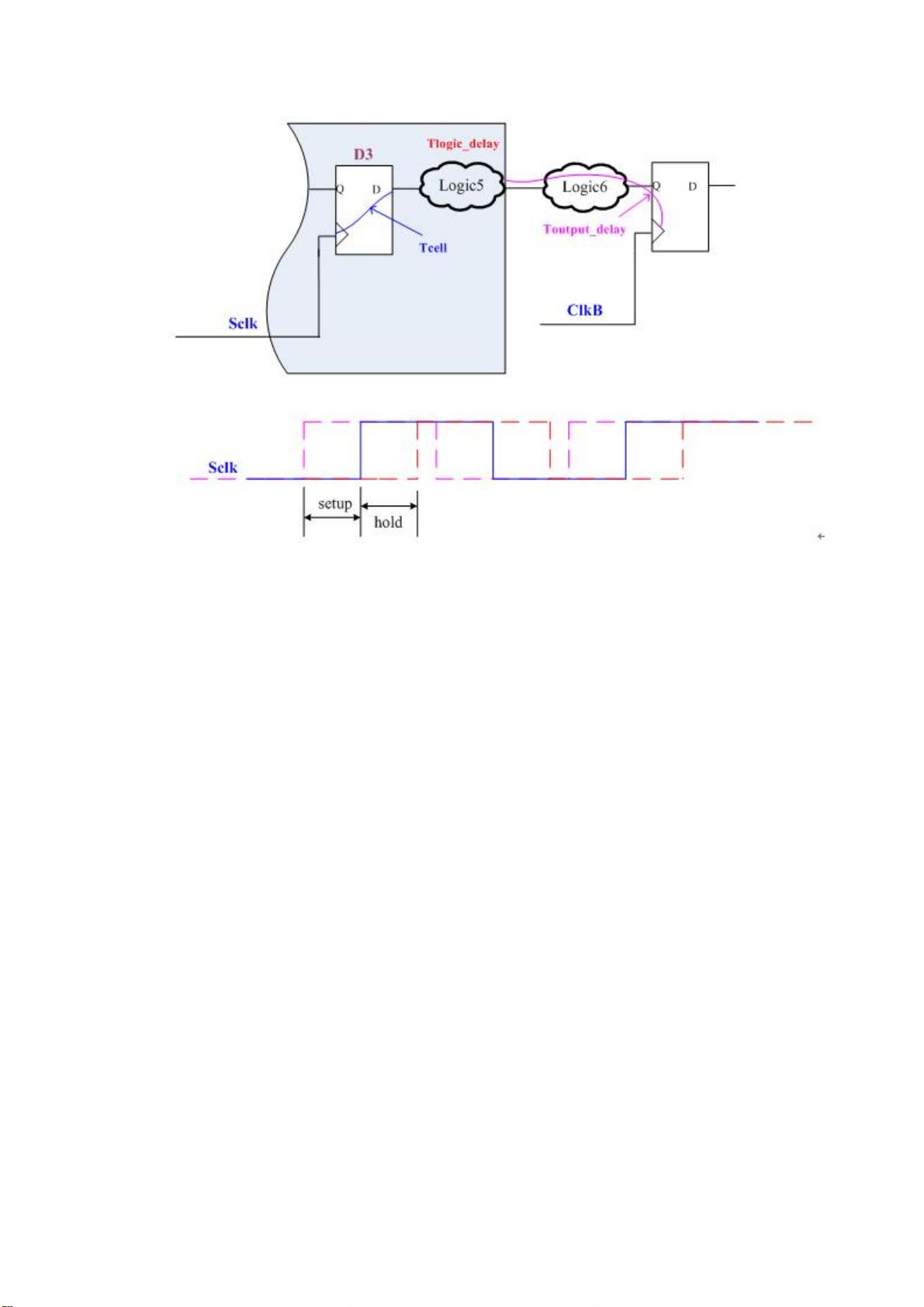

这篇文档是关于集成电路设计中的DC(Design Compiler)工具的全面概述,特别关注了时序分析的关键概念,如setup time(建立时间)和hold time(保持时间),这对于ASIC设计至关重要。DC是Synopsys公司的一款综合工具,用于将高级语言描述的数字电路转换成门级网表,同时优化性能、面积和时序。

1. **Setuptime与Holdtime**:

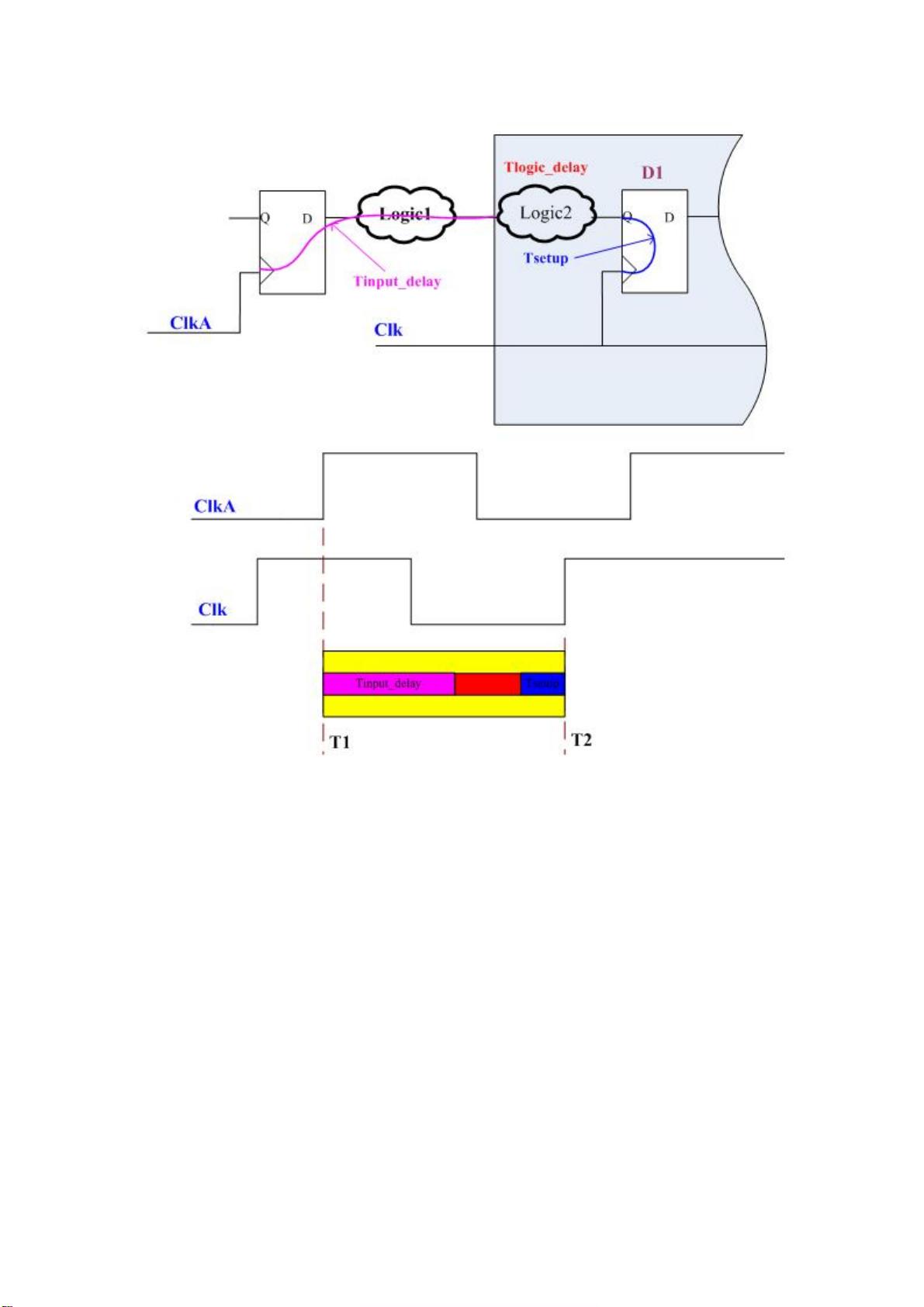

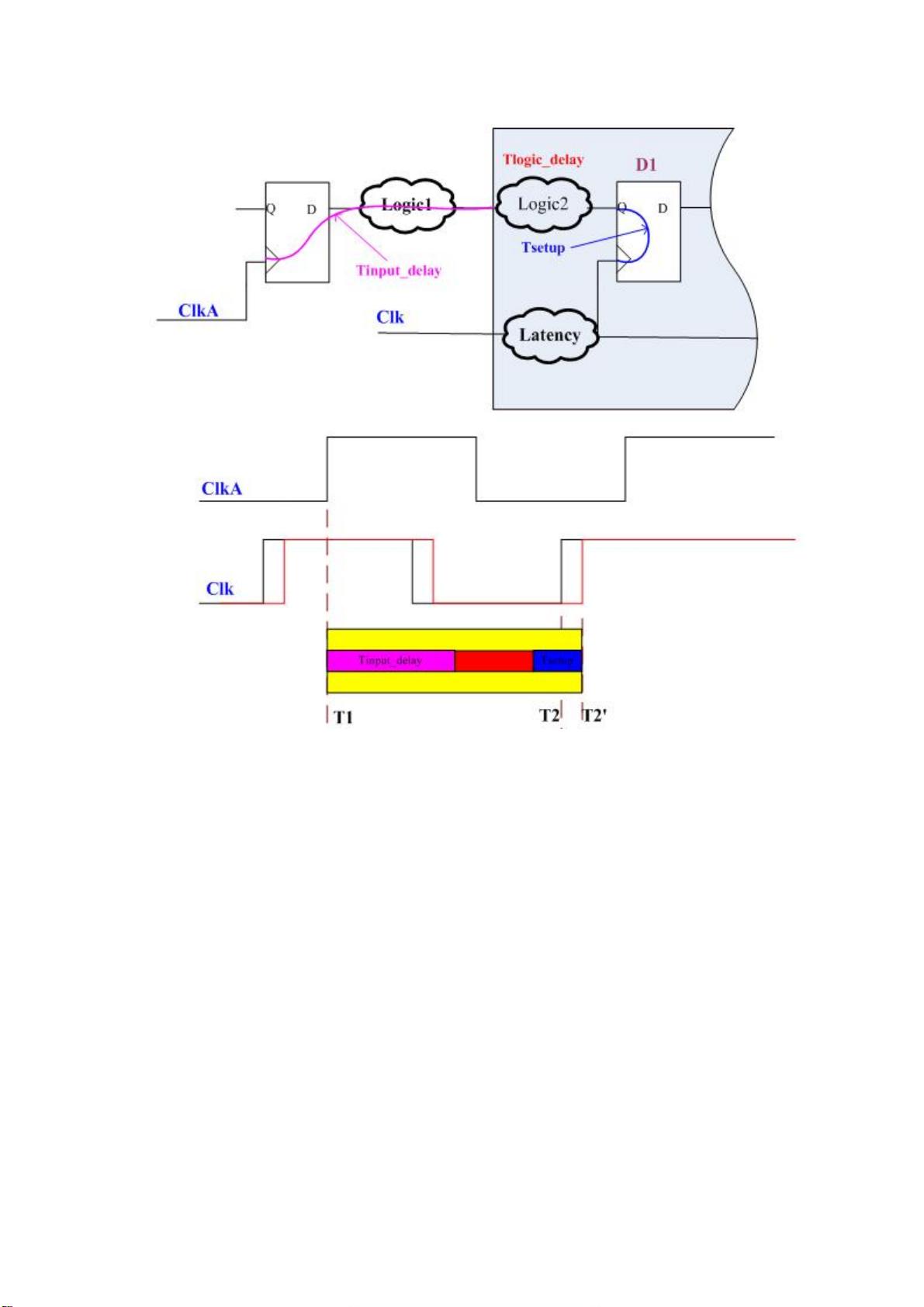

- **建立时间(setuptime)**: 数据必须在时钟沿到来前稳定,确保在时钟边沿处正确捕获数据。这是保证数字系统正确工作的一个基本条件,因为触发器会在时钟边沿采样数据。

- **保持时间(holdtime)**: 在时钟边沿后,数据必须保持稳定,以确保数据在后续阶段仍然可被正确读取。保持时间是对数据稳定性的另一个关键要求。

2. **Fanout与Skew**:

- **Fanout**: 是指一个逻辑门的输出连接到多少个其他门的输入。高扇出可能导致信号延迟增加,因为一个门的输出需要驱动多个门的输入,可能会导致信号质量下降。

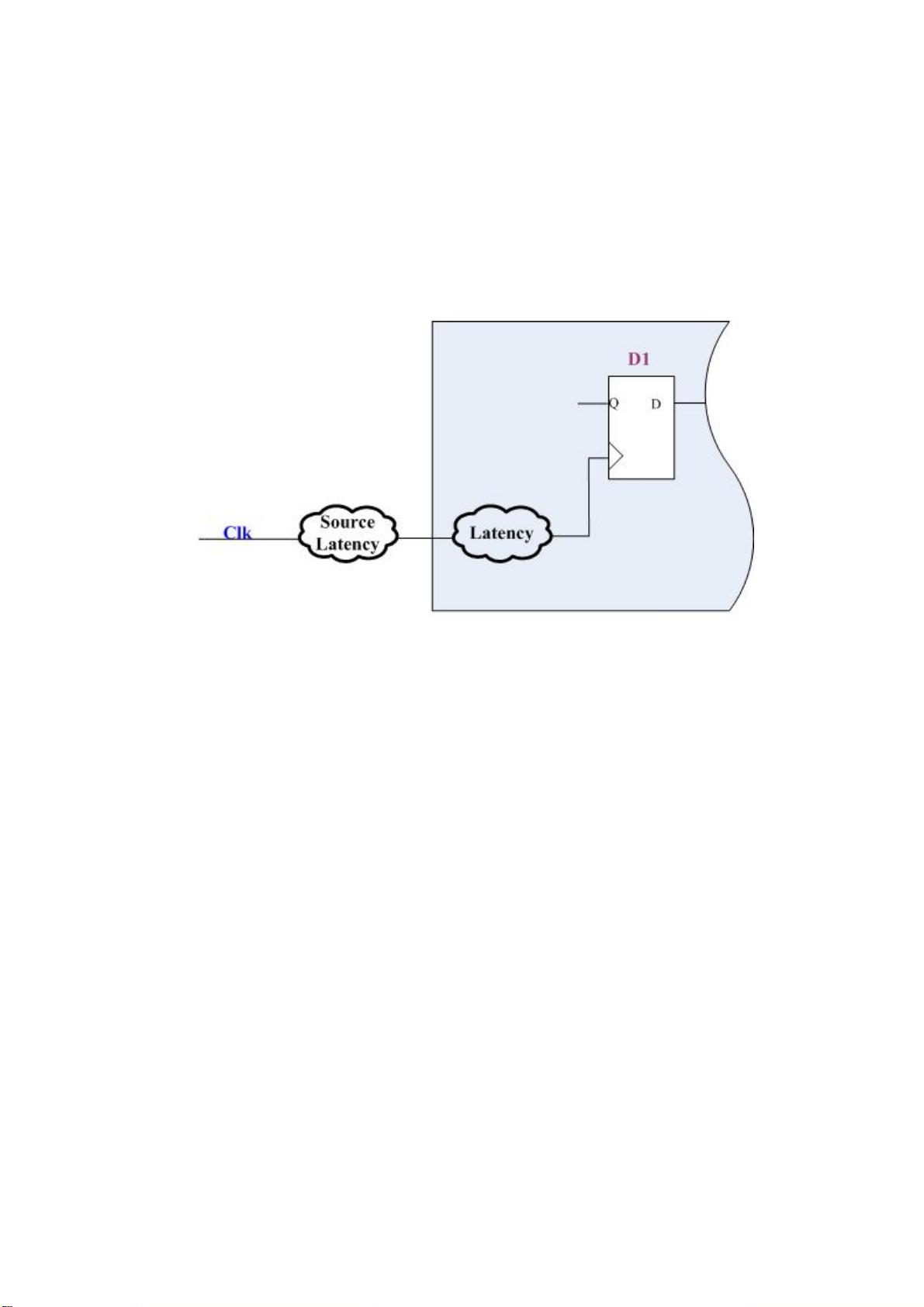

- **Skew**: 指的是时钟信号在不同路径上的传播延迟差异,这可能导致不同的逻辑单元在同一时钟周期内以不同的时间点启动操作,影响系统时序。

3. **High Fanout**:

高扇出情况通常需要更强大的驱动能力来保证信号的完整性和速度,这可能会影响设计的功耗和面积。

4. **Multicycle Path**:

多周期路径是指允许在多个时钟周期内完成的数据传输路径。在某些设计中,不是所有路径都需要满足严格的单周期时序约束,因此可以设置多周期路径来放宽特定路径的时序要求。

5. **Gated Clock**:

门控时钟是一种时钟管理技术,通过使用额外的逻辑来控制时钟信号的开启和关闭,以降低功耗或改善时序。这可以是基于条件的时钟启用,例如仅在需要时才激活某些部分的时钟。

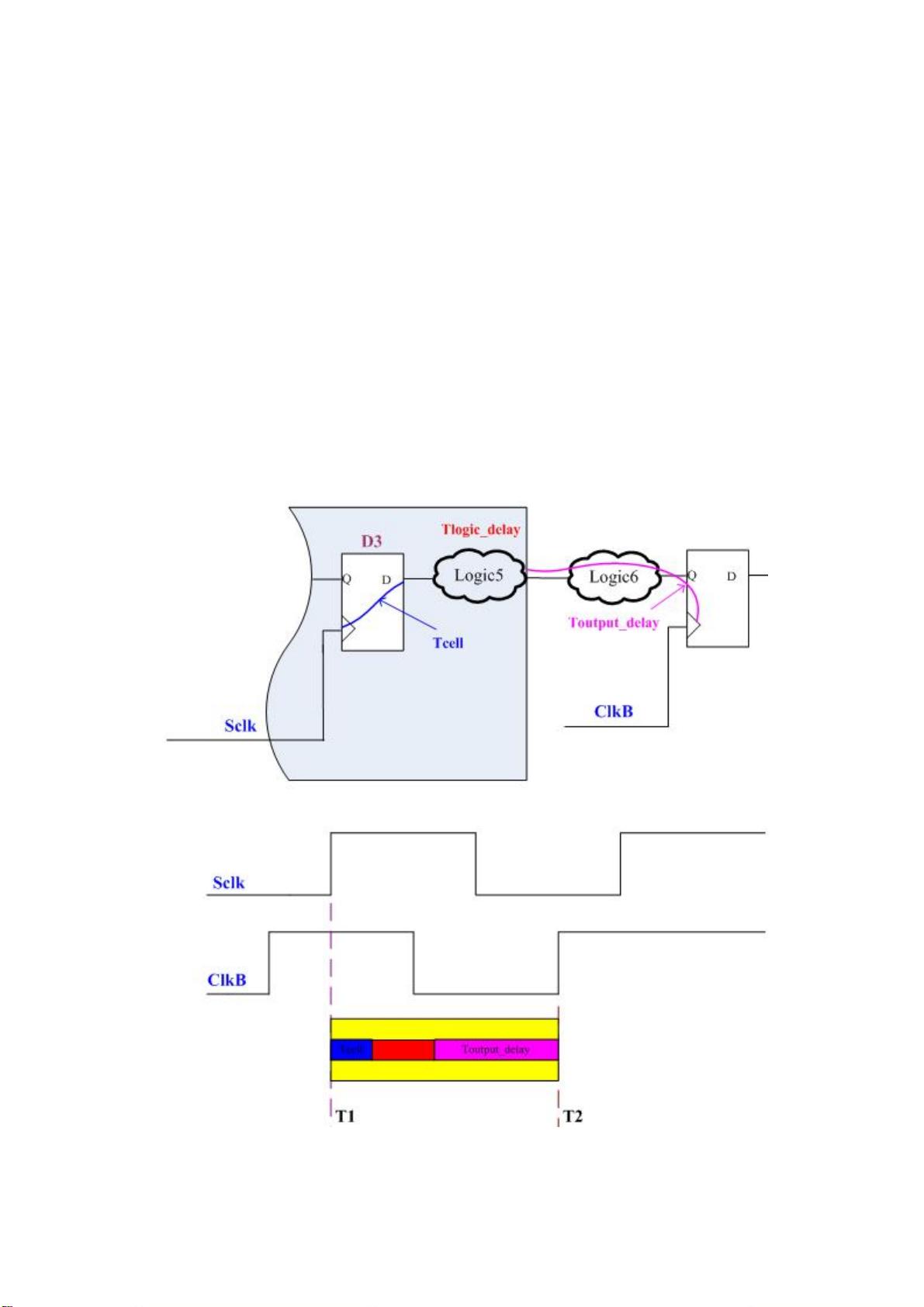

6. **IO约束**:

IO约束涉及输入/输出接口的定义,包括电源电压、信号摆幅、驱动电流和时序要求,这些都是确保芯片与外部系统正确通信的关键。

7. **DC优化约束**:

DC工具使用用户提供的约束来优化设计,这些约束可以是时序、功耗、面积或其它设计指标。优化过程涉及到器件选择、逻辑等效替换、布线调整等多个步骤,以实现最佳设计性能。

理解这些基本概念和DC工具的操作方式对于进行有效的 ASIC 设计和时序分析至关重要。设计师需要根据具体应用需求来设置和管理这些参数,以确保最终的集成电路能够满足性能、功耗和可靠性目标。通过DC的综合过程,可以实现逻辑优化并生成满足时序约束的网表,为后续的布局和布线阶段提供基础。

2020-10-20 上传

198 浏览量

2022-09-14 上传

2022-09-21 上传

2022-09-24 上传

2022-07-15 上传

2022-07-14 上传

AHU_XYF

- 粉丝: 3

- 资源: 3

最新资源

- 深入浅出:自定义 Grunt 任务的实践指南

- 网络物理突变工具的多点路径规划实现与分析

- multifeed: 实现多作者间的超核心共享与同步技术

- C++商品交易系统实习项目详细要求

- macOS系统Python模块whl包安装教程

- 掌握fullstackJS:构建React框架与快速开发应用

- React-Purify: 实现React组件纯净方法的工具介绍

- deck.js:构建现代HTML演示的JavaScript库

- nunn:现代C++17实现的机器学习库开源项目

- Python安装包 Acquisition-4.12-cp35-cp35m-win_amd64.whl.zip 使用说明

- Amaranthus-tuberculatus基因组分析脚本集

- Ubuntu 12.04下Realtek RTL8821AE驱动的向后移植指南

- 掌握Jest环境下的最新jsdom功能

- CAGI Toolkit:开源Asterisk PBX的AGI应用开发

- MyDropDemo: 体验QGraphicsView的拖放功能

- 远程FPGA平台上的Quartus II17.1 LCD色块闪烁现象解析