没有合适的资源?快使用搜索试试~ 我知道了~

首页ADSP-BF609 Blackfin Dual-Core 处理器规格详解

ADSP-BF609 Blackfin Dual-Core 处理器规格详解

"ADSP-BF609是Analog Devices公司的一款双核高性能嵌入式处理器,属于Blackfin系列。该处理器在每个核心上可达到500MHz的时钟频率,具有两个16位乘法累加器(MACs)、两个40位算术逻辑单元(ALUs)以及一个40位移位寄存器。其设计采用类似精简指令集计算(RISC)的寄存器和指令模型,便于编程并支持编译器优化。此外,ADSP-BF609还提供了高级调试、追踪和性能分析功能。尽管文档中未详尽列出所有特性,但可以推测这款处理器旨在满足高效能、低功耗的嵌入式应用需求。"

ADSP-BF609是Analog Devices公司的Blackfin系列中的高端产品之一,它集成了两个高性能的核心,每个核心都具备强大的处理能力。每个核心不仅有16位MACs用于高效的数字信号处理运算,还有40位ALUs以处理更复杂的计算任务,以及40位的移位寄存器,这使得ADSP-BF609在数据处理和算法执行方面表现出色。

在软件开发方面,ADSP-BF609采用RISC-like的架构,意味着它拥有简洁的指令集和寄存器布局,简化了编程工作,同时对编译器友好,有助于提高代码效率。这对于需要编写复杂算法和实时操作的嵌入式系统来说尤其重要,因为它可以减少开发时间和复杂性。

文档中提及的高级调试、追踪和性能分析功能对于开发者来说是极其宝贵的工具。这些功能可以帮助开发者深入理解程序运行过程,找出潜在的性能瓶颈,进行调优,确保系统的稳定性和效率。

由于ADSP-BF609是针对嵌入式应用设计的,我们可以推断它可能广泛应用于图像处理、音频视频编码解码、通信基础设施、工业自动化、汽车电子等多个领域。尽管Analog Devices不对使用其产品可能导致的专利侵权或其他第三方权利侵犯承担责任,但他们确实在提供准确和可靠的信息,同时也强调规格可能会随时更新,而不会自动授予任何专利使用权。

总体而言,ADSP-BF609是一款专为需要强大计算能力和高效能的嵌入式系统设计的处理器,其强大的硬件性能结合友好的软件开发环境,使其成为高要求应用的理想选择。对于寻求高性能、低功耗解决方案的工程师来说,ADSP-BF609无疑是值得考虑的平台。

Rev. A | Page 16 of 112 | February 2014

ADSP-BF606/ADSP-BF607/ADSP-BF608/ADSP-BF609

Power Management

As shown in Table 4, the processor supports five different power

domains, which maximizes flexibility while maintaining com-

pliance with industry standards and conventions. There are no

sequencing requirements for the various power domains, but all

domains must be powered according to the appropriate Specifi-

cations table for processor operating conditions; even if the

feature/peripheral is not used.

The dynamic power management feature of the processor

allows the processor’s core clock frequency (f

CCLK

) to be dynam-

ically controlled.

The power dissipated by a processor is largely a function of its

clock frequency and the square of the operating voltage. For

example, reducing the clock frequency by 25% results in a 25%

reduction in dynamic power dissipation.

Full-On Operating Mode—Maximum Performance

In the full-on mode, the PLL is enabled and is not bypassed,

providing capability for maximum operational frequency. This

is the power-up default execution state in which maximum per-

formance can be achieved. The processor cores and all enabled

peripherals run at full speed.

Active Operating Mode—Moderate Dynamic Power Savings

In the active mode, the PLL is enabled but bypassed. Because the

PLL is bypassed, the processor’s core clocks and system clocks

run at the input clock (SYS_CLKIN) frequency. DMA access is

available to appropriately configured L1 memories.

For more information about PLL controls, see the “Dynamic

Power Management” chapter in the ADSP-BF60x Blackfin Pro-

cessor Hardware Reference.

See Table 5 for a summary of the power settings for each mode.

Deep Sleep Operating Mode—Maximum Dynamic Power

Savings

The deep sleep mode maximizes dynamic power savings by dis-

abling the clocks to the processor core and to all synchronous

peripherals. Asynchronous peripherals may still be running but

cannot access internal resources or external memory.

Hibernate State—Maximum Static Power Savings

The hibernate state maximizes static power savings by disabling

the voltage and clocks to the processor cores and to all of the

peripherals. This setting signals the external voltage regulator

supplying the V

DD_INT

pins to shut off using the SYS_

EXTWAKE signal, which provides the lowest static power dissi-

pation. Any critical information stored internally (for example,

memory contents, register contents, and other information)

must be written to a non-volatile storage device prior to remov-

ing power if the processor state is to be preserved.

Since the V

DD_EXT

pins can still be supplied in this mode, all of

the external pins three-state, unless otherwise specified. This

allows other devices that may be connected to the processor to

still have power applied without drawing unwanted current.

Reset Control Unit

Reset is the initial state of the whole processor or one of the

cores and is the result of a hardware or software triggered event.

In this state, all control registers are set to their default values

and functional units are idle. Exiting a full system reset starts

with Core-0 only being ready to boot. Exiting a Core-n only

reset starts with this Core-n being ready to boot.

The Reset Control Unit (RCU) controls how all the functional

units enter and exit reset. Differences in functional require-

ments and clocking constraints define how reset signals are

generated. Programs must guarantee that none of the reset

functions puts the system into an undefined state or causes

resources to stall. This is particularly important when only one

of the cores is reset (programs must ensure that there is no

pending system activity involving the core that is being reset).

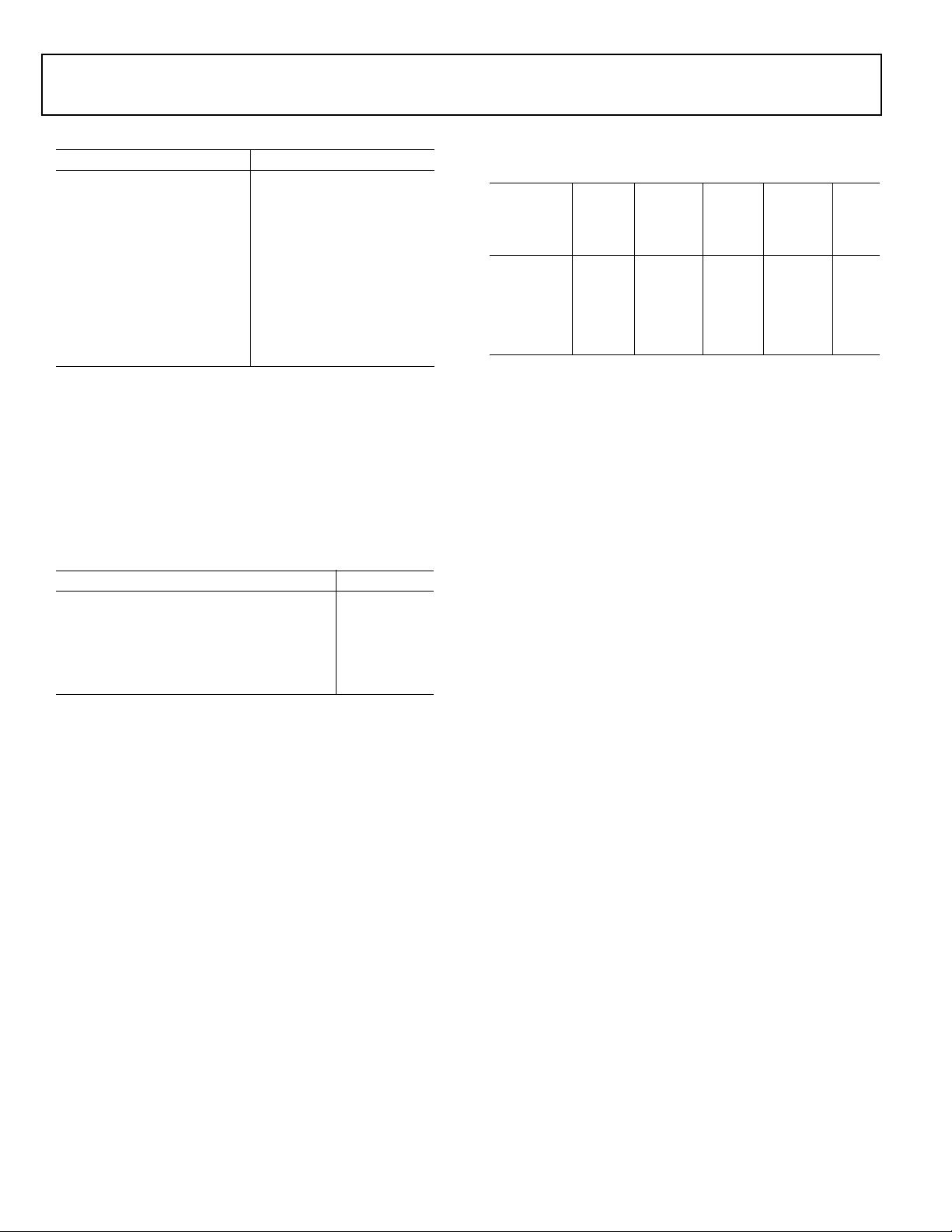

Table 3. Clock Dividers

Clock Source Divider

CCLK (core clock) By 4

SYSCLK (System clock) By 2

SCLK0 (system clock for PVP, all

peripherals not covered by

SCLK1)

None

SCLK1 (system clock for SPORTS,

SPI, ACM)

None

DCLK (LPDDR/DDR2 clock) By 2

OCLK (output clock) Programmable

CLKBUF None, direct from SYS_CLKIN

Table 4. Power Domains

Power Domain V

DD

Range

All internal logic V

DD_INT

DDR2/LPDDR V

DD_DMC

USB V

DD_USB

Thermal diode V

DD_TD

All other I/O (includes SYS, JTAG, and Ports pins) V

DD_EXT

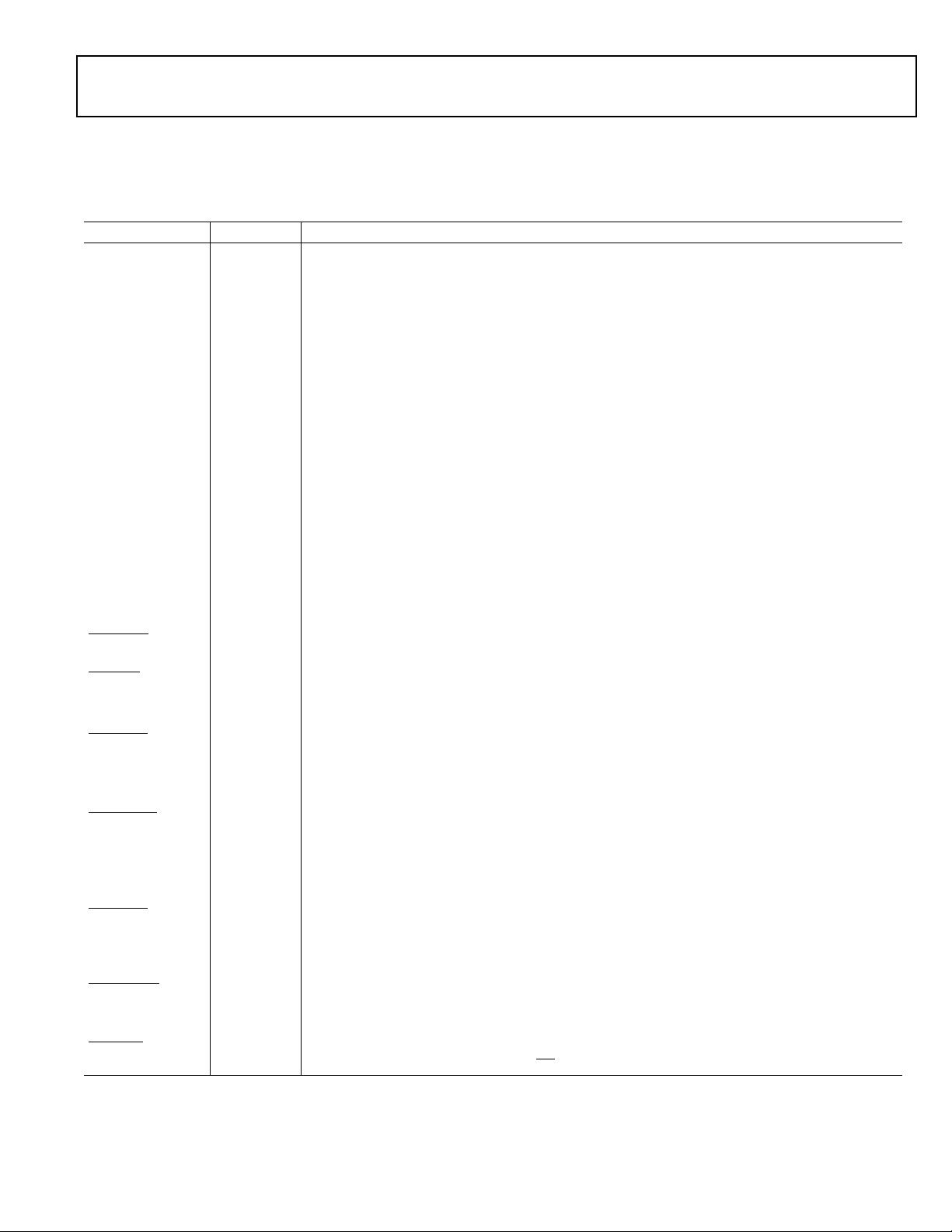

Table 5. Power Settings

Mode/State PLL

PLL

Bypassed f

CCLK

f

SYSCLK

,

f

DCLK

,

f

SCLK0

,

f

SCLK1

Core

Power

Full On Enabled No Enabled Enabled On

Active Enabled/

Disabled

Yes Enabled Enabled On

Deep Sleep Disabled — Disabled Disabled On

Hibernate Disabled — Disabled Disabled Off

Rev. A | Page 17 of 112 | February 2014

ADSP-BF606/ADSP-BF607/ADSP-BF608/ADSP-BF609

From a system perspective reset is defined by both the reset tar-

get and the reset source as described below.

Target defined:

• Hardware Reset – All functional units are set to their

default states without exception. History is lost.

• System Reset – All functional units except the RCU are set

to their default states.

• Core-n only Reset – Affects Core-n only. The system soft-

ware should guarantee that the core in reset state is not

accessed by any bus master.

Source defined:

• Hardware Reset – The SYS_HWRST

input signal is

asserted active (pulled down).

• System Reset – May be triggered by software (writing to the

RCU_CTL register) or by another functional unit such as

the dynamic power management (DPM) unit (Hibernate)

or any of the system event controller (SEC), trigger routing

unit (TRU), or emulator inputs.

• Core-n-only reset – Triggered by software.

• Trigger request (peripheral).

Voltage Regulation

The processor requires an external voltage regulator to power

the V

DD_INT

pins. To reduce standby power consumption, the

external voltage regulator can be signaled through SYS_

EXTWAKE to remove power from the processor core. This sig-

nal is high-true for power-up and may be connected directly to

the low-true shut-down input of many common regulators.

While in the hibernate state, all external supply pins (V

DD_EXT

,

V

DD_USB

, V

DD_DMC

) can still be powered, eliminating the need for

external buffers. The external voltage regulator can be activated

from this power down state by asserting the SYS_HWRST

pin,

which then initiates a boot sequence. SYS_EXTWAKE indicates

a wakeup to the external voltage regulator.

SYSTEM DEBUG

The processor includes various features that allow for easy sys-

tem debug. These are described in the following sections.

System Watchpoint Unit

The System Watchpoint Unit (SWU) is a single module which

connects to a single system bus and provides for transaction

monitoring. One SWU is attached to the bus going to each sys-

tem slave. The SWU provides ports for all system bus address

channel signals. Each SWU contains four match groups of regis-

ters with associated hardware. These four SWU match groups

operate independently, but share common event (interrupt,

trigger and others) outputs.

System Debug Unit

The System Debug Unit (SDU) provides IEEE-1149.1 support

through its JTAG interface. In addition to traditional JTAG fea-

tures, present in legacy Blackfin products, the SDU adds more

features for debugging the chip without halting the core

processors.

DEVELOPMENT TOOLS

Analog Devices supports its processors with a complete line of

software and hardware development tools, including integrated

development environments (which include CrossCore

®

Embed-

ded Studio and/or VisualDSP++

®

), evaluation products,

emulators, and a wide variety of software add-ins.

Integrated Development Environments (IDEs)

For C/C++ software writing and editing, code generation, and

debug support, Analog Devices offers two IDEs.

The newest IDE, CrossCore Embedded Studio, is based on the

Eclipse

TM

framework. Supporting most Analog Devices proces-

sor families, it is the IDE of choice for future processors,

including multicore devices. CrossCore Embedded Studio

seamlessly integrates available software add-ins to support real

time operating systems, file systems, TCP/IP stacks, USB stacks,

algorithmic software modules, and evaluation hardware board

support packages. For more information visit

www.analog.com/cces.

The other Analog Devices IDE, VisualDSP++, supports proces-

sor families introduced prior to the release of CrossCore

Embedded Studio. This IDE includes the Analog Devices VDK

real time operating system and an open source TCP/IP stack.

For more information visit www.analog.com/visualdsp. Note

that VisualDSP++ will not support future Analog Devices

processors.

EZ-KIT Lite Evaluation Board

For processor evaluation, Analog Devices provides wide range

of EZ-KIT Lite

®

evaluation boards. Including the processor and

key peripherals, the evaluation board also supports on-chip

emulation capabilities and other evaluation and development

features. Also available are various EZ-Extenders

®

, which are

daughter cards delivering additional specialized functionality,

including audio and video processing. For more information

visit www.analog.com and search on “ezkit” or “ezextender”.

EZ-KIT Lite Evaluation Kits

For a cost-effective way to learn more about developing with

Analog Devices processors, Analog Devices offer a range of EZ-

KIT Lite evaluation kits. Each evaluation kit includes an EZ-KIT

Lite evaluation board, directions for downloading an evaluation

version of the available IDE(s), a USB cable, and a power supply.

The USB controller on the EZ-KIT Lite board connects to the

USB port of the user’s PC, enabling the chosen IDE evaluation

suite to emulate the on-board processor in-circuit. This permits

the customer to download, execute, and debug programs for the

EZ-KIT Lite system. It also supports in-circuit programming of

the on-board Flash device to store user-specific boot code,

enabling standalone operation. With the full version of

Rev. A | Page 18 of 112 | February 2014

ADSP-BF606/ADSP-BF607/ADSP-BF608/ADSP-BF609

CrossCore Embedded Studio or VisualDSP++ installed (sold

separately), engineers can develop software for supported EZ-

KITs or any custom system utilizing supported Analog Devices

processors.

Software Add-Ins for CrossCore Embedded Studio

Analog Devices offers software add-ins which seamlessly inte-

grate with CrossCore Embedded Studio to extend its capabilities

and reduce development time. Add-ins include board support

packages for evaluation hardware, various middleware pack-

ages, and algorithmic modules. Documentation, help,

configuration dialogs, and coding examples present in these

add-ins are viewable through the CrossCore Embedded Studio

IDE once the add-in is installed.

Board Support Packages for Evaluation Hardware

Software support for the EZ-KIT Lite evaluation boards and EZ-

Extender daughter cards is provided by software add-ins called

Board Support Packages (BSPs). The BSPs contain the required

drivers, pertinent release notes, and select example code for the

given evaluation hardware. A download link for a specific BSP is

located on the web page for the associated EZ-KIT or EZ-

Extender product. The link is found in the Product Download

area of the product web page.

Middleware Packages

Analog Devices separately offers middleware add-ins such as

real time operating systems, file systems, USB stacks, and

TCP/IP stacks. For more information see the following web

pages:

• www.analog.com/ucos3

• www.analog.com/ucfs

• www.analog.com/ucusbd

• www.analog.com/lwip

Algorithmic Modules

To speed development, Analog Devices offers add-ins that per-

form popular audio and video processing algorithms. These are

available for use with both CrossCore Embedded Studio and

VisualDSP++. For more information visit www.analog.com and

search on “Blackfin software modules”.

Designing an Emulator-Compatible DSP Board (Target)

For embedded system test and debug, Analog Devices provides

a family of emulators. On each JTAG DSP, Analog Devices sup-

plies an IEEE 1149.1 JTAG Test Access Port (TAP). In-circuit

emulation is facilitated by use of this JTAG interface. The emu-

lator accesses the processor’s internal features via the

processor’s TAP, allowing the developer to load code, set break-

points, and view variables, memory, and registers. The

processor must be halted to send data and commands, but once

an operation is completed by the emulator, the DSP system is set

to run at full speed with no impact on system timing. The emu-

lators require the target board to include a header that supports

connection of the DSP’s JTAG port to the emulator.

For details on target board design issues including mechanical

layout, single processor connections, signal buffering, signal ter-

mination, and emulator pod logic, see the EE-68: Analog Devices

JTAG Emulation Technical Reference on the Analog Devices

website (www.analog.com)—use site search on “EE-68.” This

document is updated regularly to keep pace with improvements

to emulator support.

ADDITIONAL INFORMATION

The following publications that describe the ADSP-BF606/

ADSP-BF607/ADSP-BF608/ADSP-BF609 processors (and

related processors) can be ordered from any Analog Devices

sales office or accessed electronically on our website:

• Getting Started With Blackfin Processors

• ADSP-BF60x Blackfin Processor Hardware Reference

• Blackfin Processor Programming Reference

• ADSP-BF60x Blackfin Processor Anomaly List

RELATED SIGNAL CHAINS

A signal chain is a series of signal-conditioning electronic com-

ponents that receive input (data acquired from sampling either

real-time phenomena or from stored data) in tandem, with the

output of one portion of the chain supplying input to the next.

Signal chains are often used in signal processing applications to

gather and process data or to apply system controls based on

analysis of real-time phenomena. For more information about

this term and related topics, see the “signal chain” entry in the

Glossary of EE Terms on the Analog Devices website.

Analog Devices eases signal processing system development by

providing signal processing components that are designed to

work together well. A tool for viewing relationships between

specific applications and related components is available on the

www.analog.com website.

The Application Signal Chains page in the Circuits from the

Lab

TM

site (http:\\www.analog.com\circuits) provides:

• Graphical circuit block diagram presentation of signal

chains for a variety of circuit types and applications

• Drill down links for components in each chain to selection

guides and application information

• Reference designs applying best practice design techniques

Rev. A | Page 19 of 112 | February 2014

ADSP-BF606/ADSP-BF607/ADSP-BF608/ADSP-BF609

ADSP-BF60x DETAILED SIGNAL DESCRIPTIONS

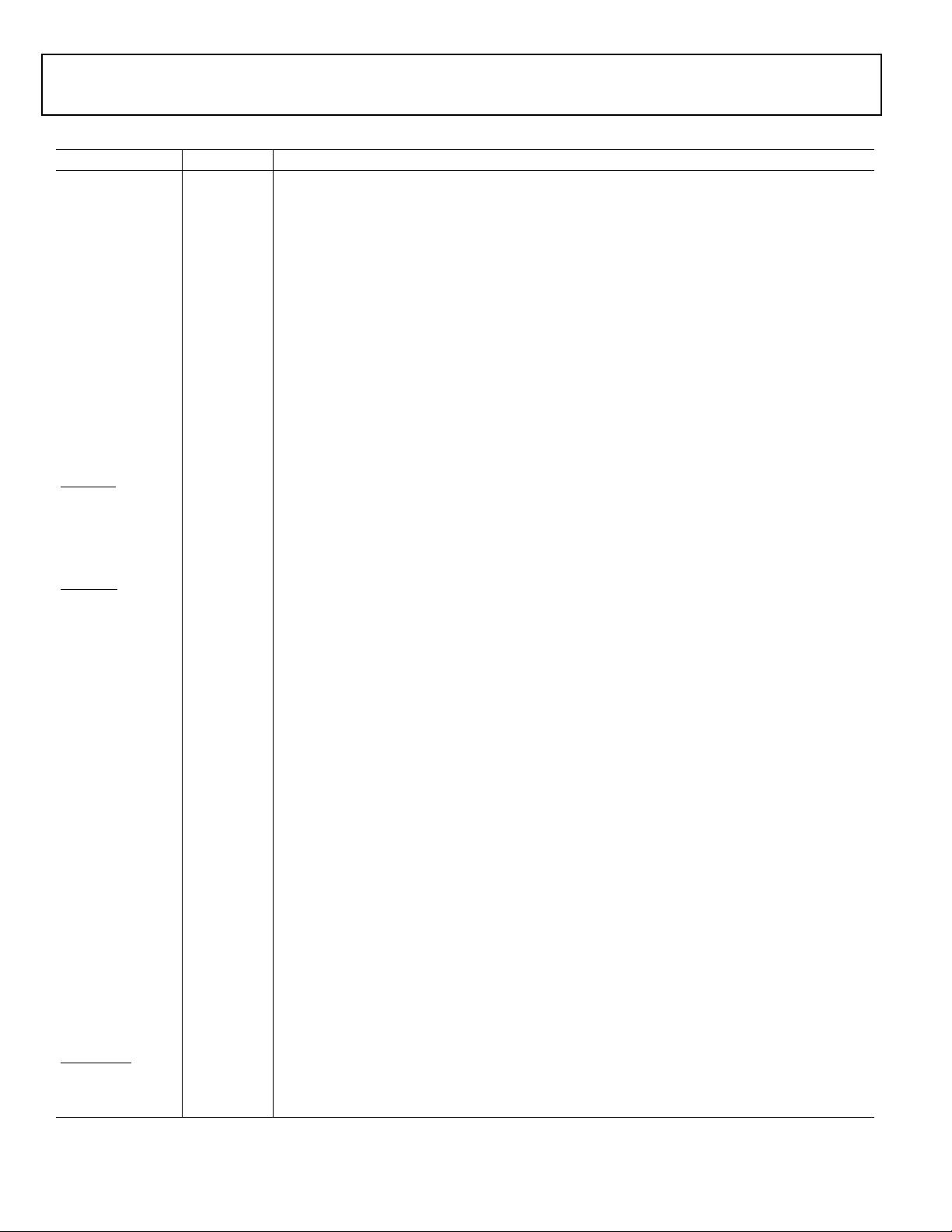

Table 6 provides a detailed description of each signal.

Table 6. Detailed Signal Descriptions

Signal Name Direction Description

ACM_An Output ADC Control Signals Function varies by mode.

ACM_CLK Output Clock SCLK derived clock for connecting to an ADC.

ACM_FS Output Frame Sync Typically used as an ADC chip select.

ACM_Tn Input External Trigger n Input for external trigger events.

CAN_RX Input Receive Typically an external CAN transceiver's RX output.

CAN_TX Output Transmit Typically an external CAN transceiver's TX input.

CNT_DG Input Count Down and Gate Depending on the mode of operation this input acts either as a count down

signal or a gate signal.

Count Down: This input causes the GP counter to decrement.

Gate: Stops the GP counter from incrementing or decrementing.

CNT_UD Input Count Up and Direction Depending on the mode of operation this input acts either as a count up signal

or a direction signal.

Count Up: This input causes the GP counter to increment.

Direction: Selects whether the GP counter is incrementing or decrementing.

CNT_ZM Input Count Zero Marker Input that connects to the zero marker output of a rotary device or detects the

pressing of a push button.

DMC_Ann Output Address n Address bus.

DMC_BAn Output Bank Address Input n Defines which internal bank an ACTIVATE, READ, WRITE, or PRECHARGE command

is being applied to on the dynamic memory. Also defines which mode registers (MR, EMR, EMR2, and/or

EMR3) are loaded during the LOAD MODE REGISTER command.

DMC_CAS

Output Column Address Strobe Defines the operation for external dynamic memory to perform in conjunction

with other DMC command signals. Connect to the CAS input of dynamic memory.

DMC_CK

Output Clock (complement) Complement of DMC_CK.

DMC_CK Output Clock Outputs DCLK to external dynamic memory.

DMC_CKE Output Clock enable Active high clock enables. Connects to the dynamic memory’s CKE input.

DMC_CSn

Output Chip Select n Commands are recognized by the memory only when this signal is asserted.

DMC_DQnn I/O Data n Bidirectional data bus.

DMC_LDM Output Data Mask for Lower Byte Mask for DMC_DQ07:DMC_DQ00 write data when driven high. Sampled on

both edges of the data strobe by the dynamic memory.

DMC_LDQS

I/O Data Strobe for Lower Byte (complement) Complement of LDQS. Not used in single-ended mode.

DMC_LDQS I/O Data Strobe for Lower Byte DMC_DQ07:DMC_DQ00 data strobe. Output with Write Data. Input with

Read Data. May be single-ended or differential depending on register settings.

DMC_ODT Output On-die Termination Enables dynamic memory termination resistances when driven high (assuming

the memory is properly configured). ODT is enabled/disabled regardless of read or write commands.

DMC_RAS

Output Row Address Strobe Defines the operation for external dynamic memory to perform in conjunction

with other DMC command signals. Connect to the RAS input of dynamic memory.

DMC_UDM Output Data Mask for Upper Byte Mask for DMC_DQ15:DMC_DQ08 write data when driven high. Sampled on

both edges of the data strobe by the dynamic memory.

DMC_UDQS

I/O Data Strobe for Upper Byte (complement) Complement of UDQS. Not used in single-ended mode.

DMC_UDQS I/O Data Strobe for Upper Byte DMC_DQ15:DMC_DQ08 data strobe. Output with Write Data. Input with

Read Data. May be single-ended or differential depending on register settings.

DMC_WE

Output Write Enable Defines the operation for external dynamic memory to perform in conjunction with other

DMC command signals. Connect to the WE

input of dynamic memory.

Rev. A | Page 20 of 112 | February 2014

ADSP-BF606/ADSP-BF607/ADSP-BF608/ADSP-BF609

ETH_CRS Input Carrier Sense/RMII Receive Data Valid Multiplexed on alternate clock cycles.

CRS: Asserted by the PHY when either the transmit or receive medium is not idle. De-asserted when both

are idle.

RXDV: Asserted by the PHY when the data on RXDn is valid.

ETH_MDC Output Management Channel Clock Clocks the MDC input of the PHY.

ETH_MDIO I/O Management Channel Serial Data Bidirectional data bus for PHY control.

ETH_PTPAUXIN Input PTP Auxiliary Trigger Input Assert this signal to take an auxiliary snapshot of the time and store it in

the auxiliary time stamp FIFO.

ETH_PTPCLKIN Input PTP Clock Input Optional external PTP clock input.

ETH_PTPPPS Output PTP Pulse-Per-Second Output When the Advanced Time Stamp feature is enabled, this signal is

asserted based on the PPS mode selected. Otherwise, PTPPPS is asserted every time the seconds counter

is incremented.

ETH_REFCLK Input Reference Clock Externally supplied Ethernet clock.

ETH_RXDn Input Receive Data n Receive data bus.

ETH_TXDn Output Transmit Data n Transmit data bus.

ETH_TXEN I/O Transmit Enable When asserted indicates that the data on TXDn is valid.

JTG_EMU

Output Emulation Output JTAG emulation flag.

JTG_TCK Input Clock JTAG test access port clock.

JTG_TDI Input Serial Data In JTAG test access port data input.

JTG_TDO Output Serial Data Out JTAG test access port data output.

JTG_TMS Input Mode Select JTAG test access port mode select.

JTG_TRST

Input Reset JTAG test access port reset.

LP_ACK I/O Acknowledge Provides handshaking. When the link port is configured as a receiver, ACK is an output.

When the link port is configured as a transmitter, ACK is an input.

LP_CLK I/O Clock When the link port is configured as a receiver, CLK is an input. When the link port is configured as

a transmitter, CLK is an output.

LP_Dn I/O Data n Data bus. Input when receiving, output when transmitting.

PPI_CLK I/O Clock Input in external clock mode, output in internal clock mode.

PPI_Dnn I/O Data n Bidirectional data bus.

PPI_FS1 I/O Frame Sync 1 (HSYNC) Behavior depends on PPI mode. See the PPI chapter in the processor hardware

reference for more details.

PPI_FS2 I/O Frame Sync 2 (VSYNC) Behavior depends on PPI mode. See the PPI chapter in the processor hardware

reference for more details.

PPI_FS3 I/O Frame Sync 3 (FIELD) Behavior depends on PPI mode. See the PPI chapter in the processor hardware

reference for more details.

PWM_AH Output Channel A High Side High side drive signal.

PWM_AL Output Channel A Low Side Low side drive signal.

PWM_BH Output Channel B High Side High side drive signal.

PWM_BL Output Channel B Low Side Low side drive signal.

PWM_CH Output Channel C High Side High side drive signal.

PWM_CL Output Channel C Low Side Low side drive signal.

PWM_DH Output Channel D High Side High side drive signal.

PWM_DL Output Channel D Low Side Low side drive signal.

PWM_SYNC Input PWM External Sync This input is for an externally generated sync signal. If the sync signal is internally

generated no connection is necessary.

PWM_TRIPn

Input Shutdown Input n When asserted the selected PWM channel outputs are shut down immediately.

Px_nn I/O Position n General purpose input/output. See the GP Ports chapter in the processor hardware reference

for programming information.

Table 6. Detailed Signal Descriptions (Continued)

Signal Name Direction Description

剩余111页未读,继续阅读

2014-01-14 上传

2020-07-29 上传

2020-10-19 上传

2020-07-29 上传

点击了解资源详情

2022-09-24 上传

2022-09-19 上传

LSXKL

- 粉丝: 11

- 资源: 7

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- JHU荣誉单变量微积分课程教案介绍

- Naruto爱好者必备CLI测试应用

- Android应用显示Ignaz-Taschner-Gymnasium取消课程概览

- ASP学生信息档案管理系统毕业设计及完整源码

- Java商城源码解析:酒店管理系统快速开发指南

- 构建可解析文本框:.NET 3.5中实现文本解析与验证

- Java语言打造任天堂红白机模拟器—nes4j解析

- 基于Hadoop和Hive的网络流量分析工具介绍

- Unity实现帝国象棋:从游戏到复刻

- WordPress文档嵌入插件:无需浏览器插件即可上传和显示文档

- Android开源项目精选:优秀项目篇

- 黑色设计商务酷站模板 - 网站构建新选择

- Rollup插件去除JS文件横幅:横扫许可证头

- AngularDart中Hammock服务的使用与REST API集成

- 开源AVR编程器:高效、低成本的微控制器编程解决方案

- Anya Keller 图片组合的开发部署记录

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功