FPGA多时钟域设计中的时钟同步及亚稳态风险评估-PPT版

需积分: 19 113 浏览量

更新于2024-01-20

收藏 1.17MB PPT 举报

边沿检测同步器是一种广泛应用于数字系统设计中的电路,用于将信号从一个时钟域传递到另一个时钟域。在FPGA(Field Programmable Gate Array)的跨时钟域设计中,边沿检测同步器被用于解决慢时钟域到快时钟域的数据传输问题。本文主要介绍了FPGA跨时钟域设计的相关概念和技术。

首先,本文介绍了局部同步设计概念。局部同步设计是指在一个时钟域内同步的设计方法。全同步设计是指整个系统只有一个时钟信号,而全异步设计则是指系统中没有任何时钟信号。在FPGA设计中,由于系统复杂性和功能要求的限制,往往需要多个独立的时钟域,这就是多时钟域设计的需求,也是本文关注的重点。

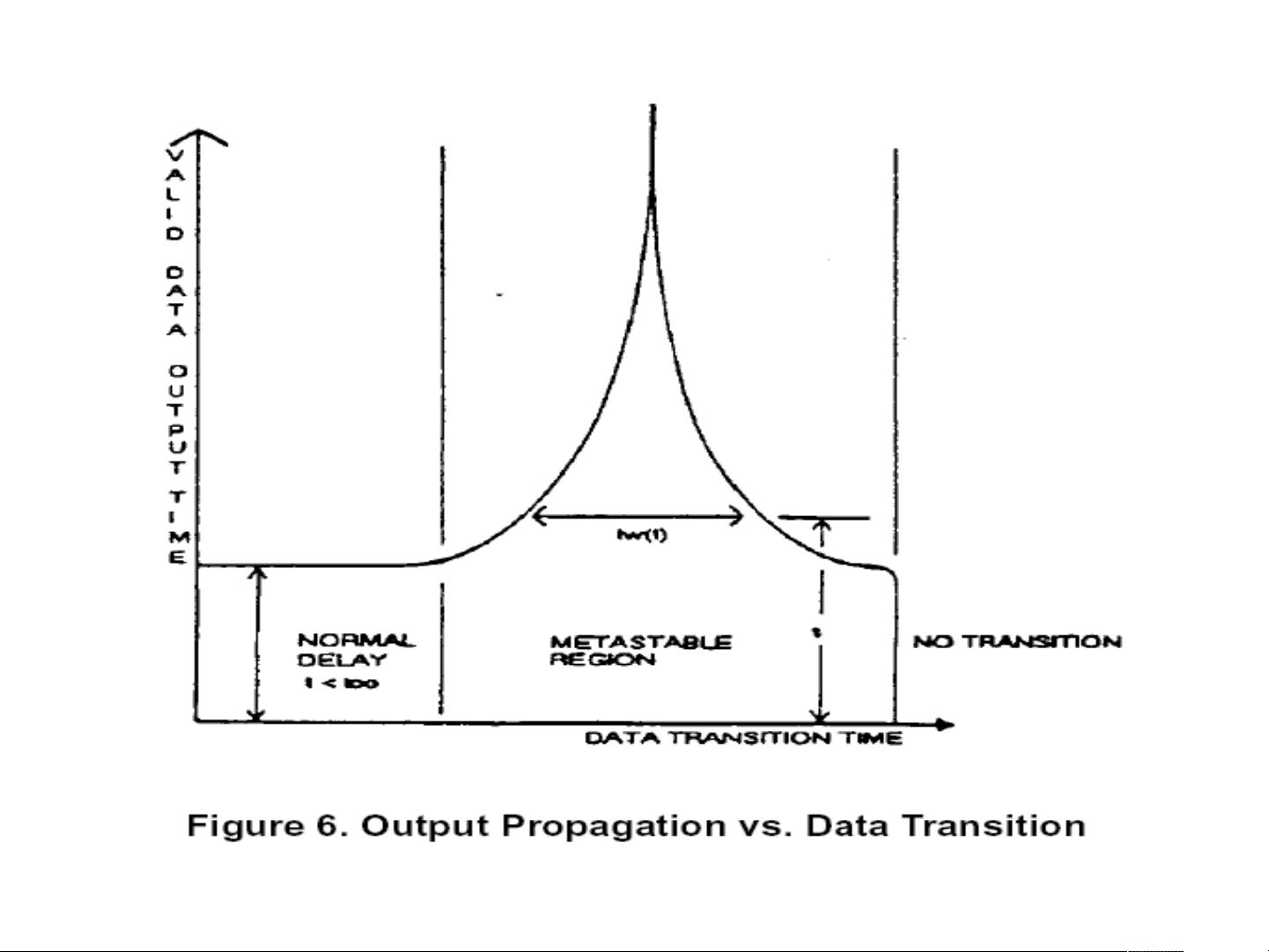

接下来,本文详细介绍了亚稳态的概念。亚稳态是指在边沿检测同步器工作过程中可能发生的临界状态,导致输出信号的不确定性或不稳定性。亚稳态的产生主要是由时钟信号的插入边界附近引起的,可能导致同步失败。亚稳态对系统的可靠性造成危害,因此需要评估其风险并采取相应的措施进行减少。

在FPGA跨时钟域设计中,同步器起着至关重要的作用。同步器是一种用于解决亚稳态问题的电路,通过握手信号和保持寄存器来确保数据的同步传输。本文介绍了同步器的工作原理和常用的设计方法。

此外,本文还介绍了异步FIFO设计,它是一种常用的多时钟域设计技术。异步FIFO是一个用于不同时钟域之间数据传输的缓冲区,通过握手信号和保持寄存器来实现异步数据传输,从而解决不同时钟域之间的数据同步问题。

最后,本文总结了FPGA跨时钟域设计的重要性和挑战。在设计复杂的数字系统时,多时钟域设计是不可避免的,单一时钟不能满足复杂的功能要求。然而,跨时钟域设计中存在亚稳态问题,可能导致同步失败和系统可靠性的降低。因此,设计人员需要了解亚稳态的原因和危害,并采取相应的措施进行风险评估和减少。

总而言之,本文详细介绍了FPGA跨时钟域设计中的边沿检测同步器和相关技术。通过合理设计同步器和异步FIFO,可以实现不同时钟域之间的数据传输,并解决亚稳态问题。在实际应用中,设计人员需要仔细考虑不同时钟域之间的数据同步需求,并选择合适的设计方法来确保系统的性能和可靠性。

150 浏览量

180 浏览量

点击了解资源详情

613 浏览量

747 浏览量

194 浏览量

372 浏览量

126 浏览量

420 浏览量

慕栗子

- 粉丝: 19

- 资源: 2万+

最新资源

- detectBrowserVisibility:检测浏览器可见性状态变化

- stomp-websocket-server:使用Spring的STOMP实现Websocket服务器

- python代码自动办公 Excel_案例_用Excel画画项目源码有详细注解,适合新手一看就懂.rar

- jQuery带备忘录功能的日期选择器特效代码

- NAS-DIP-pytorch:[ECCV 2020] NAS-DIP

- kj6682-library:我的图书馆

- Archive-1844_C++_

- 互联网站点:存储库,可扩展性或永久性

- breakout-rooms:分组讨论室附加到Jitsi Meet和Jitsi Videobridge项目中

- PHP实例开发源码-易优实验报告管理系统 PHP源码 v1.0.zip

- bikeshop:网络开发课程项目

- python代码自动办公 用Python在Excel中查找并替换数据 项目源码有详细注解,适合新手一看就懂.rar

- KonradLinkowski:我的GitHub操作配置文件README :)

- WEB1:某种html内容

- Node-Chat:建立在Node.js,Socket.io和WebRTC上的类似omegle的应用程序

- Leveon Bell HD Wallpapers Game Theme-crx插件