TI新一代高性能SoC DM816x最小系统构建详解:时钟配置与资源优化

190 浏览量

更新于2024-08-31

收藏 743KB PDF 举报

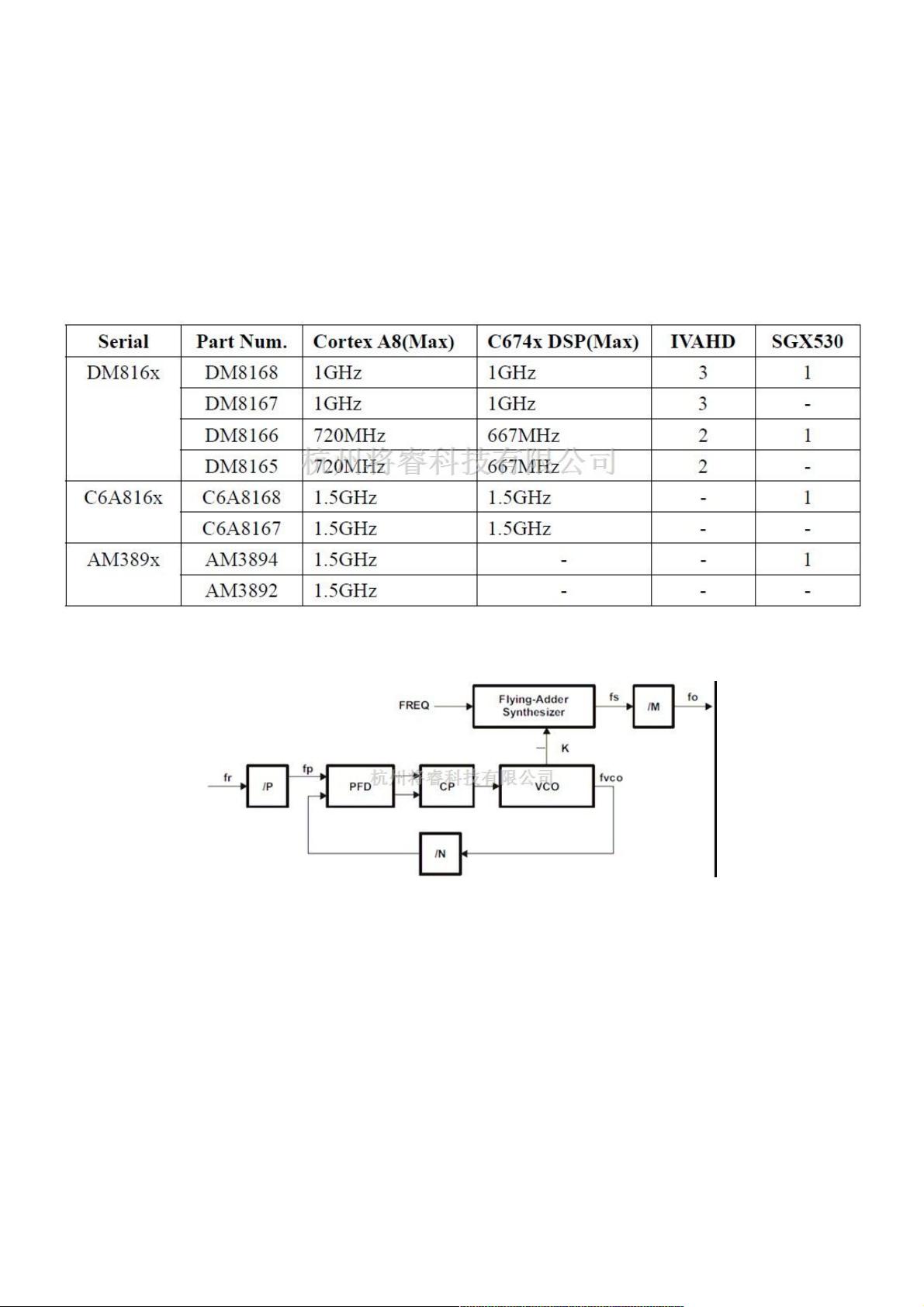

本文主要探讨了TI新一代高性能SoC,如DM816x、C6A816x和AM389x,它们在单片机与DSP领域的应用中构建最小系统的关键要点。这些SoC的特点在于系统集成度高和模块化的系统控制,它们的架构相较于传统TI SoC平台有着显著的不同。文章的核心内容聚焦在以下几个方面:

1. **时钟配置**:DM816x内部拥有4个FAPLL(Flying Adder PLL),这是其独特之处,提供了高精度、快速响应且降低模拟电路复杂性的时钟解决方案。FAPLL支持小数分频,使得用户能够方便地生成所需的定制频率。每个FAPLL由Multiphase PLL和FlyingAdder Synthesizer组成,其中Multiphase PLL的配置通过特定的控制寄存器进行,如MAINPLL_CTRL、DDRPLL_CTRL、VIDEOPLL_CTRL和AUDIOPLL_CTRL。

2. **电源管理**:尽管未在给定的部分详细介绍,但高效和优化的电源管理也是构建最小系统的重要环节,确保芯片在各种工作模式下的功耗控制和稳定性。

3. **内存映射**:由于DM816x系列产品的引脚兼容性,用户可以根据需求选择合适的SoC型号,而不会因硬件配置改变而重新设计内存映射,这大大简化了系统开发流程。

4. **内存配置**:内存配置涉及到处理器访问内外存的方式,包括存储器类型(如Flash、RAM)、地址空间划分以及可能的内存扩展选项。对于DM816x,合理的内存配置有助于提高系统性能和灵活性。

5. **平台兼容性和灵活性**:这些SoC的兼容性设计允许开发者在一个基础平台上进行定制,减少了重复的工作,提高了开发效率。

通过深入理解并应用这些特性,设计师能够更有效地构建和优化基于DM816x、C6A816x和AM389x的最小系统,实现高性能和低功耗的嵌入式解决方案。这对于任何寻求在工业界或学术研究中使用这些技术的人来说,都是至关重要的知识。

2020-11-08 上传

2020-11-27 上传

2020-12-03 上传

2020-12-10 上传

2020-11-26 上传

2020-12-10 上传

weixin_38687968

- 粉丝: 7

- 资源: 969

最新资源

- Android圆角进度条控件的设计与应用

- mui框架实现带侧边栏的响应式布局

- Android仿知乎横线直线进度条实现教程

- SSM选课系统实现:Spring+SpringMVC+MyBatis源码剖析

- 使用JavaScript开发的流星待办事项应用

- Google Code Jam 2015竞赛回顾与Java编程实践

- Angular 2与NW.js集成:通过Webpack和Gulp构建环境详解

- OneDayTripPlanner:数字化城市旅游活动规划助手

- TinySTM 轻量级原子操作库的详细介绍与安装指南

- 模拟PHP序列化:JavaScript实现序列化与反序列化技术

- ***进销存系统全面功能介绍与开发指南

- 掌握Clojure命名空间的正确重新加载技巧

- 免费获取VMD模态分解Matlab源代码与案例数据

- BuglyEasyToUnity最新更新优化:简化Unity开发者接入流程

- Android学生俱乐部项目任务2解析与实践

- 掌握Elixir语言构建高效分布式网络爬虫