《数字集成电路静态时序分析》学习笔记

"《数字集成电路静态时序分析基础》是一门关于集成电路验证和静态时序分析的网络课程,主要讲解了TCL语言的基础知识以及在数字集成电路分析中的应用。"

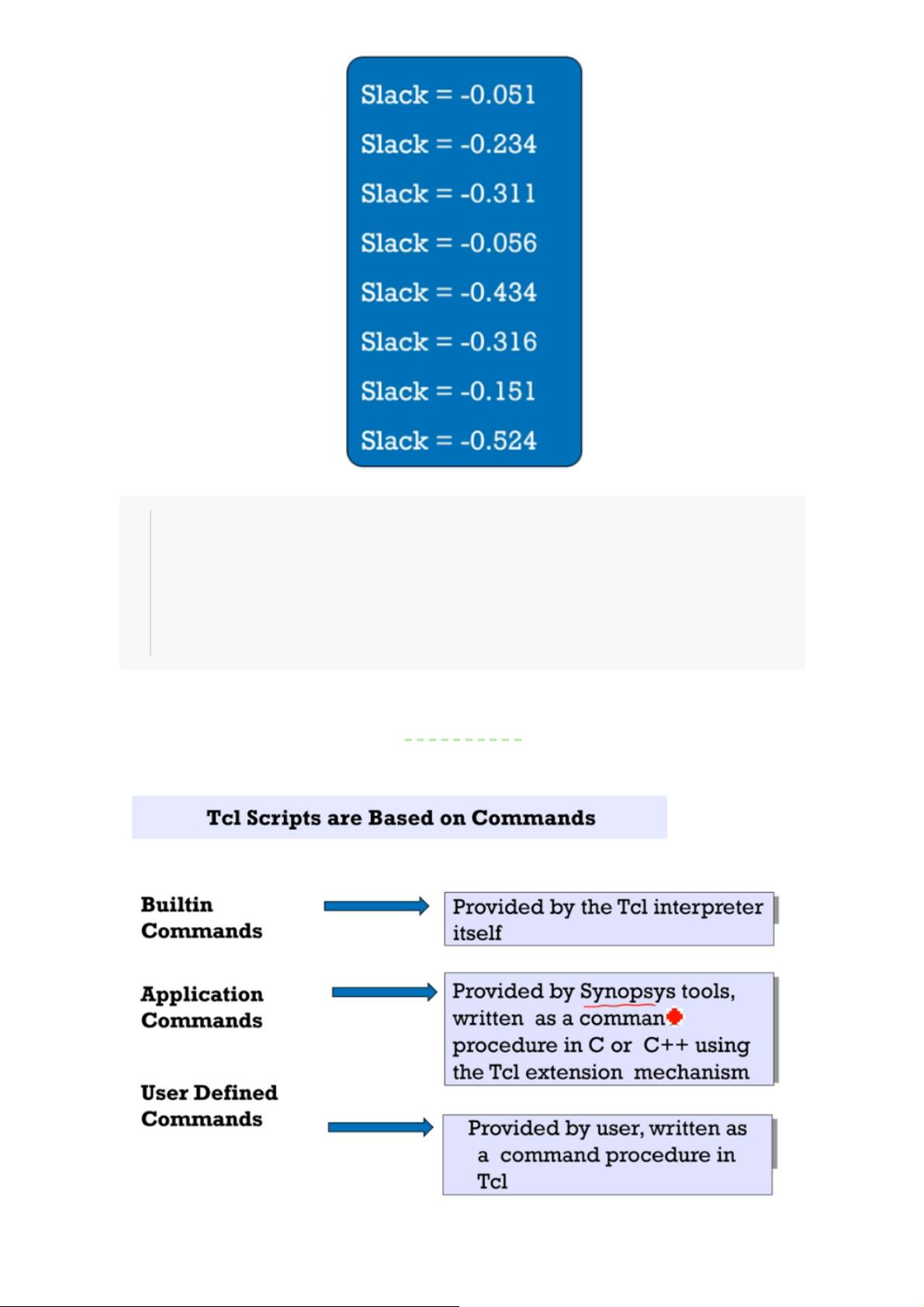

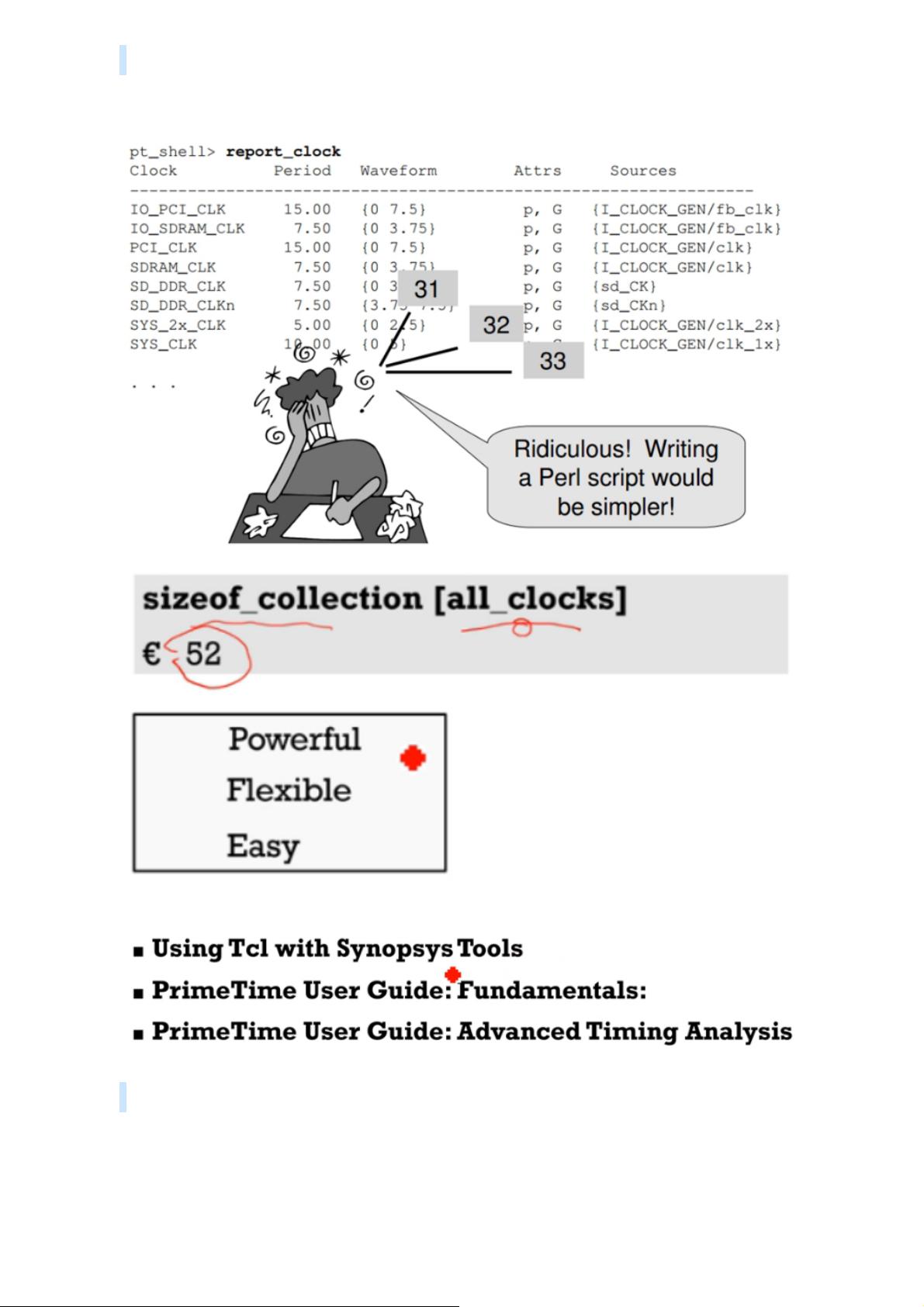

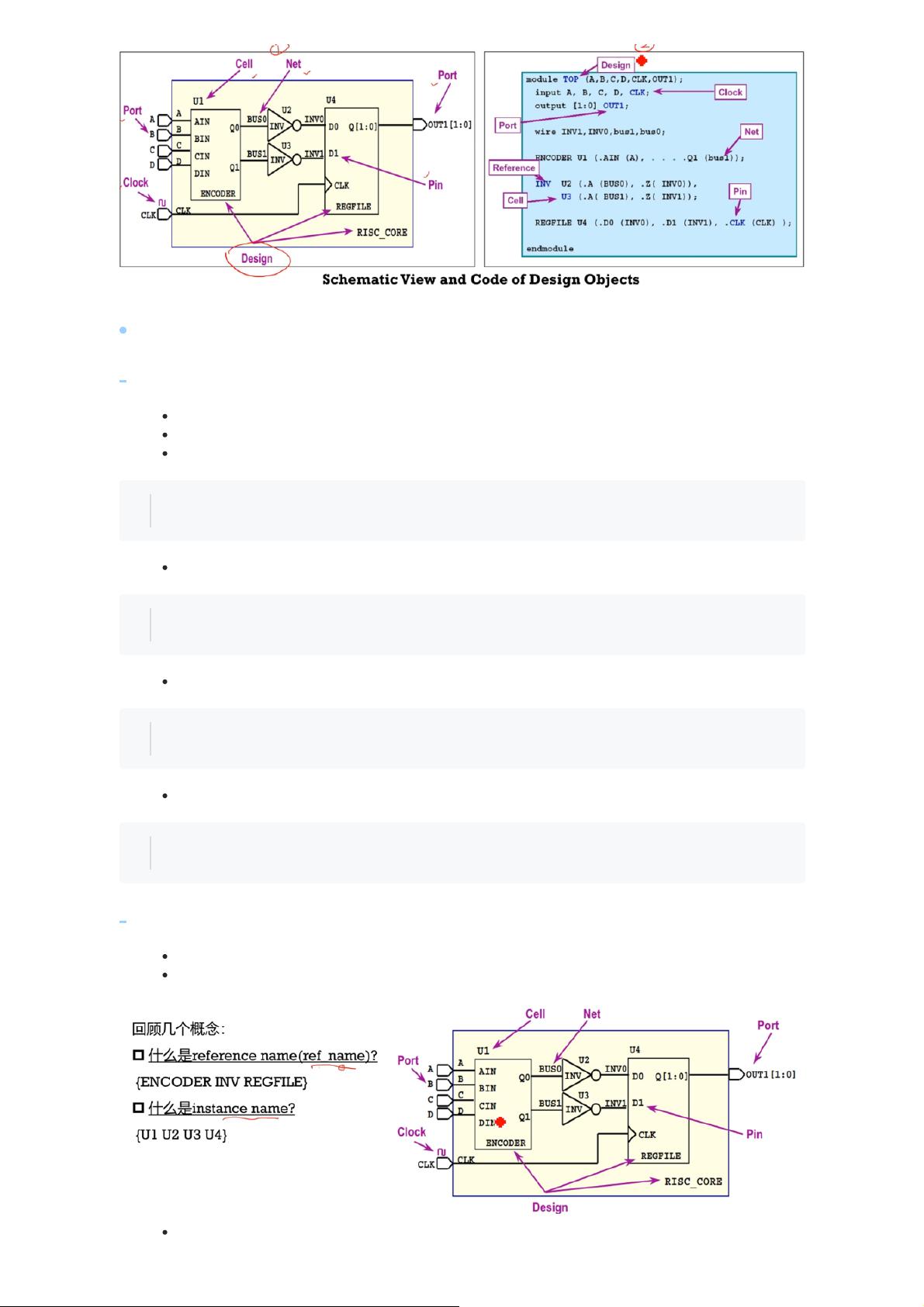

在数字集成电路的设计和验证中,静态时序分析(Static Timing Analysis, STA)是一种关键的技术,用于确定电路的性能和时序裕量。它可以帮助工程师评估电路是否能够在预定的时钟周期内正确工作,从而避免潜在的延迟问题。而TCL作为一种强大的脚本语言,常被用于自动化验证流程和时序分析工具的控制。

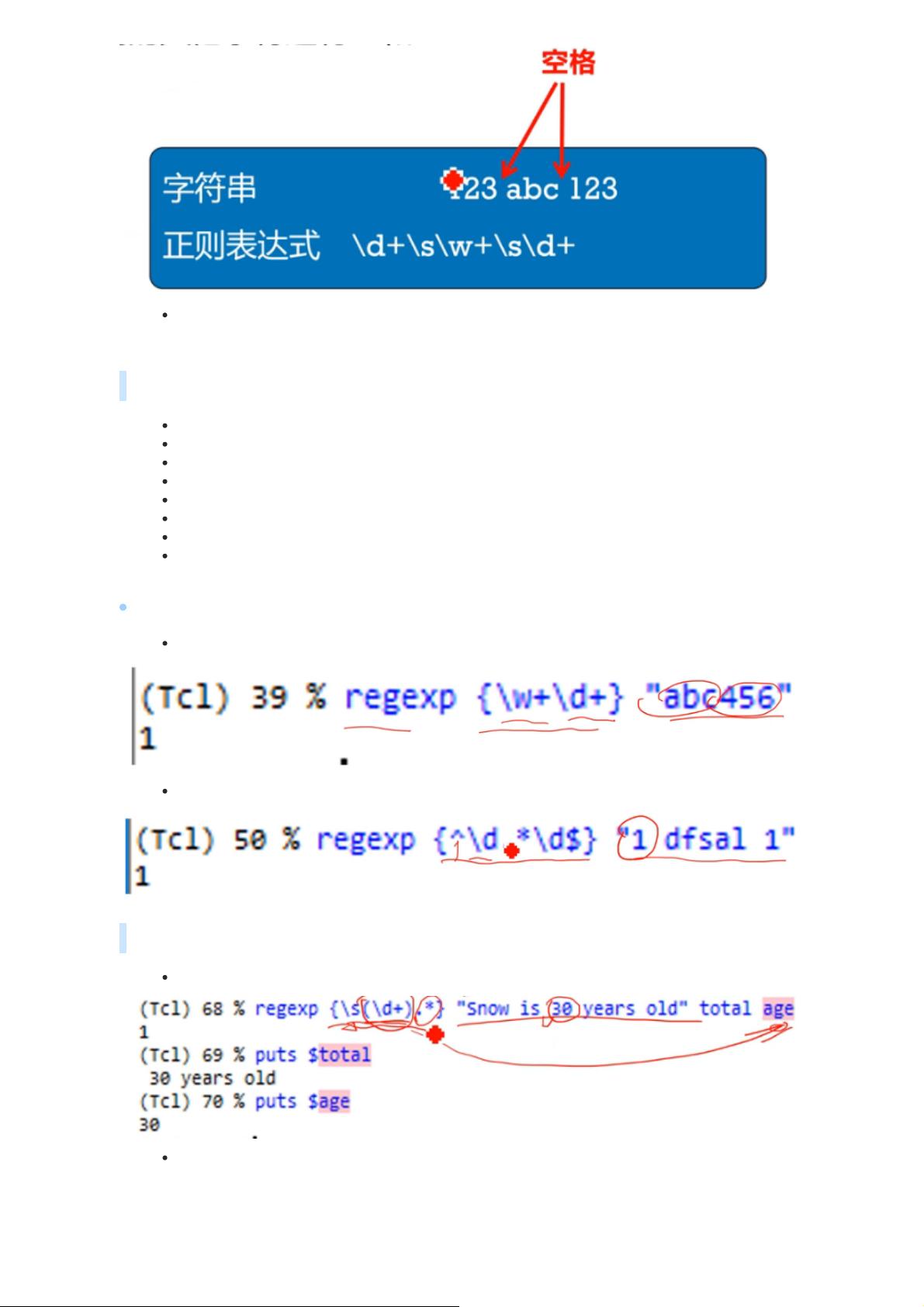

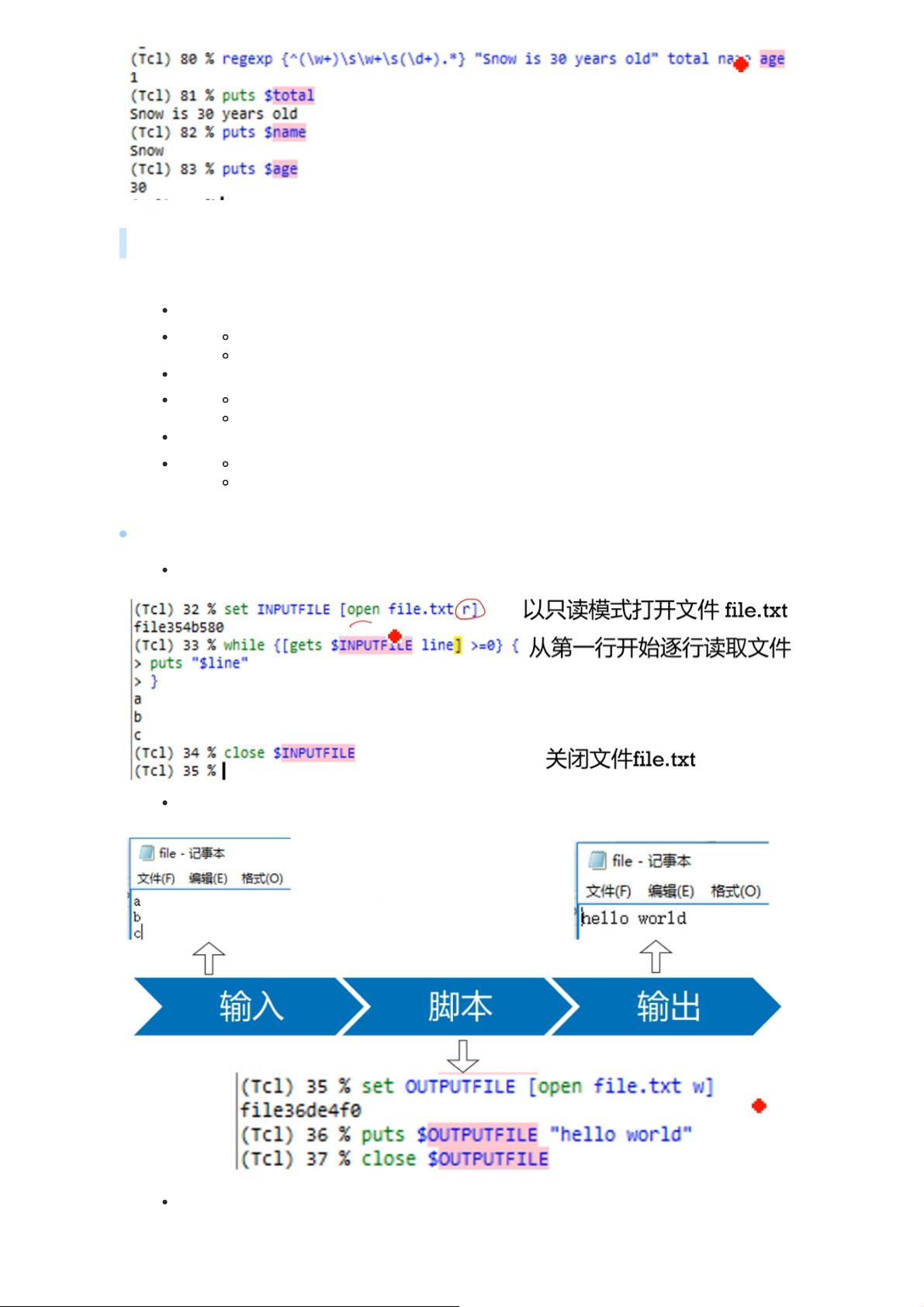

TCL的基础知识包括变量与数据结构的使用。变量定义使用`set`命令,例如`set variableName variableValue`,引用变量则通过`$variableName`。TCL提供三种置换方式:

1. 变量置换:使用`$`,如`$myVar`。

2. 命令置换:使用`[]`,例如`[expr $num + 1]`。

3. 反斜杠置换:使用`\`来转义特殊字符,如`\t`代表制表符,`\n`代表换行。

数组在TCL中是另一种数据结构,定义和取值分别用`set arrayName(elementName) value`和`$arrayName(elementName)`。可以使用`array`指令获取数组的信息。

列表是TCL中的标量有序集合,可以使用`{}`来定义,如`set myList {element1 element2 element3}`。对列表的操作包括:

- `concat`:合并两个列表。

- `llength`:返回列表元素数量。

- `lindex`:获取列表的指定位置元素。

- `lappend`:在列表末尾添加元素。

- `lsort`:对列表进行排序,可选参数实现不同排序方式。

在数学运算方面,TCL支持基本的算术操作(如加、减、乘、除)和比较运算(如小于等于、大于等于、等于和不等于)。`expr`命令用于执行复杂的数学表达式,例如`expr $num1 + $num2`。

对于静态时序分析,理解TCL语言是必要的,因为很多时序分析工具(如Synopsys的PrimeTime)的脚本接口都是基于TCL的。这门课程会深入探讨如何利用TCL进行时序路径的提取、约束设置、报告解析等任务,以优化数字集成电路的性能和时序合规性。

点击了解资源详情

点击了解资源详情

点击了解资源详情

138 浏览量

2023-06-22 上传

254 浏览量

2022-04-14 上传

2021-07-13 上传

2019-02-27 上传