VHDL语言实验教程:使用MAXPLUS II进行硬件描述

需积分: 50 94 浏览量

更新于2024-07-31

收藏 307KB DOC 举报

“VHDL语言实验指导书 word文档,用于学习MAXPLUS II软件的使用,包括VHDL语言编程的实践操作。”

本实验指导书是针对VHDL语言学习者的一份宝贵资料,旨在帮助读者熟悉MAXPLUS II集成开发环境,并通过实际操作掌握VHDL语言的编程技巧。VHDL是一种硬件描述语言,广泛应用于数字电路的设计和验证,它允许设计者以抽象的方式描述硬件系统的行为和结构。

实验一的主要目标是让学习者熟练掌握MAXPLUS II软件的使用,包括软件环境的熟悉、VHDL程序的调用和编译、以及仿真结果的观察。实验内容分为三个部分:学习指导书中的步骤、编写并调试VHDL程序、进行仿真验证。

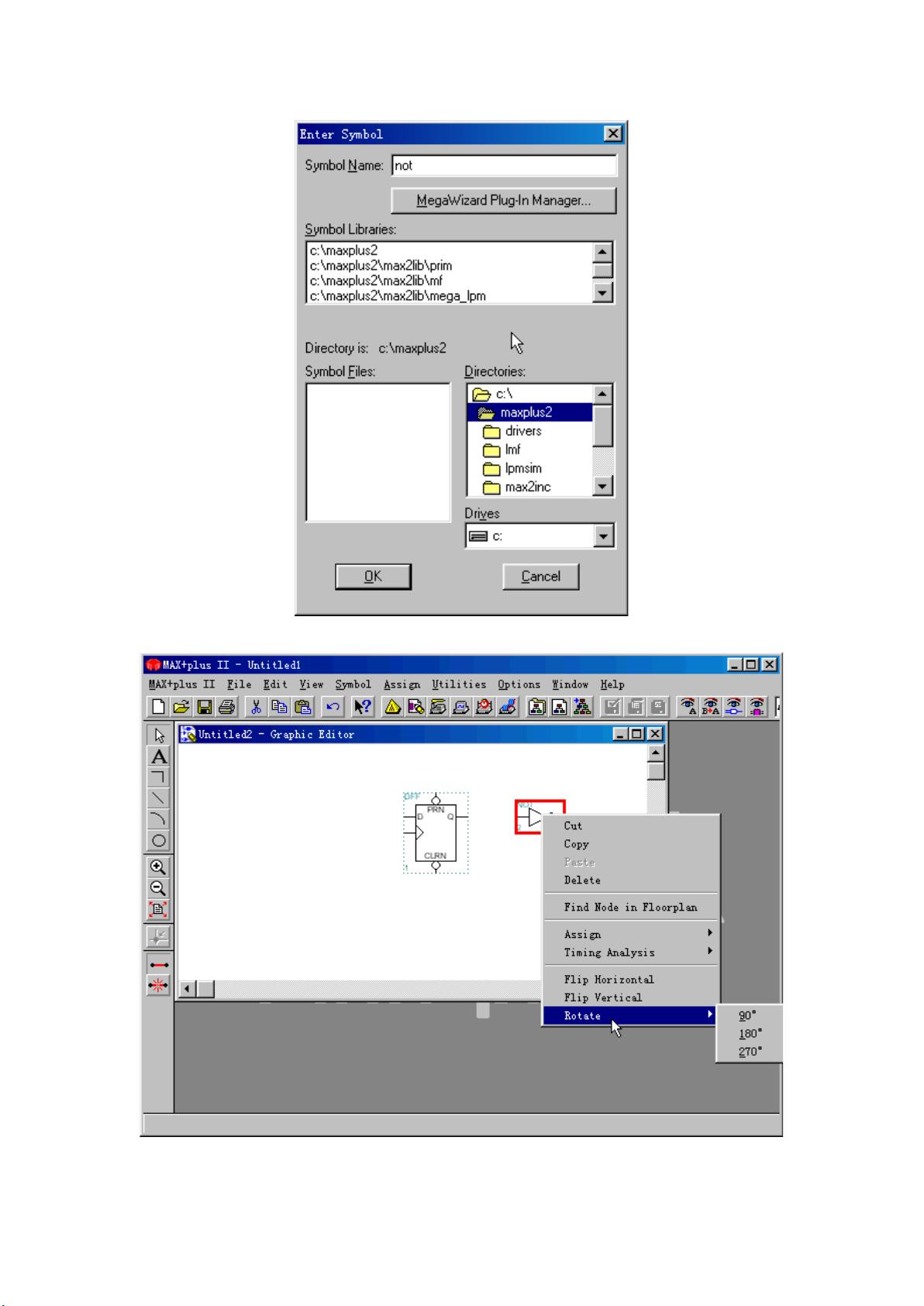

实验的具体步骤以二分频器的设计为例,通过ALTERA的EPLD——EPM7128S进行演示。首先,启动MAXPLUS II软件,运行maxstart.exe。然后,利用GraphicEditorfile(*.gdf)创建新的设计输入文件,使用原理图方式进行设计,这种方式直观且易于理解。在设计过程中,需要输入逻辑元件,例如D触发器和反相器,以及定义I/O脚,并进行连线。

在设计完成后,需要设置工程名,选择File->Project->SetProjecttoCurrentFile,将当前工程名设为设计文件名。接下来,指定器件,即选择EPLD类型,此处选择了MAX7000系列的EPM7128SLC84-10。最后,进行编译,通过选择MAX+PLUSII->Compiler,启动编译过程。成功编译后,可以通过编译窗口的报告来检查设计的正确性。

这个实验过程不仅涵盖了VHDL语言的基本编程,还涉及到了硬件实现的流程,包括逻辑门级的建模、器件选择和编译验证。对于初学者来说,这样的实践环节能有效提升对VHDL语言和FPGA设计的理解。通过不断练习,学习者可以逐步掌握复杂硬件系统的建模和实现,从而在数字系统设计领域打下坚实的基础。

点击了解资源详情

点击了解资源详情

2012-06-28 上传

154 浏览量

162 浏览量

247 浏览量

174 浏览量

278 浏览量

115 浏览量

hsgyunzhongyue

- 粉丝: 3

最新资源

- 第七届ITAT移动互联网站设计决赛试题分享

- C语言实现52张牌随机分发及排序方法

- VS2008智能提示补丁,让英文变中文的解决办法

- SISTEMA-LACONQUISTA:深入解析Windows窗体窗口应用开发

- STM32F407单片机RTC闹钟唤醒功能实验教程

- CRRedist2005 X86:水晶报表下载辅助文件解析

- Android开发中调用WebService的简易实例教程

- React Native与Electron融合:打造桌面端PWA应用

- fping:高效的网络端口批量测试工具

- 深入解析Spring与MyBatis的整合配置及问题答疑

- 深入探讨Struts2与Spring整合技术实现

- Java游戏项目开发实战:游戏项目1深入解析

- STM32掌机测试教程与资源分享

- Win7内置搜索小工具:百度与谷歌搜索集成

- JWPlayer JavaScript API下载指南

- 精易模块V5.22新特性与功能更新解析