DSP实现的软件锁相环技术探析

"基于DSP的PLL数字锁相技术详解"

PLL(Phase-Locked Loop,数字锁相环)是一种广泛应用于通信、雷达、导航等领域的信号处理技术,它主要用于频率合成、相位同步和频率分频等任务。在数字信号处理时代,特别是在高速DSP(Digital Signal Processor)的支持下,PLL技术也逐渐转向软件实现,即软件锁相环。

软件锁相环的核心优势在于其灵活性和可编程性。与传统的模拟锁相环或硬件实现的数字锁相环相比,软件锁相环可以通过改变软件算法来调整环路特性,适应不同的工作环境和需求。这种技术的发展与软件无线电(Software Defined Radio, SDR)的兴起密切相关,因为SDR强调利用软件来实现通信系统的大部分功能,包括频率处理。

在软件锁相环的构建过程中,通常会涉及以下关键组件:

1. 数字鉴相器:负责比较输入参考信号与压控振荡器(VCO)输出信号的相位差,并将相位差转换为数字量。在Z域中,数字鉴相器的模型可以用差分方程来表示,如公式所描述,它可以是基于正交分解或其他方法实现的。

2. 低通滤波器:也称为环路滤波器,其作用是平滑鉴相器的输出,去除高频噪声,并决定锁相环的响应速度和稳定性。在软件实现中,滤波器通常由一系列乘法器、加法器和延迟单元组成,可以使用IIR(无限脉冲响应)或FIR(有限脉冲响应)滤波器结构。

3. 压控振荡器:根据低通滤波器的输出调整其输出频率,以使相位差趋于零。在软件锁相环中,VCO可能被模拟为一个频率控制项,通过改变数字信号的相位或频率来实现。

4. 延时估计:在软件锁相环中,准确的延时估计是关键,因为它直接影响到锁相环的捕获速度和跟踪性能。延时通常通过插值或抽取技术来估计。

5. 多速率条件下的锁相环:在不同采样率条件下,锁相环的模型需要相应调整。多速率锁相环模型考虑了采样率的变化,确保在不同速率下仍能保持良好的相位锁定性能。

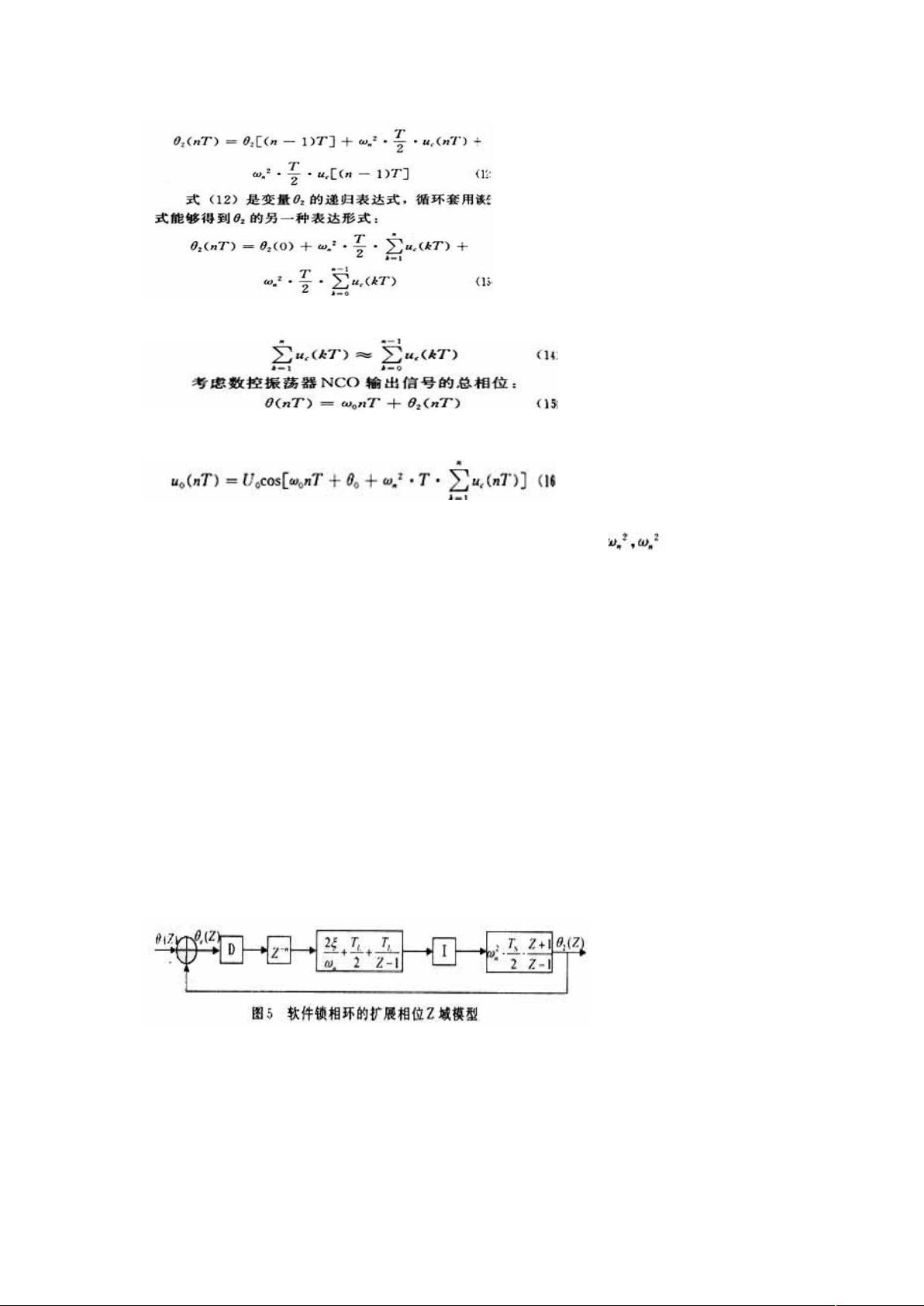

软件锁相环的建模通常在Z域进行,通过双线性变换法将模拟系统的S域模型转换为数字系统的Z域模型。这种方法能够清晰地表达系统动态,并简化设计过程。例如,将模拟的二阶二型锁相环通过双线性变换转化为数字模型,可以得到软件锁相环的Z域模型,如图1、图2和图3所示。

在图3所示的模型Ⅱ中,τ1,τ2和K分别对应于软件实现的乘法器、加法器和寄存器,这比模型Ⅰ更符合实际的软件实现。

基于DSP的软件锁相环技术是一种高效、灵活的信号处理手段,它允许在不改变硬件的情况下,通过调整软件算法来优化锁相环的性能,适应各种复杂的通信环境。随着高速DSP技术的进步,软件锁相环将在未来的无线通信和信号处理领域发挥更大的作用。

2020-10-23 上传

2019-08-13 上传

点击了解资源详情

2022-09-23 上传

2021-10-04 上传

2021-05-08 上传

164 浏览量

2023-03-07 上传

lzjzdq

- 粉丝: 2

- 资源: 4

最新资源

- 探索AVL树算法:以Faculdade Senac Porto Alegre实践为例

- 小学语文教学新工具:创新黑板设计解析

- Minecraft服务器管理新插件ServerForms发布

- MATLAB基因网络模型代码实现及开源分享

- 全方位技术项目源码合集:***报名系统

- Phalcon框架实战案例分析

- MATLAB与Python结合实现短期电力负荷预测的DAT300项目解析

- 市场营销教学专用查询装置设计方案

- 随身WiFi高通210 MS8909设备的Root引导文件破解攻略

- 实现服务器端级联:modella与leveldb适配器的应用

- Oracle Linux安装必备依赖包清单与步骤

- Shyer项目:寻找喜欢的聊天伙伴

- MEAN堆栈入门项目: postings-app

- 在线WPS办公功能全接触及应用示例

- 新型带储订盒订书机设计文档

- VB多媒体教学演示系统源代码及技术项目资源大全