Amphion MPEG2解码器原理与应用设计详解

需积分: 9 34 浏览量

更新于2024-09-06

收藏 343KB PDF 举报

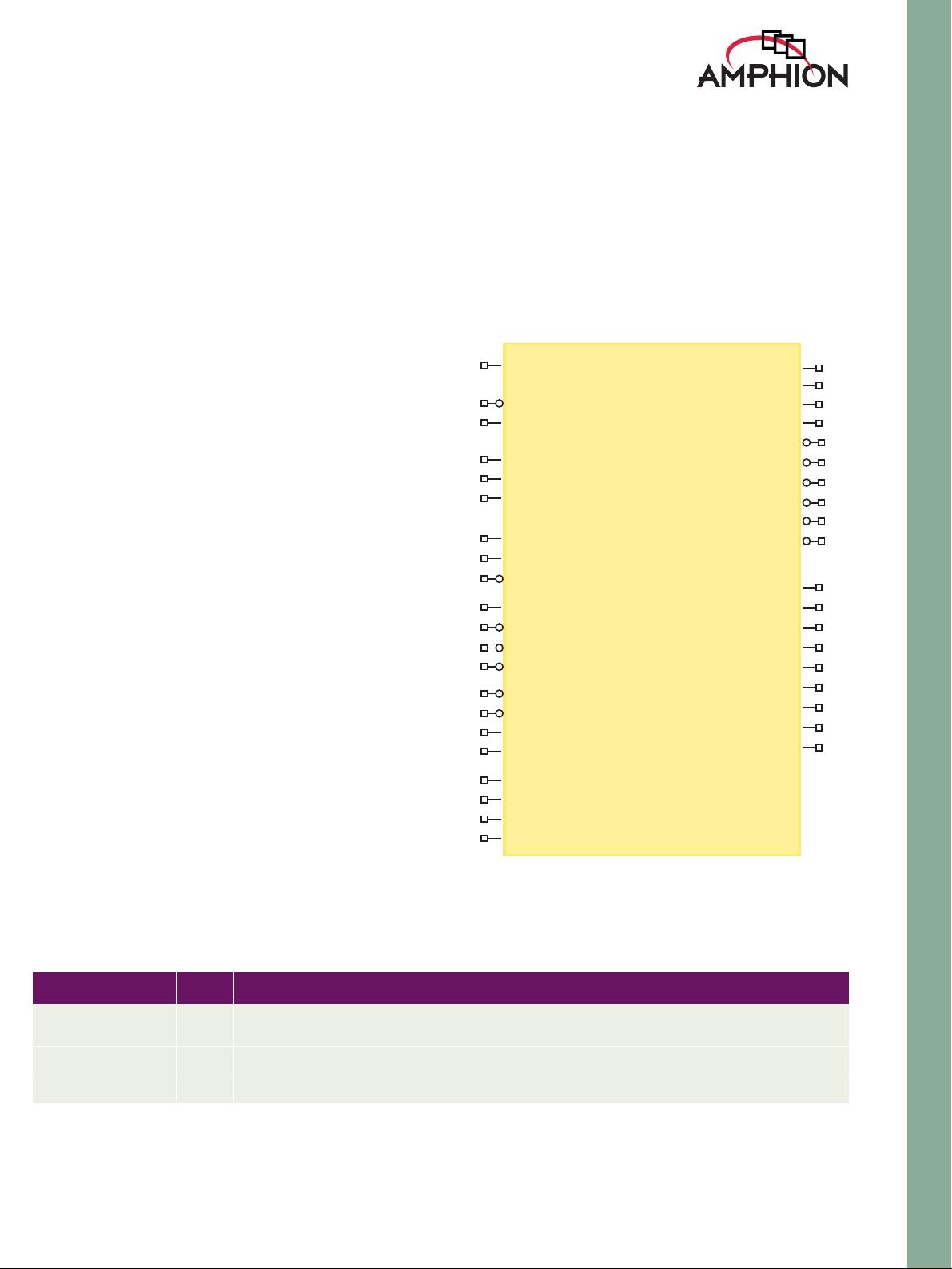

MPEG2 Decoder 原理图是Amphion公司针对高清晰度视频解码器市场推出的一款应用特定核心芯片——CS6650的设计图纸。这款解码器专为满足广泛的运动图像应用需求而设计,遵循ISO/IEC 13818-2(MPEG2)标准,支持高达4:2:2 Profile的高级别解码(422@HL)。它不仅适用于主流消费电子设备,能够处理4:2:0位流的高或主要级别编码(MP@HL),还兼容MPEG1(ISO/IEC 11172-2)编码的解码。

该解码器的核心结构包括以下几个关键模块:

1. **Host Interface**: 用于与外部处理器(如微处理器)进行通信,允许数据交换和控制信号的传输,确保系统的稳定集成。

2. **Video Stream Parser**: 分析输入的视频数据流,将其分解成便于解码的各个部分,执行帧同步和错误检测等功能。

3. **Input Video Data Stream**: 输入的原始MPEG2视频数据,包含视频图像、音频以及其他相关信息。

4. **Frame Store**: 存储解码后的帧,以便在需要时提供连续的视频输出。

5. **SDRAMs**: 高速存储器,用于临时存储数据和优化解码性能,减少CPU访问延迟。

6. **Output Picture Data**: 解码后的视频数据,输出为清晰的像素信息,可供显示或进一步处理。

7. **Motion Compensation**: 通过预测和补偿技术来减少视频序列中的运动失真,提高画面流畅度。

8. **Variable Length Code Decoder**: 处理MPEG2压缩编码中的可变长度编码,实现高效的数据压缩和解压。

9. **Run Level Decoder**: 解码并解析编码中的运行长度(Run-Length)信息,这是MPEG2编码中的一种压缩方法。

10. **Microprocessor Interface**: 与微处理器协同工作,控制解码过程和处理解码后的数据。

CS6650的优势在于其高度集成,提供了卓越的性能,同时注重降低功耗和减小硅片面积,这使得它成为在消费电子、家庭娱乐系统、卫星接收器等应用领域中理想的解码解决方案。对于系统设计师来说,这份原理图提供了宝贵的设计参考,可以帮助他们理解和优化自己的硬件系统,以实现高效的MPEG2视频解码功能。

2022-09-21 上传

2009-11-19 上传

117 浏览量

2018-06-06 上传

2011-08-25 上传

点击了解资源详情

2024-11-04 上传

drjiachen

- 粉丝: 172

- 资源: 2138

最新资源

- Aspose资源包:转PDF无水印学习工具

- Go语言控制台输入输出操作教程

- 红外遥控报警器原理及应用详解下载

- 控制卷筒纸侧面位置的先进装置技术解析

- 易语言加解密例程源码详解与实践

- SpringMVC客户管理系统:Hibernate与Bootstrap集成实践

- 深入理解JavaScript Set与WeakSet的使用

- 深入解析接收存储及发送装置的广播技术方法

- zyString模块1.0源码公开-易语言编程利器

- Android记分板UI设计:SimpleScoreboard的简洁与高效

- 量子网格列设置存储组件:开源解决方案

- 全面技术源码合集:CcVita Php Check v1.1

- 中军创易语言抢购软件:付款功能解析

- Python手动实现图像滤波教程

- MATLAB源代码实现基于DFT的量子传输分析

- 开源程序Hukoch.exe:简化食谱管理与导入功能