原码一位除法器设计与实现

下载需积分: 10 | DOC格式 | 425KB |

更新于2024-08-01

| 142 浏览量 | 举报

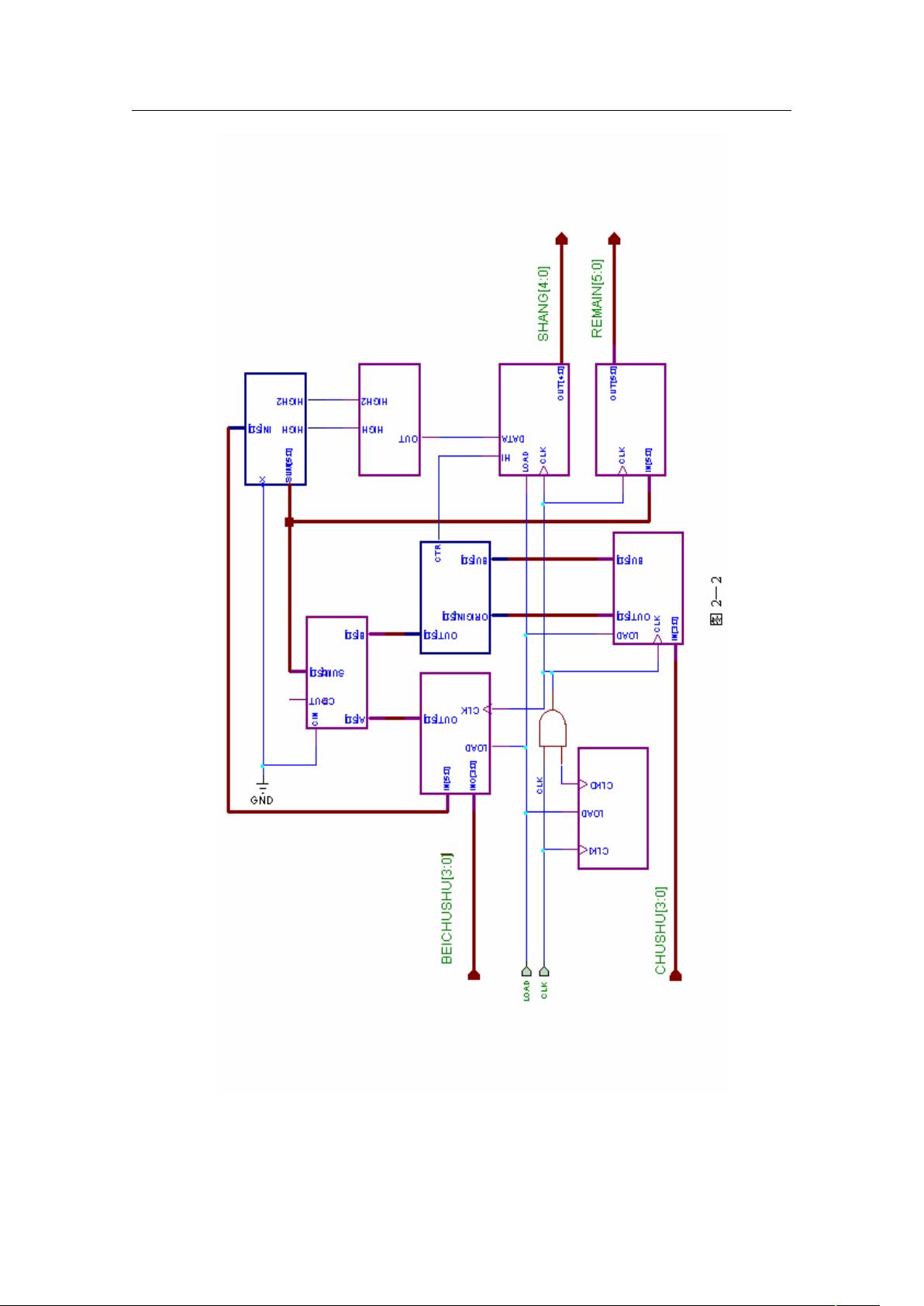

"本文主要介绍了原码一位除除法器的设计方案,该设备用于执行除法运算,采用不恢复余数法。设计中包括了三个寄存器A、B、C,分别存储被除数/余数、除数和商,以及一个用于加法运算的D寄存器。在运算过程中,根据加法器输出的符号位判断是加Y还是加[-Y]补,以确定下一位商。设计还包括移位电路和将除数Y与[-Y]补送入加法器的功能。设计流程涉及Verilog硬件描述语言的程序编写,最终通过XCV200可编程逻辑芯片实现硬件测试。设计环境包括伟福COP2000实验仪、XCV200实验板和相关EDA软件。"

原码一位除除法器是一种基于原码表示的数字系统中的除法运算单元,它使用不恢复余数法进行运算。在这个方法中,被除数(或余数)存储在A寄存器,除数在B寄存器,而商则保存在C寄存器。D寄存器用于存储除数Y的补码或者[-Y]补,这取决于加法器的运算结果符号。在运算开始时,被除数加载到A寄存器,除数加载到B寄存器,A寄存器的初始值作为首余数。

运算过程如下:根据加法器的符号位,如果为负,则加Y,否则加[-Y]补,然后将结果左移一位进入A寄存器。同时,C寄存器通过移位电路左移,将高位置入商的位。商的符号由被除数和除数的符号位半加结果决定。在不恢复余数法中,最后一位商为0时,需要额外恢复余数以确保正确结果。

设计中,移位电路是一个关键组件,它需要能够实现左移一位的功能。此外,还有一个专门的模块负责将除数Y和其补码[-Y]送入加法器。整个运算过程由LOAD信号控制,初始清零,然后通过一系列脉冲驱动运算,每次运算结果被存储并决定下一次操作是加余数的补码还是原码,最终商被存入C寄存器,余数留在A寄存器。

设计阶段采用Verilog硬件描述语言编写程序,并利用Xilinx Foundation F3.1设计软件进行编译和调试,最终生成的*.bit文件烧录到XCV200可编程逻辑芯片中,通过实际硬件测试验证设计的正确性和功能完整性。实验环境包括伟福COP2000实验平台、XCV200实验板以及相应的EDA仿真软件,如ModelSim。

这种原码一位除除法器设计提供了基础的除法运算能力,对于理解和实现数字系统中的除法操作具有重要意义,同时也为后续的硬件设计和系统集成提供了参考。

相关推荐

714 浏览量

121 浏览量

210 浏览量

265 浏览量

398 浏览量

2025-01-02 上传

464 浏览量

qls870228

- 粉丝: 1

最新资源

- 掌握Oracle DBA日常管理及常用SQL技巧

- SIFT算法演讲:深度详解与步骤演示

- Java图书管理系统课设代码实现与数据库配置教程

- 一键关闭惠普v3000笔记本屏幕的TOM工具

- 操作系统概念第7版练习答案解析

- FastStone Capture 8.4汉化版:强大屏幕捕捉与编辑工具

- Android项目结构:CircleLayout布局压缩包解读

- 机器学习NLP:深入理解停用词与LDA主题模型

- Android开发中服务框架的实践探索之路

- STL中文手册:C++初学者的实用学习指南

- 使用HideAdmin创建系统超级隐藏账户指南

- cube500sCN:智能魔方解密工具,破解最快步骤

- 深蓝词库转换工具:输入法词库文件的转换专家

- IOT脚本替换工具V1.3.3:一键完成代码查找与替换

- JavaWeb书店应用部署教程:连接Tomcat与MySQL

- 深入解析Win32系统服务与多媒体扩展编程