Serial RapidIO Gen2 v4.1 Endpoint IP Guide

需积分: 50 169 浏览量

更新于2024-07-09

收藏 4.11MB PDF 举报

"该文档是Xilinx公司的Serial RapidIO Gen2 v4.1 LogiCORE IP产品指南,属于Rapid IO技术的官方文档,详细介绍了该IP核的使用和设计流程。"

在RapidIO技术中,Serial RapidIO Gen2是一个重要的传输层协议,它基于串行接口,用于构建高性能、低延迟的通信网络,常应用于嵌入式系统和数据中心的互连。此文档详细阐述了Serial RapidIO Gen2 v4.1版本的特性、规范、设计指导和实现步骤。

1. **系统概述**:

- 文档提到了Serial RapidIO Gen2在系统中的角色,可能包括作为处理器、存储器和其他外设之间的高速数据通道。

- 应用场景可能包括高性能计算、网络设备、航空航天与国防等领域。

- 不支持的特性也在这部分中列出,帮助用户理解其局限性。

- 软件和硬件的许可信息也在这里提及,对于合规使用非常重要。

2. **产品规格**:

- 标准符合性:Serial RapidIO Gen2遵循相应的电气和协议标准,确保与其他RapidIO设备的兼容性。

- 性能:描述了IP核在传输速率、带宽等方面的表现。

- 资源利用率:详细列出了该IP核在FPGA或ASIC上的逻辑资源占用情况。

- 串行收发器支持:说明了与物理层收发器的配合方式,包括速度等级和功耗优化。

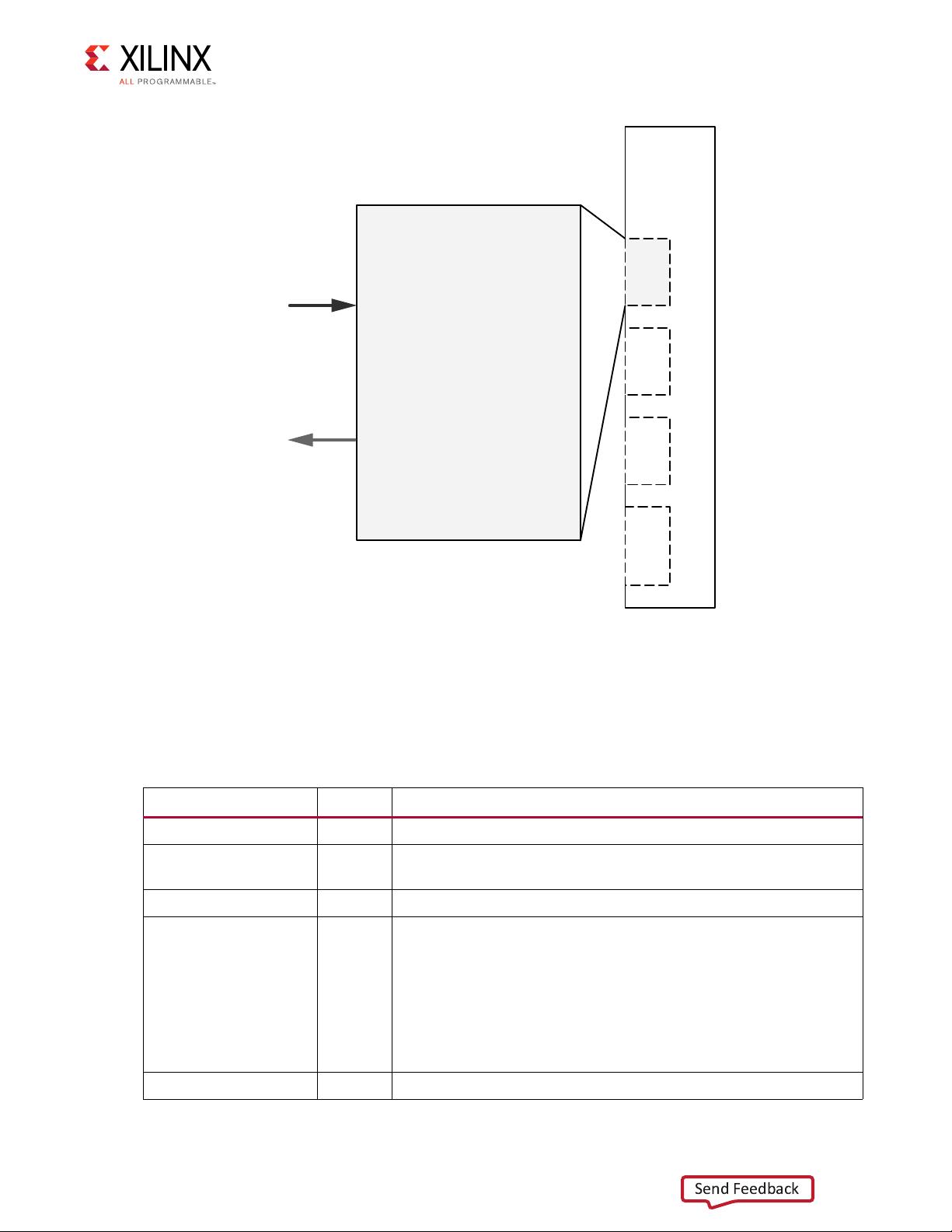

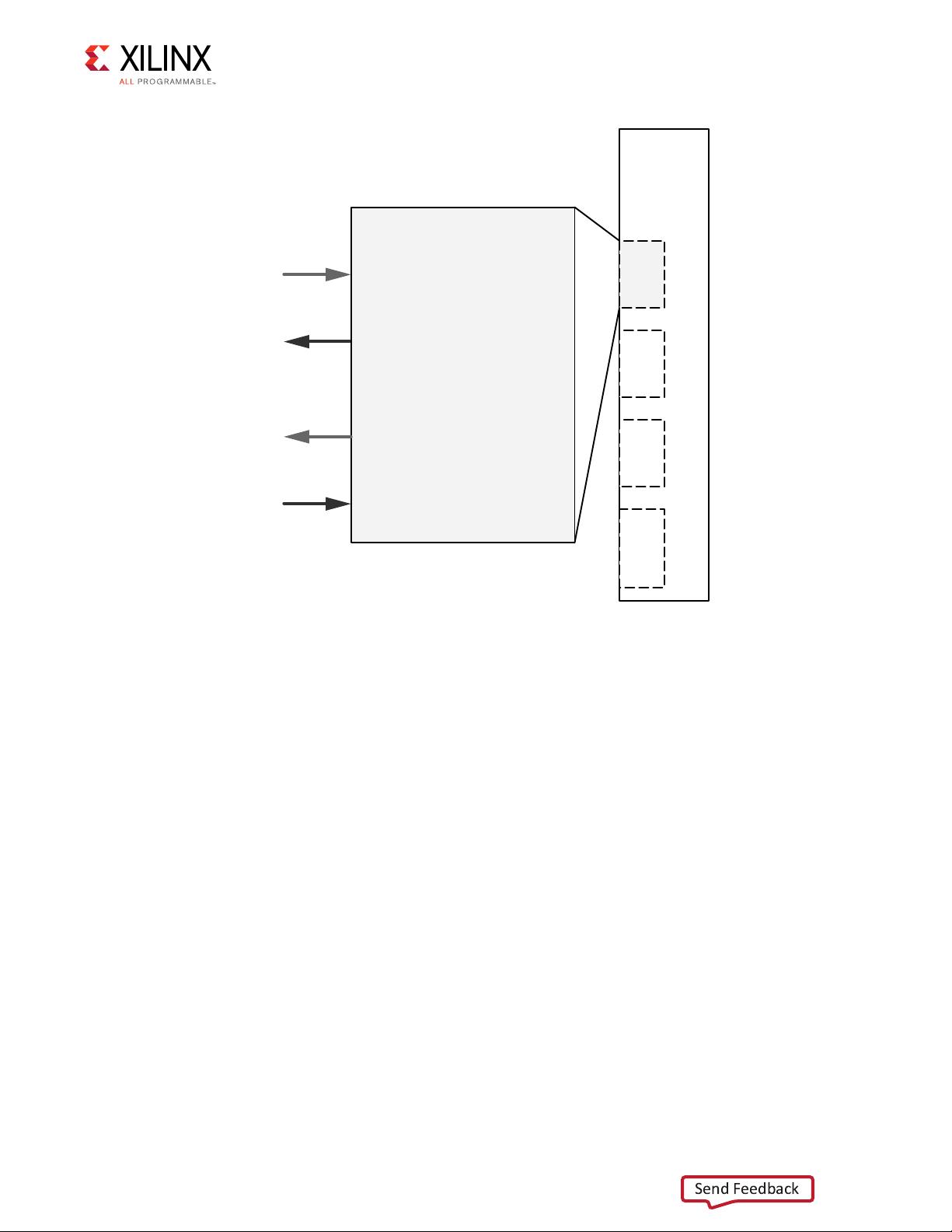

- Top-Level Wrapper:是IP核的顶层封装,用于整合IP核与其他系统组件的接口。

3. **设计指南**:

- 一般设计准则提供了在集成IP核时需要遵循的指导原则,如布线、时钟管理和时序约束。

- 时钟:详细说明了时钟源的选择、同步和管理。

- 重置:解释了IP核如何处理复位信号,以及不同类型的复位对系统稳定性的影响。

- 共享逻辑相关端口描述:描述了多个模块共享逻辑的接口和交互方式。

- 协议描述:详细解析了Serial RapidIO Gen2协议的细节,包括包结构、错误处理等。

4. **设计流程步骤**:

- 自定义和生成IP核的步骤,包括在Xilinx Vivado Design Suite中进行的操作。

- 对IP核进行约束,确保满足系统的时序和性能需求。

- 模拟、综合和实现流程,涵盖了从行为级模拟到硬件实现的全过程。

5. **详细示例设计**:

- 提供了一个具体的例子来演示如何使用这个IP核。

- 包括生成IP核的过程、样例设计的目录结构和文件内容,以及如何实施和验证这个设计。

6. **测试平台**:

- 介绍了用于验证IP核功能的测试平台,这对于确保设计正确性和调试至关重要。

这份文档是针对开发者和工程师的,他们需要在Xilinx FPGA或SoC上实现Serial RapidIO Gen2功能,提供了全面的技术指南和支持,帮助他们有效地利用该IP核进行系统设计和优化。

262 浏览量

213 浏览量

点击了解资源详情

951 浏览量

502 浏览量

1042 浏览量

262 浏览量

945 浏览量

射手Snake357

- 粉丝: 1

- 资源: 12

最新资源

- 商业房产信息网页模板

- competitive_programming

- Libro-Modelos-pedag-gicos-y-strateds-dicicas-en-la-educaci-n-contable-:工具库和模型库

- mail.com Start for Chrome-crx插件

- LoinGoText.rar

- WebViewFileUploadFix:Android WebView 文件上传修复(Agate JavaScript 插件)

- 绿色热门商务培训网页模板

- pact:一个用于加密和解密数据的实验密码应用程序,该应用程序实现了实验密码库MSG

- Barracuda Chromebook Security For BCS-crx插件

- proshop-udemy:那里有很多“电子商务”课程,但是大多数使用某种预先构建的插件或平台。 在本课程中,我们将使用MERN堆栈从头开始构建具有以下功能的完全定制的电子商务购物车应用程序:功能齐全的购物车产品评论和评分顶级产品轮播产品分页产品搜索功能带有订单的用户个人资料管理员产品管理管理员用户管理管理员订单详细信息页面将订单标记为已交付选项结帐流程(运输,付款方式等)PayPal信用卡集成自定义数据库种子脚本

- stunning-octo-enigma

- nosafe-webdosV2.0.rar

- 数码产品网络营销网页模板

- winrt-rust:最终使用Rust并使其最终成为Windows Runtime API

- jquery三环立体式图片切换效果

- My Tabs-crx插件