CPLD基础解析与应用

需积分: 50 197 浏览量

更新于2024-07-24

1

收藏 1.58MB PPT 举报

"CPLD基础教程,涵盖了CPLD的概念、结构、开发软件和编程器设计等内容,对比了CPLD与FPGA的区别,并强调CPLD在控制密集型数字系统设计中的优势。"

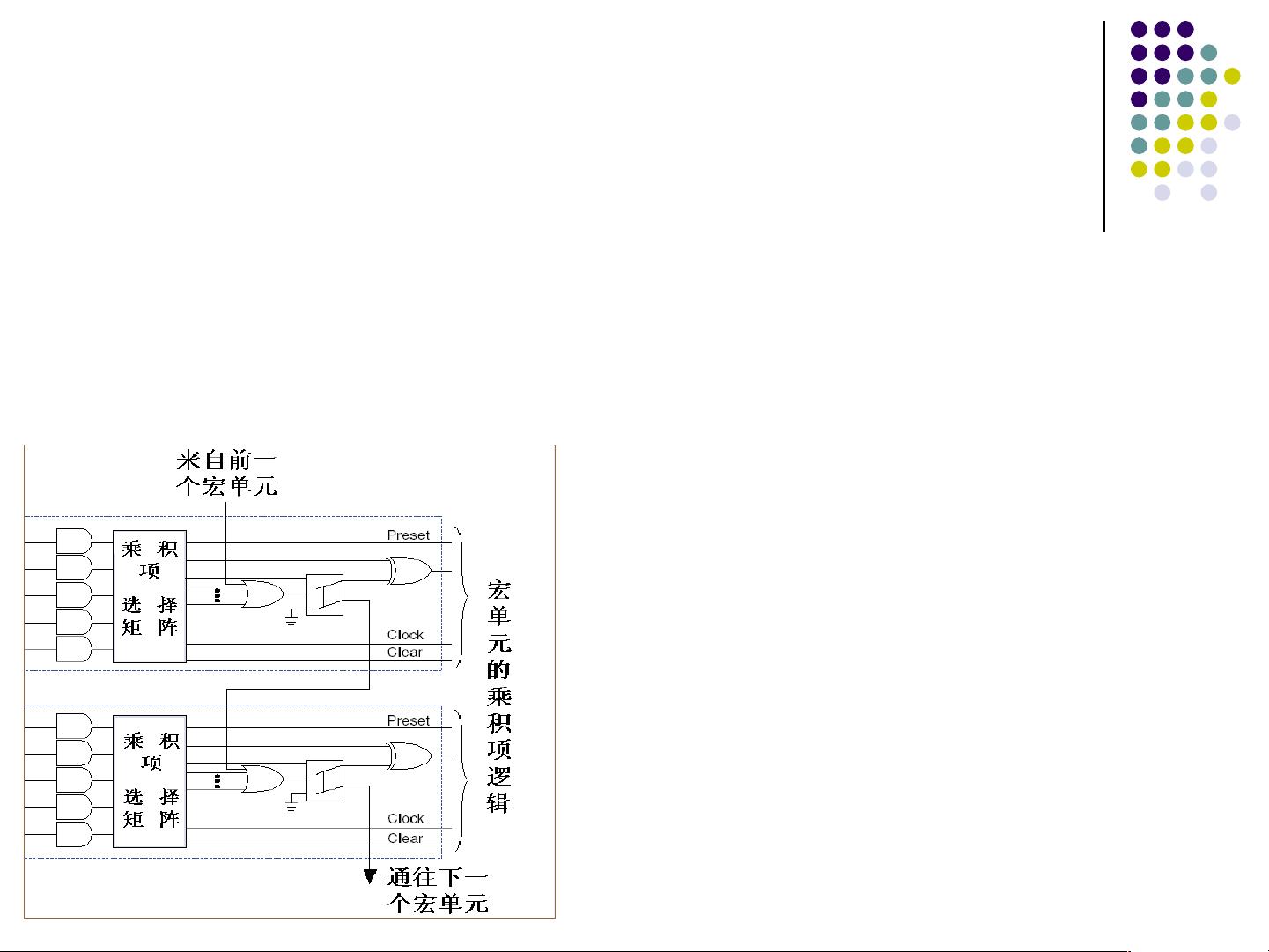

CPLD(Complex Programmable Logic Device),即复杂可编程逻辑器件,是一种大规模集成电路LSI中的专用集成电路ASIC,主要用于控制密集型的数字系统设计,因为它提供了较好的时延控制。CPLD由与或阵列的多PLD组合体构成,这使得它们在设计自由度上相对较低,但门的使用率由电路本身决定,因此在特定应用场景中可以达到较高的效率。

与CPLD相比,FPGA(Field Programmable Gate Array)的逻辑功能块较小,更适合数据密集型系统的处理,但时延设计较为复杂。FPGA的基本结构是单纯的门阵列逻辑组合体,提供更高的设计自由度,但门的使用率由配置配线决定,导致其速度和延迟时间具有较大的不确定性。此外,FPGA的程序存储器通常使用SRAM,这意味着在电源关闭后数据会丢失,而CPLD通常使用Flash或EEPROM,数据在断电后仍能保持。

在延迟时间和动作速度方面,CPLD由于其结构特点,延迟时间相对固定且更容易实现高速化,而FPGA的延迟会因配置配线的不同而变化,高速化实现起来更为复杂。在定时和模拟性能方面,CPLD通常不需要额外的定时考虑,而FPGA由于其灵活性,可能需要更多的定时和模拟设计考虑。适用范围上,CPLD适用于小到中规模的逻辑设计,而FPGA则更适合大规模逻辑设计。

CPLD的开发流程通常包括选择合适的CPLD器件,使用开发软件进行逻辑设计,编写硬件描述语言(HDL,如VHDL或Verilog)代码,通过逻辑综合和布线生成配置文件,最后将配置文件下载到CPLD中。编程器在这一过程中起到关键作用,能够将设计的逻辑信息写入CPLD的存储器中,使其能够执行预定的功能。

对于初学者,理解CPLD的基础知识是进入数字系统设计领域的关键步骤。学习CPLD不仅可以提升对数字逻辑设计的理解,还能为将来可能涉及的FPGA设计打下坚实基础。同时,掌握CPLD的使用可以提高设计效率,特别是在那些对延迟和控制要求严格的项目中,CPLD往往能提供更优的解决方案。

2008-11-04 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

2008-03-29 上传

2019-02-07 上传

海恋星依Fighting

- 粉丝: 3

- 资源: 2

最新资源

- 明日知道社区问答系统设计与实现-SSM框架java源码分享

- Unity3D粒子特效包:闪电效果体验报告

- Windows64位Python3.7安装Twisted库指南

- HTMLJS应用程序:多词典阿拉伯语词根检索

- 光纤通信课后习题答案解析及文件资源

- swdogen: 自动扫描源码生成 Swagger 文档的工具

- GD32F10系列芯片Keil IDE下载算法配置指南

- C++实现Emscripten版本的3D俄罗斯方块游戏

- 期末复习必备:全面数据结构课件资料

- WordPress媒体占位符插件:优化开发中的图像占位体验

- 完整扑克牌资源集-55张图片压缩包下载

- 开发轻量级时事通讯活动管理RESTful应用程序

- 长城特固618对讲机写频软件使用指南

- Memry粤语学习工具:开源应用助力记忆提升

- JMC 8.0.0版本发布,支持JDK 1.8及64位系统

- Python看图猜成语游戏源码发布