实现RISC-CPU系统的VHDL设计方法-基于CPLD技术的可行性验证

版权申诉

DOC格式 | 217KB |

更新于2024-04-04

| 84 浏览量 | 举报

Based on the document "RISCCPU System Design Based on VHDL Language.doc", this project utilizes CPLD as the carrier and utilizes the MAX PLUSⅡ software platform to complete the design of the RISC-CPU system. The paper mainly elaborates on the design method of implementing this IP core using CPLD technology. RISC, which stands for Reduced Instruction Set Computer, simplifies the instruction system compared to general CPUs, and by simplifying the instruction system, the structure of the computer becomes more reasonable, thereby improving the computational speed.

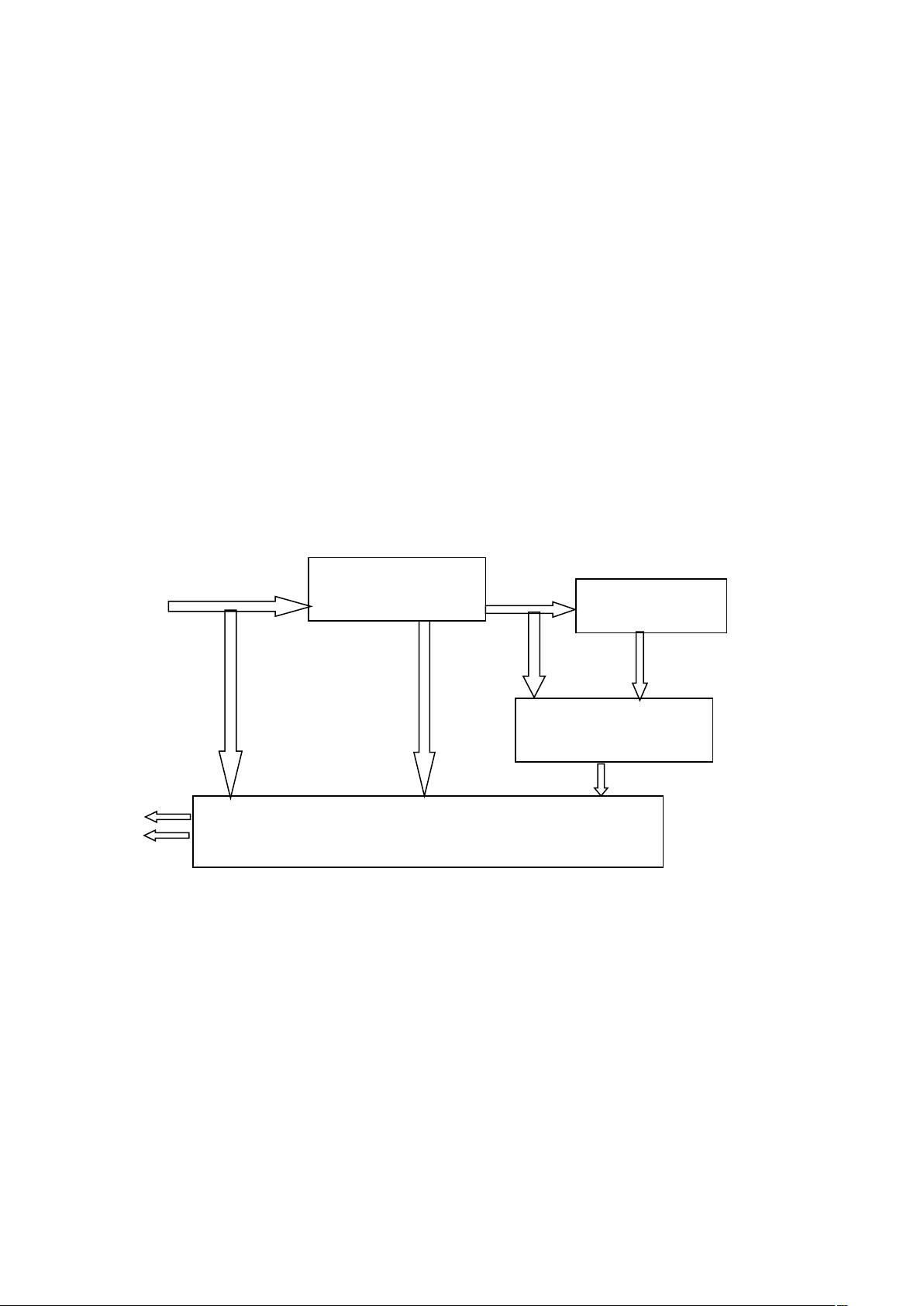

This project designs an 8-bit RISC-CPU system using the hardware description language VHDL and adopts a top-down design method. According to the design process, the RISC-CPU is divided into eight basic functional modules. Then, VHDL code description is applied to each module, and various tools in the development system are used for compilation, functional simulation, logic synthesis, timing simulation, layout, and wiring, ultimately providing simulated waveforms of instruction execution to verify the CPU instruction's functionality. The design demonstrates that the method of implementing RISC-CPU system design using CPLD technology is completely feasible.

Keywords: Complex Programmable Logic Devices, VHDL language, RISC-CPU.

相关推荐

老帽爬新坡

- 粉丝: 99

最新资源

- Qt与QtWebkit打造简易浏览器应用 qt-webkit-kiosk项目介绍

- asp建站高效文件上传下载解决方案

- WebProject增量打包工具使用教程:配置Ant环境

- OpenGL实现三维物体自由旋转技术解析

- 局域网聊天应用:多用户功能与文件传输

- FiveM服务器加载屏:幻灯片过渡设计教程

- Unity 3D游戏开发教程:《泡泡龙》源码解析

- 在Vim中打造个性化状态栏:vim-crystalline插件介绍

- 测试驱动开发学习Emacs Lisp指南

- 安卓抽屉式菜单实现教程与效果展示

- VS环境下的SVN版本控制插件AnkhSvn实用介绍

- Java Struts在线考试系统实现与MySQL数据库集成

- 搭建离线地图服务器:Geoserver实践指南

- rufascube:开源3D魔方滑块拼图 - Ada编写的多平台益智游戏

- Macwire编译时依赖注入在Play Scala项目示例

- 手机仿海王星辰网上药店项目源代码完整分享