Altera CPLD资源优化技术探索

需积分: 10 133 浏览量

更新于2024-08-01

收藏 2.65MB PDF 举报

"self_study_Altera_CPLD的资源优化"

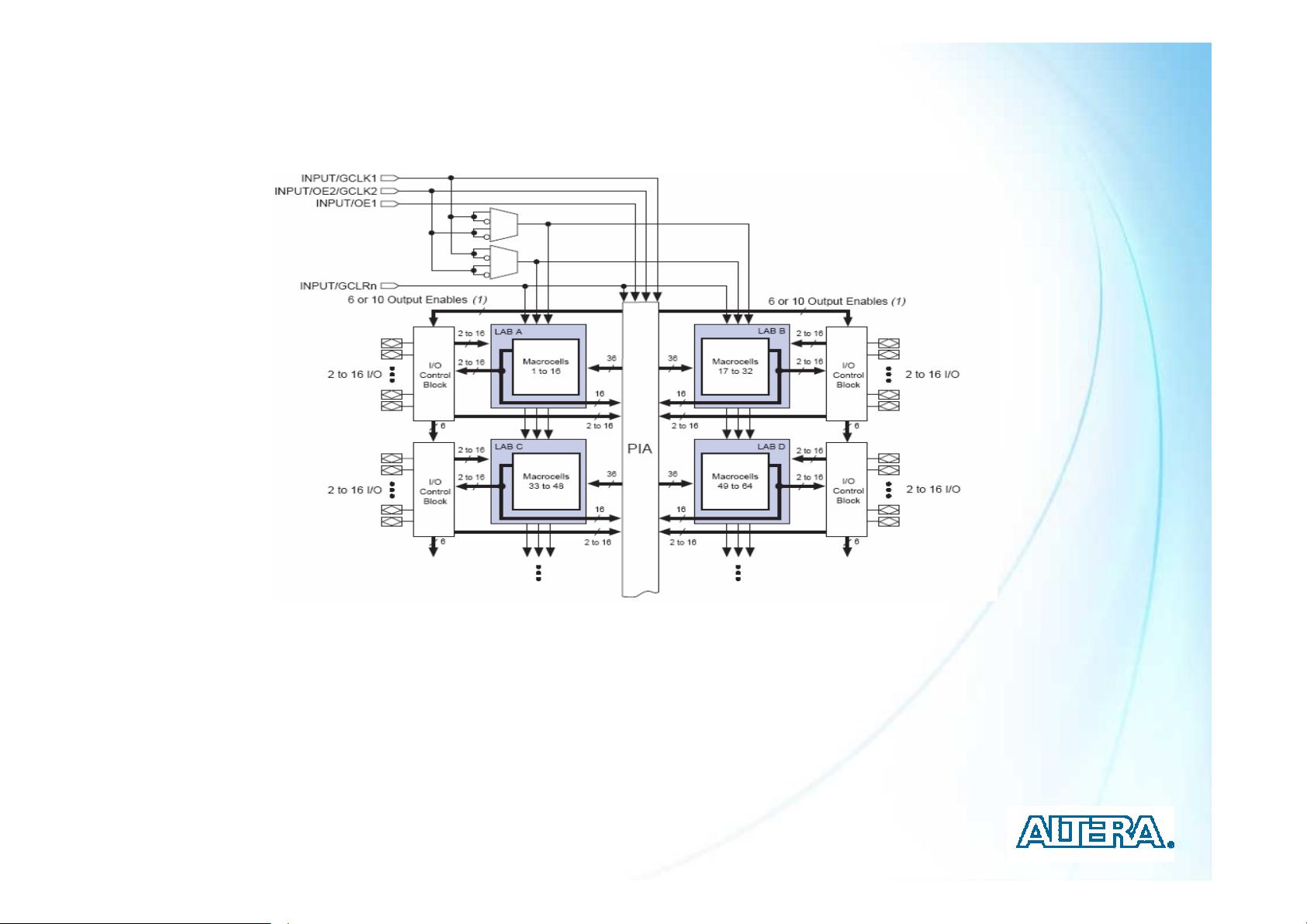

本文档主要探讨了Altera公司CPLD(复杂可编程逻辑器件)的资源优化技术,特别是针对MAX系列设备的优化策略。CPLD是FPGA(现场可编程门阵列)的一种变体,常用于实现中等规模的数字逻辑设计,其优势在于快速的配置和较高的系统集成度。

**MAX Device Architecture**

MAX系列CPLD由多个宏单元(Macrocell)组成,每个宏单元可以配置为各种逻辑功能,如触发器、组合逻辑门等。这些宏单元通过内部互连网络连接,形成用户自定义的逻辑结构。了解MAX设备的架构是优化资源利用的关键。在设计中,合理布局宏单元和路由资源能有效提高性能和减少功耗。

**Resource Optimization Techniques**

1. **Macrocell Utilization**: 优化宏单元的使用是提高CPLD效率的重要途径。设计师应避免浪费宏单元资源,确保每个宏单元都被充分利用。这可能包括将多个简单逻辑功能整合到一个宏单元中,或利用宏单元内的寄存器和逻辑门来实现更复杂的逻辑。

2. **Routing Resource Utilization**: 路由资源优化涉及如何有效地分配和使用布线资源,以降低延迟和提高信号完整性。这包括合理规划逻辑模块的位置,以及使用适当的布线策略,比如使用全局布线资源来连接关键路径。

3. **逻辑综合与布局布线**: 使用Altera的 Quartus II工具进行逻辑综合和布局布线时,可以设置不同的优化选项,如减小逻辑深度、提高时钟速度等,以达到最佳的资源利用。

4. **资源共享**: 在设计中尽可能地重复使用相同的逻辑功能,避免复制冗余的逻辑模块,从而减少资源占用。

5. **时序分析与约束设定**: 通过时序分析,可以识别出可能导致性能瓶颈的部分,并对设计进行相应调整。同时,设定合理的时序约束可以帮助优化工具更好地分配资源。

6. **Power Management**: 优化电源管理策略,例如使用低功耗模式、按需唤醒等功能,可以在不牺牲性能的前提下降低整体功耗。

**Conclusion**

通过对MAX系列CPLD的资源优化,设计者可以实现更高效、更快、更节省成本的设计。理解设备架构、掌握优化技巧并利用好设计工具,是提升CPLD设计质量和性能的关键步骤。在实践中不断学习和调整,是成为优秀CPLD/FPGA设计师的必经之路。

**Appendix**

文档的附录部分可能包含更多具体的实例、案例研究或详细的优化指导,以帮助读者深入理解并应用上述理论知识。

对于自学Altera CPLD的初学者来说,这份资料提供了一个良好的起点,指导如何最大化利用CPLD的资源,解决宏单元使用和路由问题,提升设计效率。通过实践这些优化技术,可以提升设计能力,更好地应对各种复杂的数字逻辑设计挑战。

2019-09-12 上传

2019-02-25 上传

2022-07-15 上传

2022-09-23 上传

2022-08-03 上传

2022-09-21 上传

2022-07-15 上传

2022-09-24 上传

zpf007

- 粉丝: 1

- 资源: 2

最新资源

- 掌握Jive for Android SDK:示例应用的使用指南

- Python中的贝叶斯建模与概率编程指南

- 自动化NBA球员统计分析与电子邮件报告工具

- 下载安卓购物经理带源代码完整项目

- 图片压缩包中的内容解密

- C++基础教程视频-数据类型与运算符详解

- 探索Java中的曼德布罗图形绘制

- VTK9.3.0 64位SDK包发布,图像处理开发利器

- 自导向运载平台的行业设计方案解读

- 自定义 Datadog 代理检查:Python 实现与应用

- 基于Python实现的商品推荐系统源码与项目说明

- PMing繁体版字体下载,设计师必备素材

- 软件工程餐厅项目存储库:Java语言实践

- 康佳LED55R6000U电视机固件升级指南

- Sublime Text状态栏插件:ShowOpenFiles功能详解

- 一站式部署thinksns社交系统,小白轻松上手