系统时钟源选择:晶体振荡器与高性能PLL的权衡与发展

需积分: 15 185 浏览量

更新于2024-09-29

收藏 652KB PDF 举报

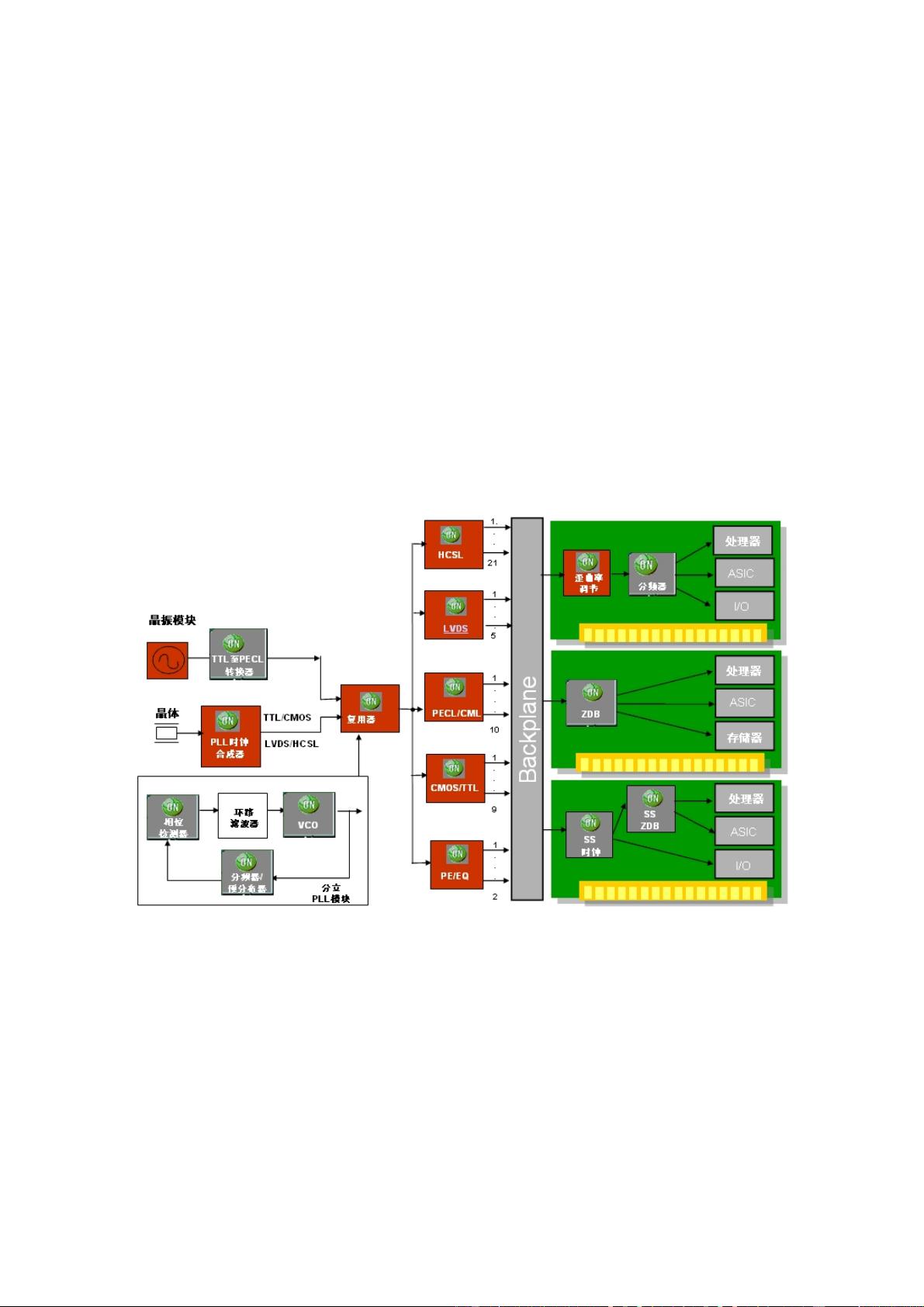

"本文探讨了系统时钟源的选择与高性能PLL的发展趋势,重点关注了晶体振荡器(XO)和锁相环(PLL)合成器的比较。时钟源的性能对电子系统的整体性能至关重要,而复杂的系统设计可能需要多种时钟信号。文中提到,晶振模块通常基于石英晶体谐振器,利用压电效应工作,而PLL则能实现频率合成和倍频。晶体振荡器的频率精度以PPM偏差表示,更精确的振荡器成本更高。"

在电子系统设计中,系统时钟源起着至关重要的作用,因为它决定了系统的运行速度和稳定性。时钟信号的产生通常涉及振荡器源、逻辑电平转换和时钟分配。晶体振荡器(XO)是最常见的时钟源之一,它使用石英晶体作为谐振元件,通过压电效应产生稳定的振荡。石英晶体在电场作用下会发生机械变形,反之亦然,这种现象使得晶体能够产生精确的振荡频率。晶体振荡器的频率精度通常以每百万分之几的偏差(PPM)来衡量,更精确的振荡器可能会有更高的成本。

另一方面,锁相环(PLL)是一种频率合成器,它可以实现频率的倍频和分频,以适应不同的系统需求。PLL通过锁定到输入参考信号的相位,可以产生与输入信号同步的精确输出频率。这种灵活性使得PLL在需要多个频率或者需要快速频率切换的系统中非常有用。然而,与晶体振荡器相比,PLL通常会引入更多的相位噪声和抖动,这可能对某些高精度应用造成影响。

随着技术的发展,高性能PLL正朝着更低功耗、更高频率稳定性和更小封装尺寸的方向发展。这包括采用先进的工艺技术来提高电路的集成度,以及引入数字控制算法来优化相位噪声性能。此外,PLL的设计也在考虑如何更好地抑制噪声,减少抖动,以满足高速通信、数据中心和高性能计算等领域的严格要求。

在系统时钟源的选择上,设计师需要平衡精度、稳定性和成本等因素。晶振模块提供高精度但可能较贵,而PLL可以提供更多的频率灵活性但可能带来额外的相位噪声。在复杂系统中,可能需要结合使用两者,例如,使用晶体振荡器作为基本时钟源,通过PLL进行频率转换和分配,以满足各种组件的需求。

系统时钟源的比较选择和高性能PLL的发展趋势是电子工程领域的重要研究方向,它们对确保系统性能、可靠性和效率具有决定性的影响。随着技术的进步,我们可以期待未来出现更多创新的时钟解决方案,以满足不断增长的高速、低功耗和高精度时序需求。

214 浏览量

118 浏览量

点击了解资源详情

132 浏览量

2022-10-12 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

289 浏览量

zh_h77

- 粉丝: 0

- 资源: 5

最新资源

- 极速PE u盘启动盘制作工具(xp内核) v6.1

- ember-cli-webcomponents-bundler:使用ES6模块捆绑Web组件

- 行业文档-设计装置-阶梯式弧形看台现浇装饰板的模板支撑体系及构建方法.zip

- Imperial Realms Standard Client-开源

- 2020TI杯模拟电子系统邀请赛现场u盘内容 包络电源

- Racer对Emacs的支持—自动完成(另请参阅公司和自动完成)-Rust开发

- gpsDataLogger-开源

- python 碎图合成脚本 附带说明文档

- 领域自适应文本挖掘工具(新词发现、情感分析、实体链接等),基于少量种子词和背景知识

- scripts:波格

- 行业文档-设计装置-一种平台.zip

- FJSP算例转化程序,需要指定文件位置带后缀的,xls,除了MK算例不能转化外,其他的算例都能转化

- 算法:算法문제풀이

- jql-JSON查询语言CLI工具-Rust开发

- Mobile_App_Look-Feel

- PYNQ-Z1中文入门指导手册及示例程序