Mapping Granularity Adaptive FTL

Based on Flash Page Re-programming

Yazhi Feng, Dan Feng, Chenye Yu, Wei Tong

‡

, Jingning Liu

‡

,

Wuhan National Lab for Optoelectronics, School of Computer Science and Technology

Huazhong University of Science and Technology, Wuhan, China

{fengyazhi, dfeng, yuchenye, Tongwei, jnliu}@hust.edu.cn

‡

Co-corresponding authors: Wei Tong (Tongwei@hust.edu.cn) and JingningLiu (jnliu@hust.edu.cn)

Abstract—The page size of NAND flash continuously grows

as the manufacturing process advances. While larger page can

reduce the cost per bit and improve the throughput of NAND

flash, it may waste the storage space and data transfer time.

Meanwhile, it causes more frequent garbage collections when

serving small write requests. To address the issues, we proposed

a Mapping Granularity Adaptive FTL (MGA-FTL) based on

flash page re-programming feature. MGA-FTL enables a finer

granularity NAND flash space management and exploits multiple

subpage writes on a single flash page without erase. 2-Level

Mapping is introduced to serve requests of different sizes in

order to control the overhead of DRAM requirement. Meanwhile,

the allocation strategy determines whether different logical pages

can be mapped to a single physical page to balance the space

utilization and performance. Subpage merging limits the number

of associated physical pages to a logical page, which could

reduce data fragmentation and improves the performance of

read operations. We compared MGA-FTL with some typical

FTLs, including page-level mapping FTL and sector-log mapping

FTL. Experimental results show that MGA-FTL reduces the I/O

response time, write amplification and the number of erasures by

53%, 30% and 40% respectively. Despite the overhead of fine-

grained management, MGA-FTL increases no more than 16.5%

DRAM requirement compared with a page-level mapping FTL.

Unlike the subpage-level mapping, MGA-FTL only needs one

third of DRAM space for storing mapping tables.

I. INTRODUCTION

With the advance in flash memory manufacturing process,

the storage density of NAND flash chip has been increased in

many folds. The basic read and write unit of flash is a flash

page, whose size is continuously growing from 512 bytes to

4KB and 8KB. Table shows the evolution of the chip capacity

and page size of NAND flash memory [1]. Now some flash

chips with 16KB pages have already been shipped. Recently,

3D NAND Flash memories have been introduced to keep the

trend of increasing bit density with the potential to scale up

to several Terabits. However, 3D flash memory devices face

the problem of big blocks [2]. A large block might consist

of a large number of pages or the pages with large size. So

the page size may continue increasing even larger in the near

future. In order to reduce the cost of bit, solid-state drive

(SSD) manufacturers are increasingly likely to choose the

large-capacity and high-density flash memory chips, which

degrades the lifetime and performance when serving small

updates.

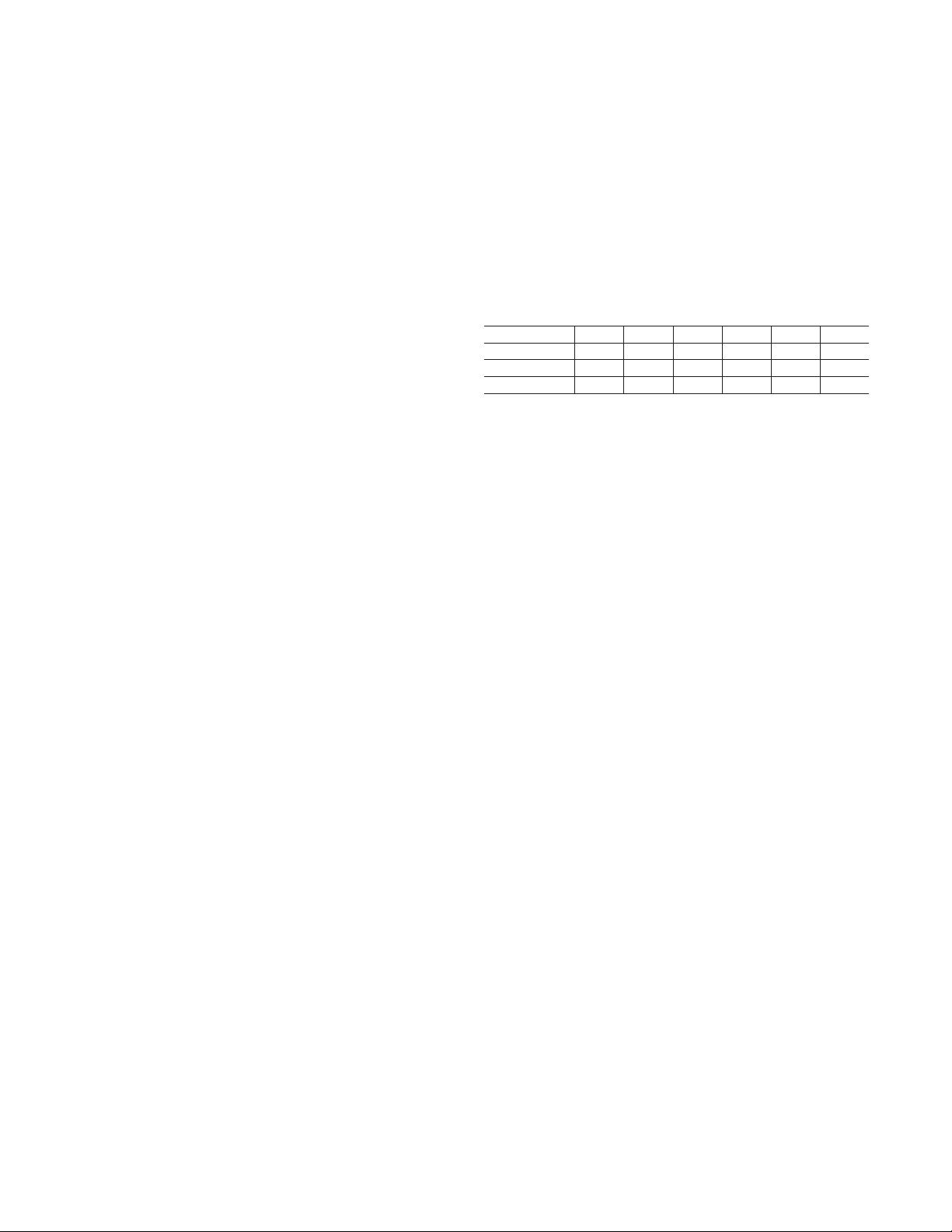

TABLE I: Evolution of NAND Flash Page Size

2006 2007 2008 2009 2010 2014

Process 90nm 72nm 50nm 34nm 25nm 16nm

Chip Capacity 2Gb 8Gb 16Gb 32Gb 64Gb 128Gb

Page Size 2KB 2KB 4KB 4KB 8KB 16KB

Flash Translation Layer (FTL) is used in SSDs to emulate

the Hard Disk Drive (HDD) interface. Thus, most file systems

can be directly used on SSD without any changes. However,

the default block size of file systems such as NTFS [3] and

ext4 [4] is 4KB. Flash pages are several times the size of

File System Blocks (FSBs). For example, if the flash page

size is 16KB, it needs four 4KB FSBs to fill up a full page.

When updating 4KB data in a flash page, 16KB old data in

the entire page need to be read, merged with the updated data

and then written to a new flash page. These operations cause

a lot of extra page read, write and erase cost which wastes the

data transfer time, resulting in significant performance loss and

lifetime degradation.

To address the above issues, an intuitive way is to manage

all flash pages at the granularity of subpages (the same size

of FSBs). However, the subpage mapping table entries will

increase several times of page-level mapping and the cost of

DRAM is unacceptable, e.g., 1 TB device with 16KB pages

and 4KB subpages needs 2GB storage space for mapping

tables. On the other hand, the past work of subpage-level

mapping [5] only supports to write part of a page, and

leads to a low space utilization. We took advantages of the

characteristics of the underlying hardware to make full use of

the entire flash page.

In this study, we present the Mapping Granularity Adaptive

Flash Translation Layer (MGA-FTL). We focus on the impact

of large flash pages to the I/O performance and lifetime of

SSDs. MGA-FTL manages SSDs in different granularities,

writes small requests into subpages and serves large requests

with entire flash pages. MGA-FTL makes use of the page

re-programming feature of flash to achieve higher page uti-

lization. In contrast with other design [6], Subpage merging

operations is not necessary in our work and the DRAM

requirement of mapping tables is carefully controlled.

The rest of this paper is organized as follows. Section II

describes the background. The details of MGA-FTL design

are presented in section III and we describe the evaluation in

374

978-3-9815370-8-6/17/$31.00

c

2017 IEEE