Vivado高阶综合指南:UG902 v2018.3更新

需积分: 9 110 浏览量

更新于2024-07-15

收藏 6.54MB PDF 举报

"0 ug902-vivado-high-level-synthesis.pdf"

Vivado Design Suite用户指南聚焦于高层面综合(HLS),这是一款强大的工具,用于将高级编程语言如C、C++或SystemC的算法直接转换为FPGA(现场可编程门阵列)的硬件描述语言(如VHDL或Verilog)。该文档是UG902的2018.3版,更新日期为2018年12月20日,提供了关于如何使用Vivado HLS进行设计优化和调试的详细指导。

1. **修订历史**:文档的修订历史显示了2018年12月20日的2018.3版本更新,主要涉及了Schedule Viewer、数据流优化、C++任意精度固定点类型、HLS数学库、HLS视频库、HLSSQL库、系统调用以及数组处理等方面的改进和信息更新。

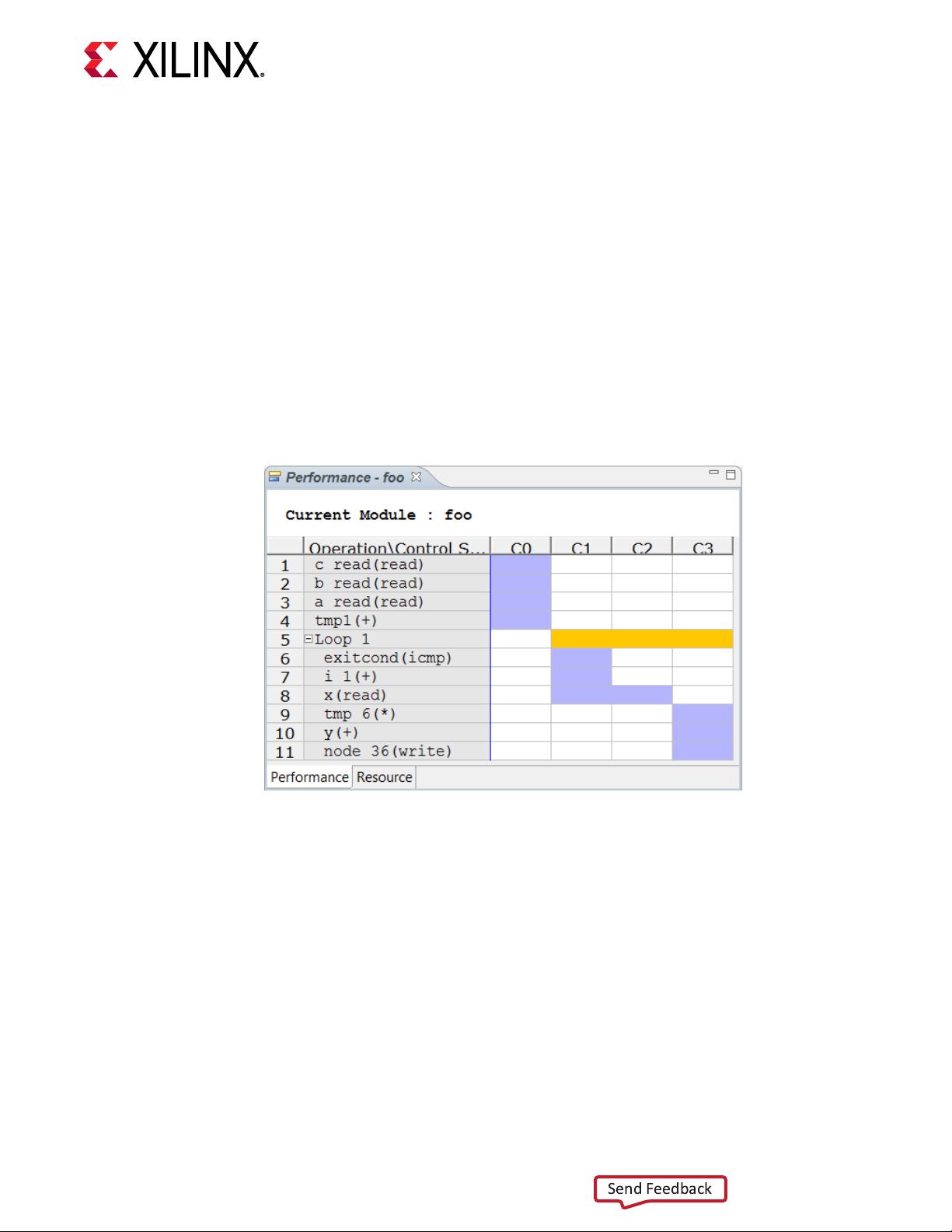

2. **Schedule Viewer**:这部分内容更新了关于Schedule Viewer的使用信息,Schedule Viewer是一个重要的工具,它帮助用户理解代码在硬件中的执行顺序,以进行性能优化。

3. **优化设计**:文档澄清了数据流和循环优化的细节,这是HLS中提升设计效率的关键技术,允许在硬件中并行执行任务,以提高FPGA的运行速度。

4. **C++任意精度固定点类型**:新增了关于使用头文件的注释,固定点类型在FPGA设计中常用于模拟浮点运算,以节省资源并保持计算精度。

5. **HLS数学库**:更新了如何使用hls_math.h头文件的信息,并对固定点数学函数进行了更新,这些函数提供了一套丰富的数学操作,适用于硬件实现。

6. **HLS视频库和HLS Video Functions Library**:HLS视频库已迁移到Xilinx的GitHub仓库(https://github.com/Xilinx/xfopencv),便于开发者获取和协作。

7. **HLSSQL库和HLSSQL Library Functions**:更新了hls::dbtohls::alg函数,使得SQL操作在FPGA上实现成为可能。

8. **系统调用**:增加了关于使用__SYNTHESIS__宏的信息,这个预处理器宏用于指示哪些代码段应该在硬件综合过程中保留。

9. **数组**:详细介绍了数组大小的行为,这对于理解硬件资源分配和内存管理至关重要。

10. **命令参考**:更新了命令参考部分,包括config_dataflow和config_rtl命令,其中添加了禁用start_propagation选项,这允许用户更精细地控制数据流优化过程。

11. **类方法、运算符和数据成员**:对于指定数据类型的指导也有所增加,帮助开发者理解和使用类、方法、运算符和数据成员来构建复杂的设计。

Vivado HLS通过简化FPGA设计流程,使软件工程师也能参与到硬件设计中,降低了FPGA开发的门槛,同时也提高了设计效率。这份用户指南详细阐述了如何充分利用这一工具,实现高效且优化的FPGA设计。无论是初学者还是经验丰富的开发者,都能从中获得宝贵的指导和洞察。

2019-06-12 上传

2021-08-09 上传

113 浏览量

2021-10-11 上传

2023-08-01 上传

2020-08-13 上传

2021-09-11 上传

MIScripture

- 粉丝: 3

- 资源: 192

最新资源

- 火炬连体网络在MNIST的2D嵌入实现示例

- Angular插件增强Application Insights JavaScript SDK功能

- 实时三维重建:InfiniTAM的ros驱动应用

- Spring与Mybatis整合的配置与实践

- Vozy前端技术测试深入体验与模板参考

- React应用实现语音转文字功能介绍

- PHPMailer-6.6.4: PHP邮件收发类库的详细介绍

- Felineboard:为猫主人设计的交互式仪表板

- PGRFileManager:功能强大的开源Ajax文件管理器

- Pytest-Html定制测试报告与源代码封装教程

- Angular开发与部署指南:从创建到测试

- BASIC-BINARY-IPC系统:进程间通信的非阻塞接口

- LTK3D: Common Lisp中的基础3D图形实现

- Timer-Counter-Lister:官方源代码及更新发布

- Galaxia REST API:面向地球问题的解决方案

- Node.js模块:随机动物实例教程与源码解析