FPGA实现的不恢复余数阵列除法器设计

"不恢复余数阵列除法器的FPGA实现"

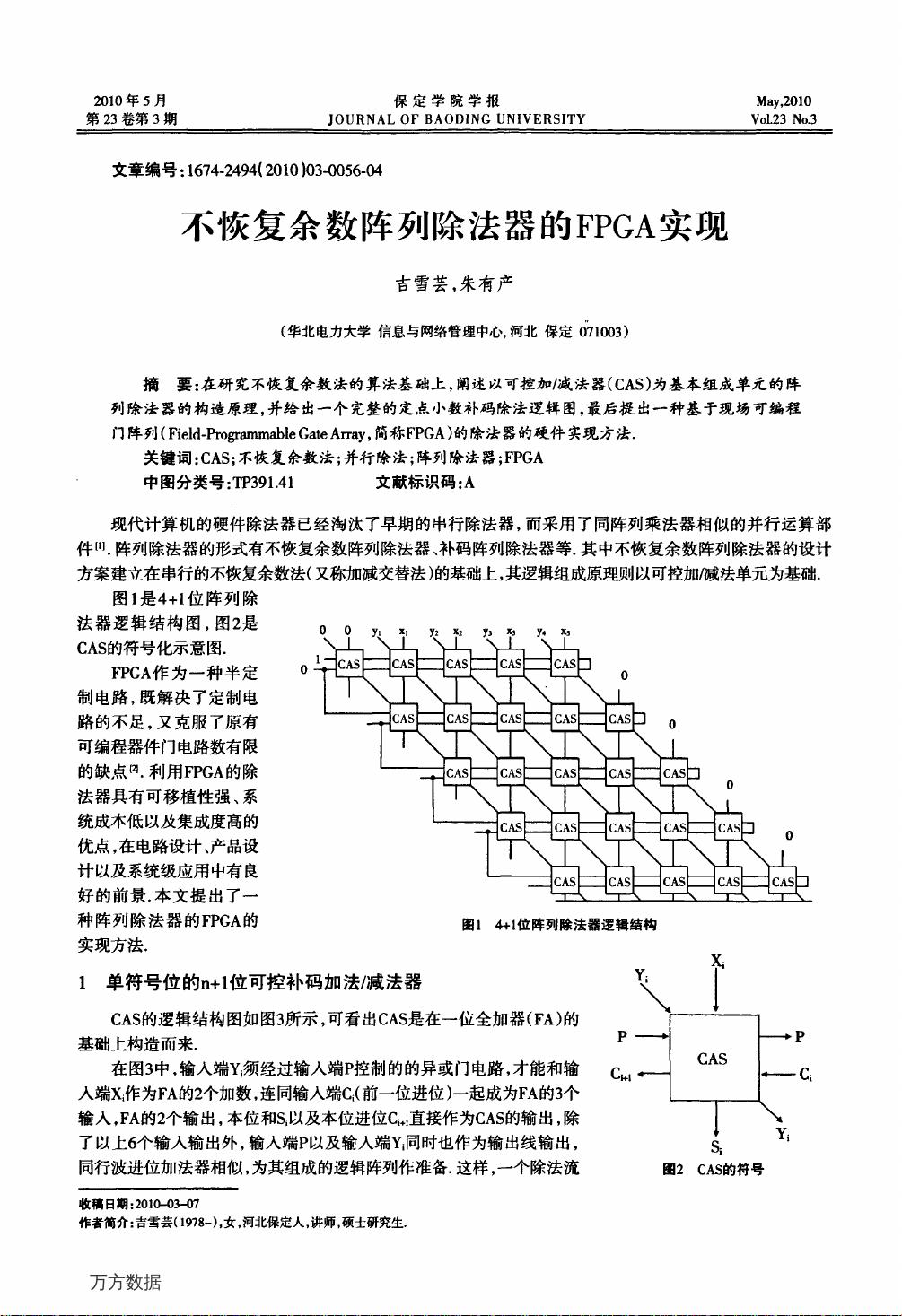

本文主要探讨了不恢复余数法在FPGA实现中的应用,这是一种用于快速并行除法的算法。不恢复余数法,又称加减交替法,是基于串行除法的一种改进策略,通过在每次迭代中交替进行加法和减法操作来逐步逼近商。这种算法的关键在于可控加/减法器(CAS),它是构建阵列除法器的基础。

阵列除法器的结构通常包含多个并行运行的CAS单元,每个单元负责处理一个位的计算。例如,一个4+1位的阵列除法器由四个CAS单元构成,它们并行工作以提高运算速度。CAS单元基于一位全加器(FA)扩展而成,可以执行加法或减法,具体取决于输入控制信号P。当P为1时,执行加法;P为0时,执行减法。CAS的输出包括本位和Si、本位进位Ci'以及输入Y和P的输出,这些输出对于构建更复杂的阵列逻辑至关重要。

FPGA,即现场可编程门阵列,是实现这种复杂逻辑的理想平台。它提供了高度灵活的硬件配置能力,可以根据设计需求进行定制,同时克服了传统可编程逻辑器件的局限。FPGA的使用使得除法器设计可移植性强,系统成本降低,并且可以实现高集成度。这在电路设计、产品开发以及系统级应用中具有显著优势。

通过FPGA实现的不恢复余数阵列除法器,可以有效地加速除法运算,尤其适用于需要高效算术运算的领域,如数字信号处理、加密算法、浮点运算等。在现代计算机系统中,硬件除法器的性能直接影响到整体系统的计算效率,因此,优化除法器设计,特别是采用并行化方法,对于提升计算机性能具有重要意义。

在实际设计过程中,设计师需要考虑FPGA资源的利用率,逻辑门的布局和布线,以及功耗和时序约束等因素。通过精心设计和优化,可以实现高性能、低功耗的除法器IP核,该核心可以被嵌入到更复杂的系统芯片(SoC)中,以满足特定应用的需求。

不恢复余数阵列除法器的FPGA实现是提高计算效率和系统性能的有效途径,而CAS作为核心组件,是实现这一目标的关键。通过深入理解和巧妙利用FPGA的特性,可以构建出高效、可扩展的除法解决方案,以应对日益增长的高速数据处理需求。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-07-13 上传

点击了解资源详情

2024-11-03 上传

2009-07-02 上传

2021-09-16 上传

点击了解资源详情

wb2009_happy

- 粉丝: 1

- 资源: 26

最新资源

- Codeforces Enhancer-crx插件

- 5.03.Heat2D:偏二氟乙烯

- donnakevin.wedding:唐娜卡特和凯文露的婚礼网站

- DBD.js-bot:我正在制作一个简单的DBD.js多用途机器人

- Lineage-P9-DB

- nodejsconcepts

- Adafruit_ILI9341:Adafruit ILI9341显示库

- JavaEE课程设计.zip

- 验尸:验尸的集合。 抱歉,合并PR的延迟!

- googlemirror.net

- netfox-api:NetFox cocos2dx前端API

- litten.love:(✿◠‿◠)

- UiPath-GuessNumberUsingStateMachine

- OS-Lab-Implementation:包含OS Labs的C代码

- Bitbucket Diff Tree-crx插件

- 敖德萨:您的股票市场预测顾问