Xilinx Virtex 7 FPGA时钟资源用户指南

"Xilinx Virtex 7系列FPGA的开发技术指导书1,着重介绍了7Series FPGAs的时钟资源,包括用户指南UG472(v1.3),发布日期为2011年10月27日。"

Xilinx的Virtex 7系列FPGA是高性能、高密度的可编程逻辑器件,广泛应用于通信、计算、汽车、医疗等多个领域。该开发技术指导书的第一部分主要关注的是时钟资源,这是FPGA设计中的关键组成部分,对系统的性能、功耗和稳定性具有重大影响。

1. **时钟资源**:

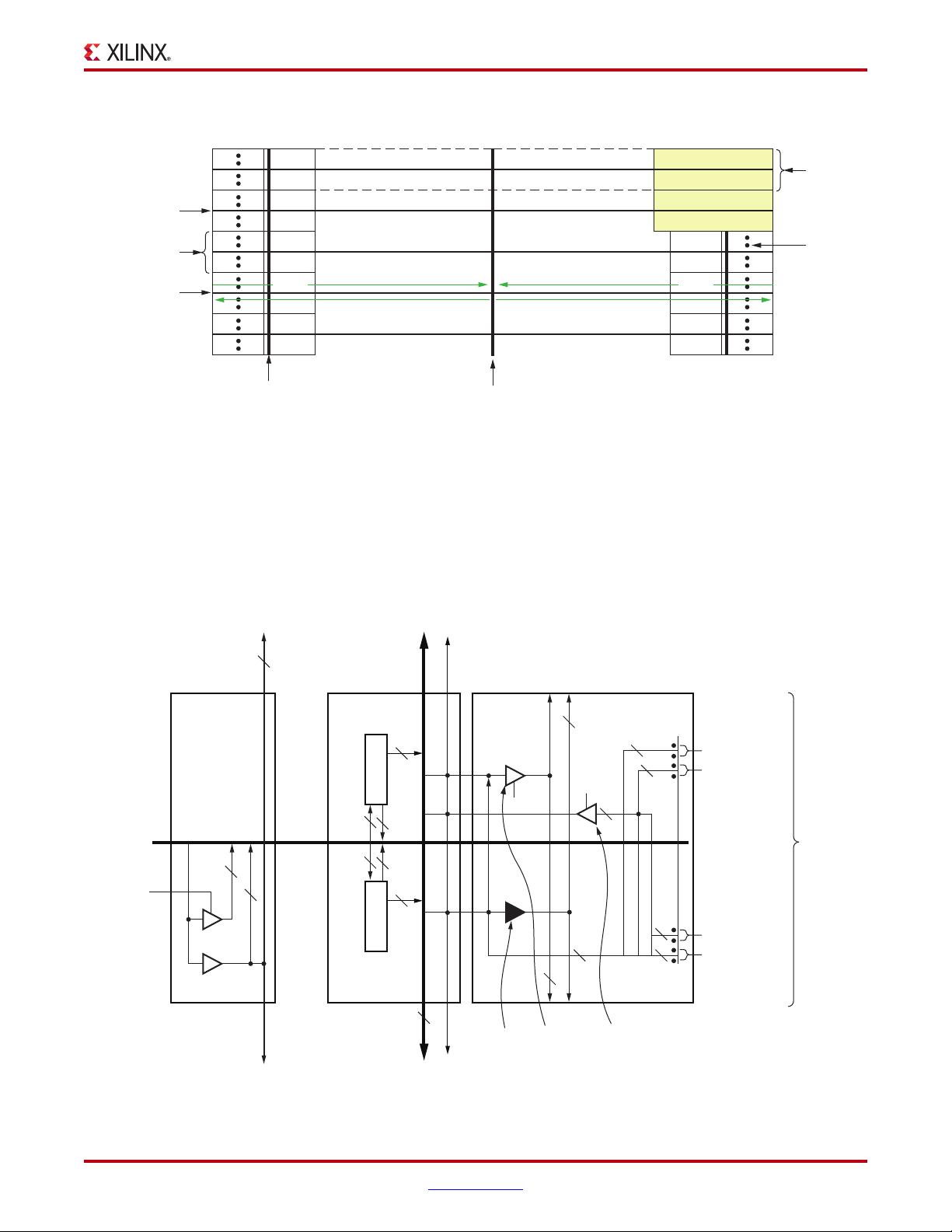

- **时钟网络**:7Series FPGAs拥有复杂的时钟网络,能够支持多种时钟分发和管理策略,包括全局时钟、分布式时钟和区域时钟等,确保信号在整个芯片上的同步。

- **时钟管理模块 (Clock Management Tiles, CMT)**:CMT是Xilinx 7系列FPGA中处理时钟路由和频率转换的核心组件,可以实现频率合成、分频、倍频以及相位锁定等功能。

- **时钟缓冲器**:时钟缓冲器用于将主时钟信号分发到FPGA的不同部分,确保信号质量并减少时钟 skew。

2. **时钟树综合 (Clock Tree Synthesis, CTS)**:

- 在设计流程中,CTS是优化时钟路径延迟的关键步骤,它确保所有时钟域的时钟信号到达时间一致,从而提高系统性能和时序收敛。

- CTS还可以通过平衡时钟路径来降低时钟抖动,提升系统稳定性。

3. **低功耗设计**:

- 7Series FPGAs提供了动态电源管理功能,如时钟门控和时钟分区,可以在不使用某些逻辑块时关闭对应的时钟,从而降低功耗。

- 另外,还有可编程电压岛,允许根据工作负载调整部分电路的电压,进一步节能。

4. **时钟质量和性能**:

- Xilinx 7系列FPGA支持高级时钟质量指标,如抖动性能和相位噪声,这些指标对于高速数字接口(如PCIe、SerDes)的正确运行至关重要。

- 设计者需要关注时钟的Jitter预算,确保系统满足严格的时序要求。

5. **知识产权 (IP) 集成**:

- 7Series FPGAs的时钟资源也支持多种硬核IP,如嵌入式处理器、存储器控制器和接口IP,它们通常有自己的时钟需求,需要与全局时钟网络进行适配。

6. **设计注意事项**:

- 使用Xilinx的开发工具 Vivado 或 ISE 进行设计时,需充分理解时钟约束的设置,确保正确配置时钟资源。

- 对于多时钟域的设计,必须处理好时钟域间的同步问题,防止数据竞争和 metastability。

7Series FPGAs的时钟资源用户指南提供了关于如何有效利用和管理这些资源的详细信息,对于成功开发高效、低功耗的FPGA系统至关重要。设计师需要深入理解时钟网络的特性,并遵循最佳实践来优化设计性能。

1207 浏览量

311 浏览量

1643 浏览量

314 浏览量

135 浏览量

152 浏览量

174 浏览量

ouyang_78oyjs

- 粉丝: 0

最新资源

- 全面详实的大学生电工实习报告汇总

- 利用极光推送实现App间的消息传递

- 基于JavaScript的节点天气网站开发教程

- 三星贴片机1+1SMT制程方案详细介绍

- PCA与SVM结合的机器学习分类方法

- 钱能版C++课后习题完整答案解析

- 拼音检索ListView:实现快速拼音排序功能

- 手机mp3音量提升神器:mp3Trim使用指南

- 《自动控制原理第二版》习题答案解析

- 广西移动数据库脚本文件详解

- 谭浩强C语言与C++教材PDF版下载

- 汽车电器及电子技术实验操作手册下载

- 2008通信定额概预算教程:快速入门指南

- 流行的表情打分评论特效:实现QQ风格互动

- 使用Winform实现GDI+图像处理与鼠标交互

- Python环境配置教程:安装Tkinter和TTk