Verilog HDL实现的蜂鸣器乐曲演奏电路设计

"基于蜂鸣器的自动乐曲演奏"

本文将探讨一个使用Verilog HDL设计的音乐发生器电路,该电路能够基于蜂鸣器自动演奏乐曲。设计的核心是通过控制音调和音长,精确地生成对应的频率信号,从而实现动听的音乐播放。音调的高低取决于信号的频率,而不同频率的信号都是通过基准频率分频得到的。由于音阶的频率通常是非整数,因此在实际设计中,需要将计算出的分频系数四舍五入取整。选择基准频率时,需要平衡频率误差和分频数的大小,以确保演奏的准确性。

设计过程中,团队成员包括刘鹏、李永权和刘凯,他们按照一系列步骤进行,包括功能性仿真、布局布线、综合、时序分析以及时序仿真。设计的目标是利用FPGA(Field-Programmable Gate Array)来产生特定音符频率的方波信号,同时考虑到乐曲的速度和每个音符的节拍,确定音符的持续时间。

课程设计的主要目的是加深对EDA技术的理解,掌握乐曲演奏电路的工作原理,并通过Verilog HDL实现乐曲的自动循环演奏。此外,设计者还需要具备自主学习和问题解决的能力。具体要求是使用Verilog HDL设计电路,通过分频控制方式,实现音乐的播放,并确保乐曲结束后能自动重头开始演奏。

乐曲演奏的基本原理是控制激励信号的频率和持续时间。每个音符的频率(音调)和持续时间(音长)是构成连续乐曲的关键。通过调整发送到扬声器的信号频率和持续时间,可以使得扬声器发出连续的音乐。相比于使用微处理器(CPU)实现,纯硬件的乐曲演奏电路设计更为复杂,但借助现代的EDA工具和硬件描述语言,如Verilog HDL,使得这一过程变得可能。

在实现基于FPGA的乐曲自动演奏器设计时,需要考虑如何有效地控制激励信号的频率和持续时间,以及如何在乐曲结束时无缝衔接回开头。这种设计的优势在于它能够实时生成音乐信号,无需软件干预,因此在实时性和效率上具有优势。

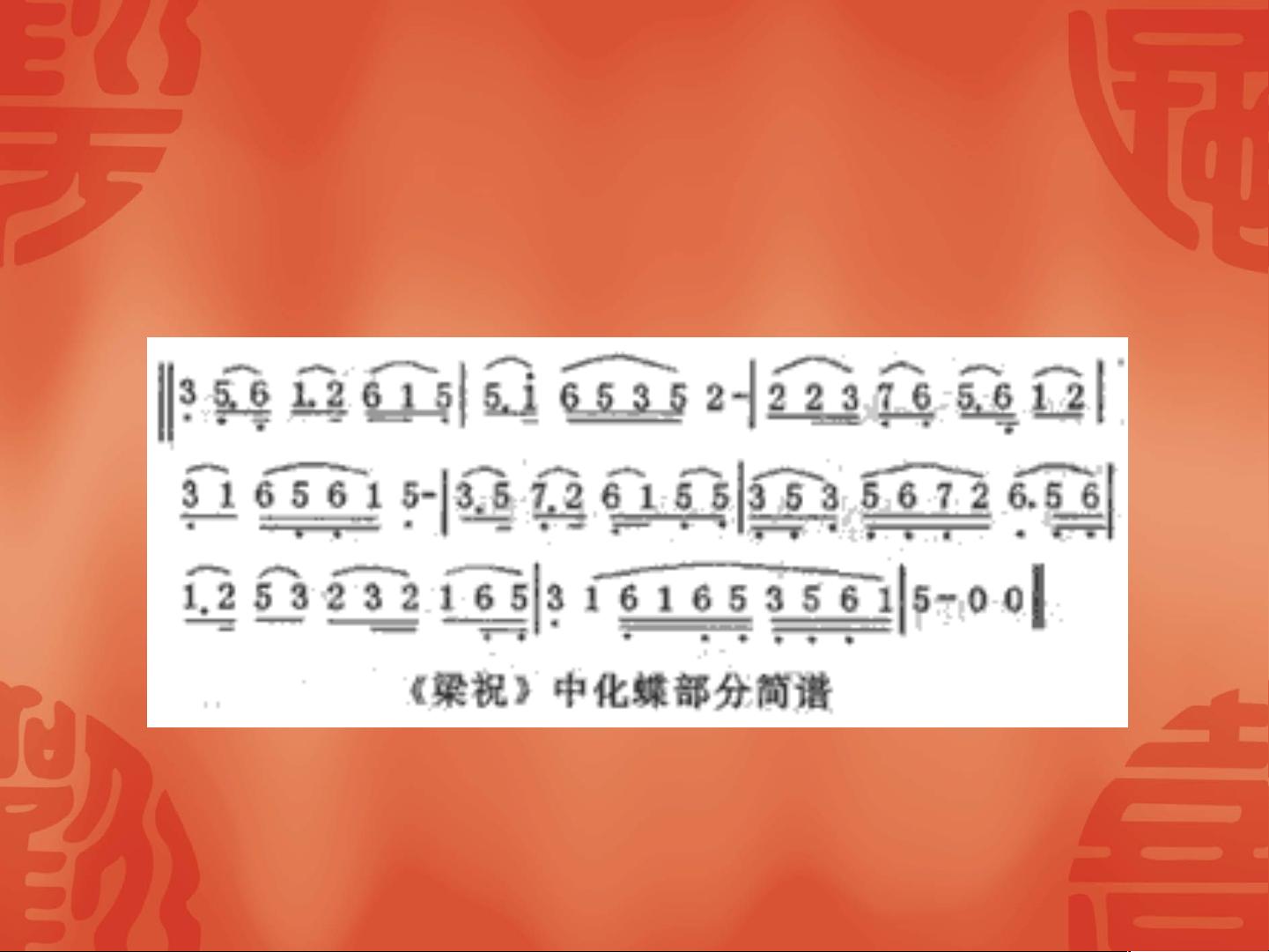

通过这个项目,设计者不仅学习了如何使用Verilog HDL编写代码,还掌握了音乐信号处理和FPGA设计的基础知识。这包括理解乐谱、计算音符频率、实现分频器以及进行时序分析等关键技能。最终,设计出的系统能够在给定的参考频率下,准确地播放出如《梁祝》化蝶部分的简谱,展示出音乐与数字逻辑的完美结合。

2015-06-14 上传

2013-03-05 上传

2024-10-14 上传

2024-10-14 上传

kagami__

- 粉丝: 1

- 资源: 4

最新资源

- 前端面试必问:真实项目经验大揭秘

- 永磁同步电机二阶自抗扰神经网络控制技术与实践

- 基于HAL库的LoRa通讯与SHT30温湿度测量项目

- avaWeb-mast推荐系统开发实战指南

- 慧鱼SolidWorks零件模型库:设计与创新的强大工具

- MATLAB实现稀疏傅里叶变换(SFFT)代码及测试

- ChatGPT联网模式亮相,体验智能压缩技术.zip

- 掌握进程保护的HOOK API技术

- 基于.Net的日用品网站开发:设计、实现与分析

- MyBatis-Spring 1.3.2版本下载指南

- 开源全能媒体播放器:小戴媒体播放器2 5.1-3

- 华为eNSP参考文档:DHCP与VRP操作指南

- SpringMyBatis实现疫苗接种预约系统

- VHDL实现倒车雷达系统源码免费提供

- 掌握软件测评师考试要点:历年真题解析

- 轻松下载微信视频号内容的新工具介绍