CUDA架构下的矩阵乘法优化与加速研究

29 浏览量

更新于2024-08-31

2

收藏 194KB PDF 举报

"本文主要研究了基于CUDA架构的矩阵乘法实现及其优化,通过在GPU上运用CUDA技术,实现矩阵乘法的高效计算。实验结果显示,CUDA矩阵乘法相较于CPU有显著的加速效果,最高加速比达1079.64,峰值比最高为30.85%,充分展示了GPU的浮点运算能力。CUDA编程模型允许CPU和GPU协同工作,CPU处理逻辑控制,GPU专注大规模并行计算,提高了整体计算效率。"

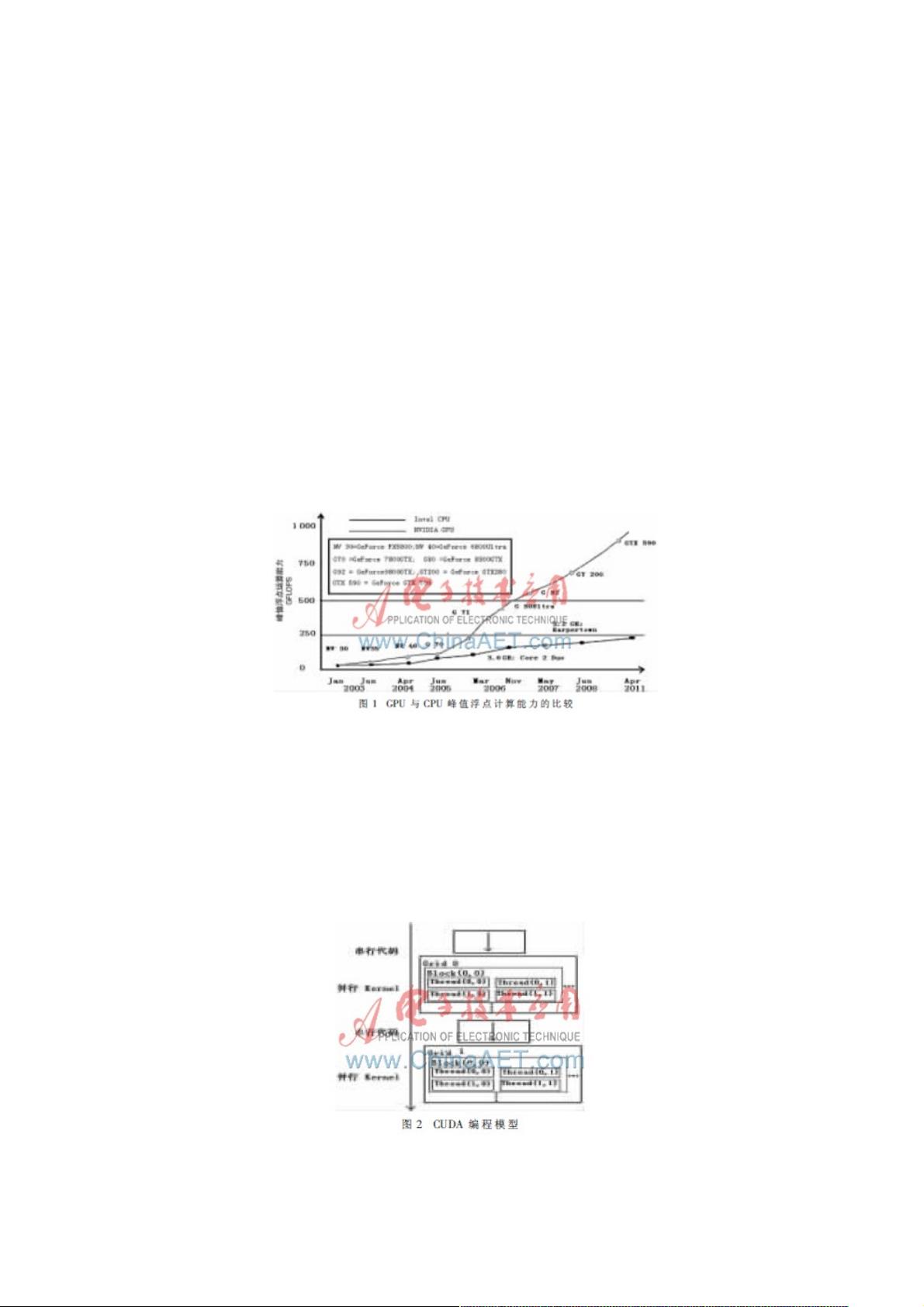

在当前计算领域,随着多核CPU和GPU的发展,计算模式已经转向CPU与GPU协同处理。CUDA作为一种由NVIDIA推出的统一计算设备架构,极大地增强了GPU的可编程性,使得GPU不再局限于图形渲染,而是能够应用于各种通用计算任务,包括矩阵乘法等高计算量的运算。

矩阵乘法是计算科学中的基础操作,尤其在图像处理、机器学习和科学计算等领域中不可或缺。然而,传统CPU在处理大规模矩阵乘法时,由于其架构限制,效率较低。相比之下,GPU因其并行计算能力强、浮点运算单元众多,成为解决此类问题的理想选择。在CUDA架构下,GPU的每个流多处理器(SM)包含多个流处理器(SP),可以同时处理大量数据,从而实现高效并行计算。

CUDA编程模型将CPU定义为主机,负责管理和调度任务,而GPU作为设备,执行计算密集型任务。这种分离使得CPU可以专注于串行逻辑控制,GPU则专注于执行并行计算,两者互补,实现了计算性能的大幅提升。在矩阵乘法的实现中,作者可能采用了两种不同的CUDA实现策略,并对其进行优化,以充分利用GPU的硬件资源。

实验结果显示,基于CUDA的矩阵乘法相比CPU矩阵乘法,不仅速度提升明显,而且在GPU的浮点运算能力利用率上也表现出色。加速比高达1079.64意味着GPU执行相同任务的速度比CPU快了近1080倍,而30.85%的峰值比表示GPU在计算过程中接近了其理论最大计算能力的三分之一,这在实际应用中是非常高的效率。

CUDA架构为解决大规模计算问题提供了新的途径,通过优化矩阵乘法等算法,可以在GPU上实现高效计算,显著提升了计算效率。这种技术的应用对于需要大量计算的领域具有重要意义,未来有望在更多领域得到推广和应用。

2010-02-21 上传

2018-05-04 上传

2011-07-07 上传

2021-10-10 上传

2012-12-01 上传

2012-11-23 上传

点击了解资源详情

weixin_38643307

- 粉丝: 8

- 资源: 925

最新资源

- EventBus:事件总线

- raspberry

- 提取均值信号特征的matlab代码-Challenge2021_firstunofficial:Challenge2021_firstunof

- Fire-Detection:该项目的重点是尽早尝试识别和检测火灾。 那是从烟雾开始的地方。

- 程序猿ProMonkey V2.03

- LeetCode:LeetCode刷题

- pics

- tongxunlu,条形码嵌入式c语言生成源码,c语言程序

- ud_handles:轴/图形孩子的管理。-matlab开发

- OkeTerraform

- UrduSearchingDictionory.java

- LevelClientEvIO:ev.io客户端

- 提取均值信号特征的matlab代码-second_unofficial_entry2021:second_unofficial_entry20

- MusicCD,c语言socks5源码分析,c语言程序

- sphinx-php:我的Sphinx扩展

- 基于Spring + Spring MVC + MyBatis的图书馆管理系统,使用Maven进行包管理 主要功能包括:图书查询