MAX+PLUS II PLD设计入门:四位二进制加法器实例

需积分: 9 13 浏览量

更新于2024-09-10

收藏 237KB DOC 举报

"MAX+PLUS II 使用指南 - EDA软件平台 - Altera公司 - PLD设计"

MAX+PLUS II 是美国Altera公司推出的一款计算机辅助工程(CAE)软件平台,专门用于可编程逻辑器件(PLD)的设计。这个系统以其易学易用的特点,广泛应用于电子设计自动化领域。它可以在运行Windows 95/98或Windows NT4.0的个人计算机上安装,最低硬件要求包括16MB内存和80MB硬盘空间。

在MAX+PLUS II 中,PLD设计通常分为三个主要步骤:设计项目的输入、设计项目的验证和设计项目的处理。设计输入阶段,用户可以选择多种方式,如文本输入、波形输入、图形输入和符号输入。本指南将以文本输入为例,通过构建一个四位二进制加法器的实例来详细讲解设计流程。

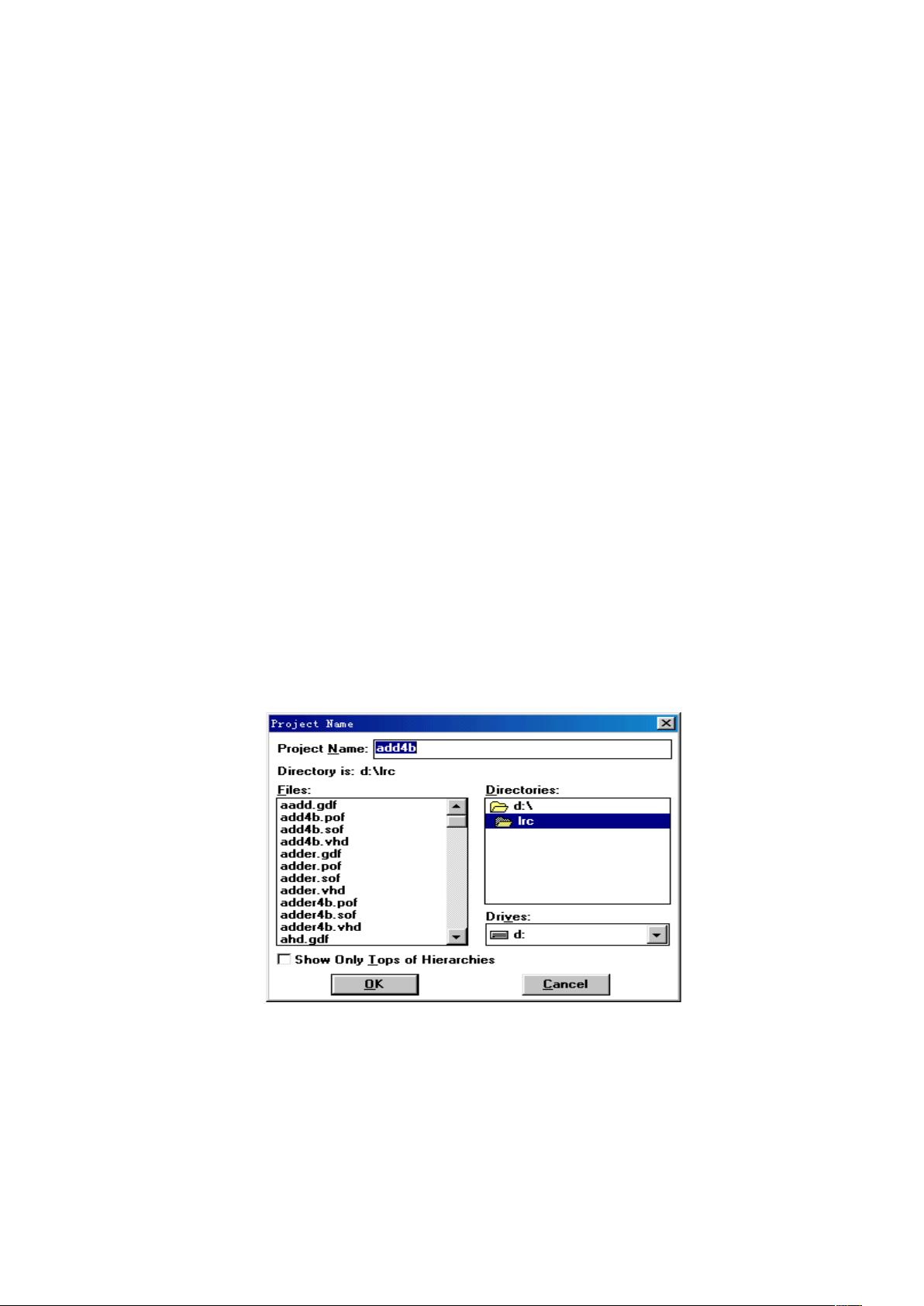

文本输入是其中最常用的一种方法,首先需要创建一个新的项目。这可以通过在启动MAX+PLUS II 后,选择“文件”-“项目”-“名称”,在弹出的对话框中输入项目名(例如“add4b”),并可选择保存的目录。完成这些设置后,MAX+PLUS II 的标题栏会显示新项目的名称。

接着,我们需要创建一个VHDL文本输入文件。在文件菜单中选择“新建”,然后在出现的对话框中选择“文本”选项。这样就可以开始编写VHDL代码,定义四位二进制加法器的逻辑功能。VHDL是一种硬件描述语言,允许设计师以结构化的方式描述数字系统的逻辑行为。

在设计项目的验证阶段,MAX+PLUS II 提供了仿真工具,可以让设计者检查逻辑电路的行为是否符合预期。这通常涉及到编写测试向量,运行仿真,观察输出结果是否符合预期的计算结果。

最后,在设计项目的处理阶段,MAX+PLUS II 可以将验证无误的VHDL设计转化为适配目标硬件的具体配置数据。这个过程可能包括综合、映射和布局布线等步骤,以优化逻辑实现并生成最终的编程文件。

在本实例中,选用的芯片是Altera公司的EPF10K10LC84-3,这是一种可编程逻辑器件,能够根据设计的VHDL代码配置成四位二进制加法器的电路。设计完成后,可以通过EDA实验开发系统对结果进行实物验证,确保设计的正确性和实际工作性能。

MAX+PLUS II 是一个强大的工具,对于理解和实践PLD设计流程至关重要。通过学习和掌握MAX+PLUS II 的使用,工程师能够快速有效地实现复杂的数字逻辑系统,提高设计效率,并为各种嵌入式和数字系统应用提供灵活的解决方案。

2024-10-28 上传

2024-11-12 上传

2024-11-12 上传

2024-11-12 上传

2024-10-26 上传

2024-10-27 上传

baidu_16053631

- 粉丝: 0

- 资源: 1

最新资源

- AJAX开发简略.pdf

- PowerBuilder8.0中文参考手册.pdf

- struts2.0+hibernate3.1+spring2.0的使用.doc

- VB中与串口通讯需要用到的控件介绍

- cpu卡基础知识与入门方法

- c++ TR1 文档

- 虚拟键盘的驱动程序 制作虚拟键盘的过程和

- MRPII-最经典的教材

- GRAILS中文开发PDF文档

- c++ 小游戏 程序

- 深入浅出Struts2.pdf

- 网络工程师英词典 网工英语词汇表.pdf

- Ubuntu实用学习教程

- Linux.C++.Programming.HOWTO

- QTP初级使用手册QTP8_Tutorial_oldsidney_cn

- 注册表概述精华及普遍误区