基于数字频率合成和FPGA的扫频仪设计

108 浏览量

更新于2024-08-31

2

收藏 237KB PDF 举报

"采用数字频率合成技术、FPGA和单片机进行扫频仪的设计"

本文主要探讨了一种基于数字频率合成技术(DFS)、现场可编程门阵列(FPGA)和单片机的扫频仪设计方法。扫频仪在通信系统、电子设备测试以及电路设计领域具有广泛应用,其主要功能是测定网络的幅频特性和相频特性,这对于理解系统的稳定性和性能至关重要。

系统总体方案中,设计者提出采用输出频率可步进调节的正弦扫频信号源作为被测网络的输入。通过测量不同频率点的信号幅度,可以得到网络的幅频响应;同时,通过过零比较和相位检测,可以获取相频特性。扫频信号的生成依赖于DFS技术,这是一种利用数字技术合成各种频率信号的方法,具有高精度、快速切换和宽频率范围的优点。

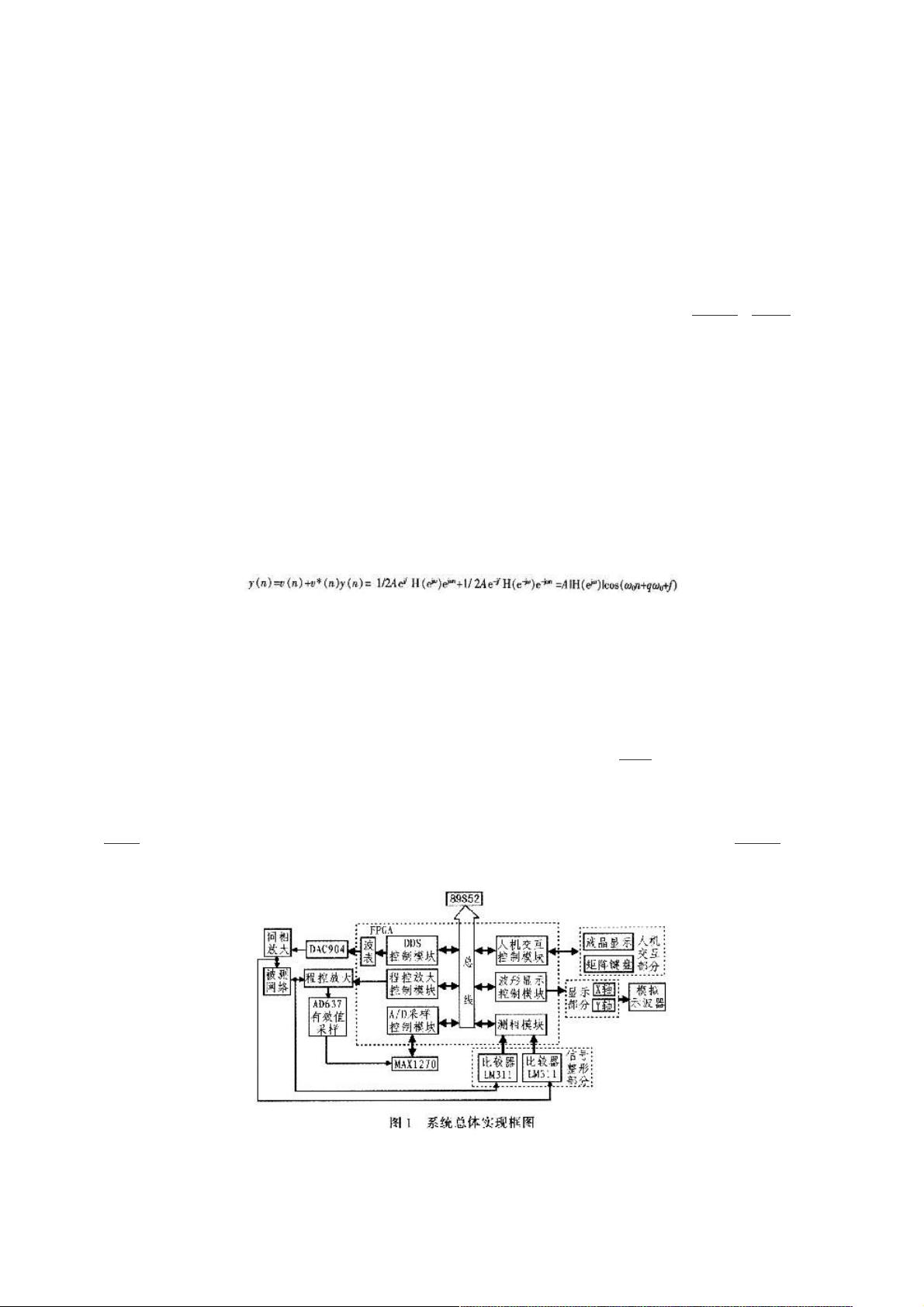

FPGA作为核心控制器,负责协调整个系统的运行,包括扫频信号的产生、频率步进调整、数据处理以及与外部设备的交互。单片机则辅助FPGA处理用户界面交互和系统设置,例如扫频范围和频率步进值的设定。A/D转换器用于将模拟信号转化为数字信号,D/A转换器则将数字信号转化为模拟扫频信号,二者在系统中起到关键的接口作用。

系统设计框图进一步揭示了系统的结构。键盘输入用于设定扫频参数,然后通过DDS(直接数字频率合成)控制模块调整D/A转换器,输出所需频率的扫频信号。扫频信号经过被测网络后,其幅度和相位会发生变化。为了补偿可能的信号衰减,设计中采用了程控放大器。接着,利用AD637进行有效值采样,以获取信号的幅度信息。LM311用于信号整形,便于后续的相位检测。最后,通过AD转换器MAXl270,将模拟信号转换为数字信号,以便进一步处理和分析。

通过这样的设计,扫频仪能快速、精确地测量出被测网络的幅频特性曲线和相频特性曲线,极大地提高了测量效率和准确性,适用于各种生产、科研和教学场景。同时,FPGA的灵活编程能力和单片机的用户友好性,使得该系统具有良好的可扩展性和适应性,可以根据不同的测试需求进行定制。

198 浏览量

222 浏览量

113 浏览量

387 浏览量

111 浏览量

2021-04-16 上传

153 浏览量

150 浏览量

2021-09-25 上传

weixin_38691194

- 粉丝: 5

最新资源

- Homebridge Xbox电视插件:实现微软游戏机的HomeKit控制

- Code.js:打造前端开发中的语法高亮显示

- Java实现GDP经济地图可视化分析

- 解决Office 2003无法打开Office 2007文件的问题

- 使用Python实现K-Means进行文本聚类分析

- CentOS虚拟机模板使用指南及开源项目介绍

- Java实现的飞行模拟游戏项目

- 深入探究Windows 32位API的查询与应用

- 全面破解:U盘PE系统维护与分区工具教程

- Firefox OS NFC应用开发与远程内容加载实践

- Dart软件包管理器Pub的贡献指南与组织架构

- Spy4win8在Windows 8上的完美兼容性验证

- MySQL 5.7.16解压版:一键启动,简化数据库部署流程

- AMScrollingNavbar:Objective-C实现可滚动的UINavigationBar

- MYSQL培训经典教程 - 易学好用的数据库教程

- 探索CityGen道路插件:增强草图大师的道路生成功能