Verilog HDL语言教程:深入解析模块与端口

需积分: 5 121 浏览量

更新于2025-01-03

1

收藏 771KB PPT 举报

“verilog HDL语言课件,清华大学课件,详细讲解Verilog语法,适合学习可编程逻辑语言。”

在Verilog HDL语言中,模块(module)是设计的核心元素,它代表了硬件设计的基本构建块,可以表示从简单的逻辑门到复杂的ASIC单元或整个系统。模块的定义以`module`关键字开始,接上模块名和端口列表,并在`endmodule`关键字处结束。模块内部主要包括五个部分:

1. 变量声明:这部分用来声明模块内部使用的变量,包括`wire`和`reg`类型的信号,以及其他数据类型。

2. 数据流语句:通常使用`assign`关键字,用于实现无时序的逻辑赋值,即静态连接。

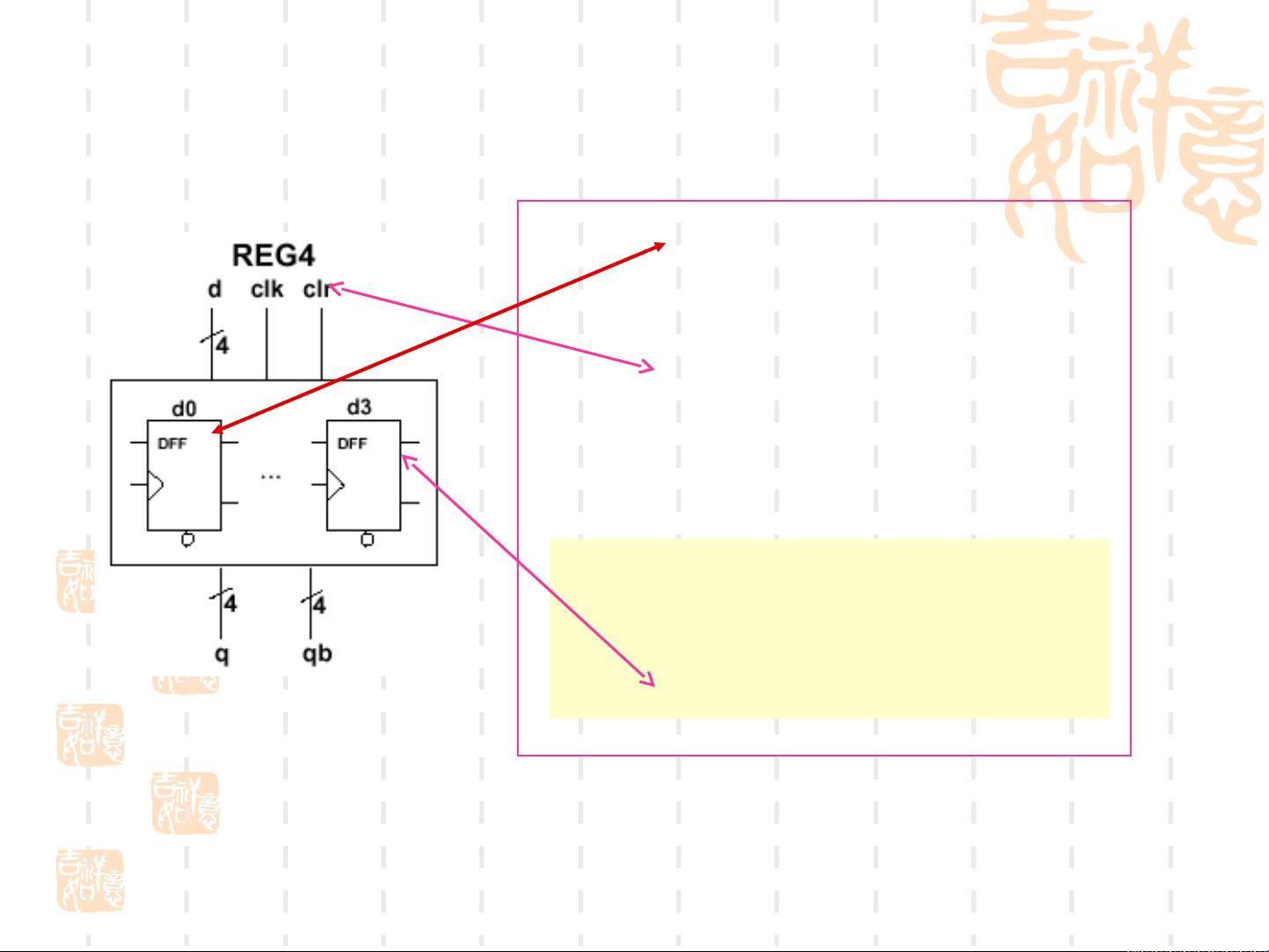

3. 低层模块实例:通过实例化其他模块,可以在当前模块中嵌套其他模块,实现模块化设计。

4. 行为描述块:`always`和`initial`块是行为描述的主要载体,其中`always`块用于描述时序逻辑,而`initial`块则用于初始化操作。

5. 任务(task)和函数(function):这两者提供了过程性语句,任务可以包含阻塞和非阻塞赋值,函数则只返回一个值,不允许有副作用。

端口(Terminal)是模块与其他模块或外部环境交互的接口,相当于硬件芯片的输入、输出引脚。它们分为三类:`input`输入端口,接收外部信号;`output`输出端口,提供对外部的信号;以及`inout`双向端口,可以同时进行读写操作。端口可以在模块声明时定义,可以指定为输入、输出或双向,并可以使用ANSI格式进行详细声明,如数据宽度等。

例如,下面的D触发器模块示例展示了如何声明端口:

```verilog

module D_FF(input d, clk, clr, output reg q, qb);

// ...

endmodule

```

在这个例子中,`d`是输入,`clk`和`clr`也是输入,而`q`和`qb`是输出。`reg`关键字表明`q`和`qb`是存储型变量,可以被驱动。

此外,模块之间的连接可以通过端口列表实现,例如在加法器模块`adder`中,输入`a`、`b`和`cin`,以及输出`cout`和`sum`都是通过端口进行通信的。这样的接口设计使得模块的内部实现可以独立于外部环境,增强了设计的可重用性和可维护性。

在学习Verilog HDL时,理解模块的概念、端口的使用以及它们如何构成硬件描述是至关重要的。这个清华大学的课件提供了一个很好的起点,通过深入学习,你可以掌握创建和实例化模块、定义和使用端口以及编写行为描述等核心技能,从而在FPGA或ASIC设计中运用自如。

114 浏览量

点击了解资源详情

点击了解资源详情

2012-07-08 上传

2022-09-24 上传

139 浏览量

116 浏览量

110 浏览量

2018-02-25 上传