FPGA开发入门:Quartus工程创建与编译步骤

需积分: 13 148 浏览量

更新于2024-07-15

收藏 3.81MB PDF 举报

"FPGA基本开发流程(quartus)"

在FPGA开发中,Quartus是Altera公司提供的一款强大的集成开发环境,用于设计、仿真、综合、编程和调试基于Altera FPGA的数字系统。以下是一个使用Quartus进行FPGA基本开发流程的详细步骤:

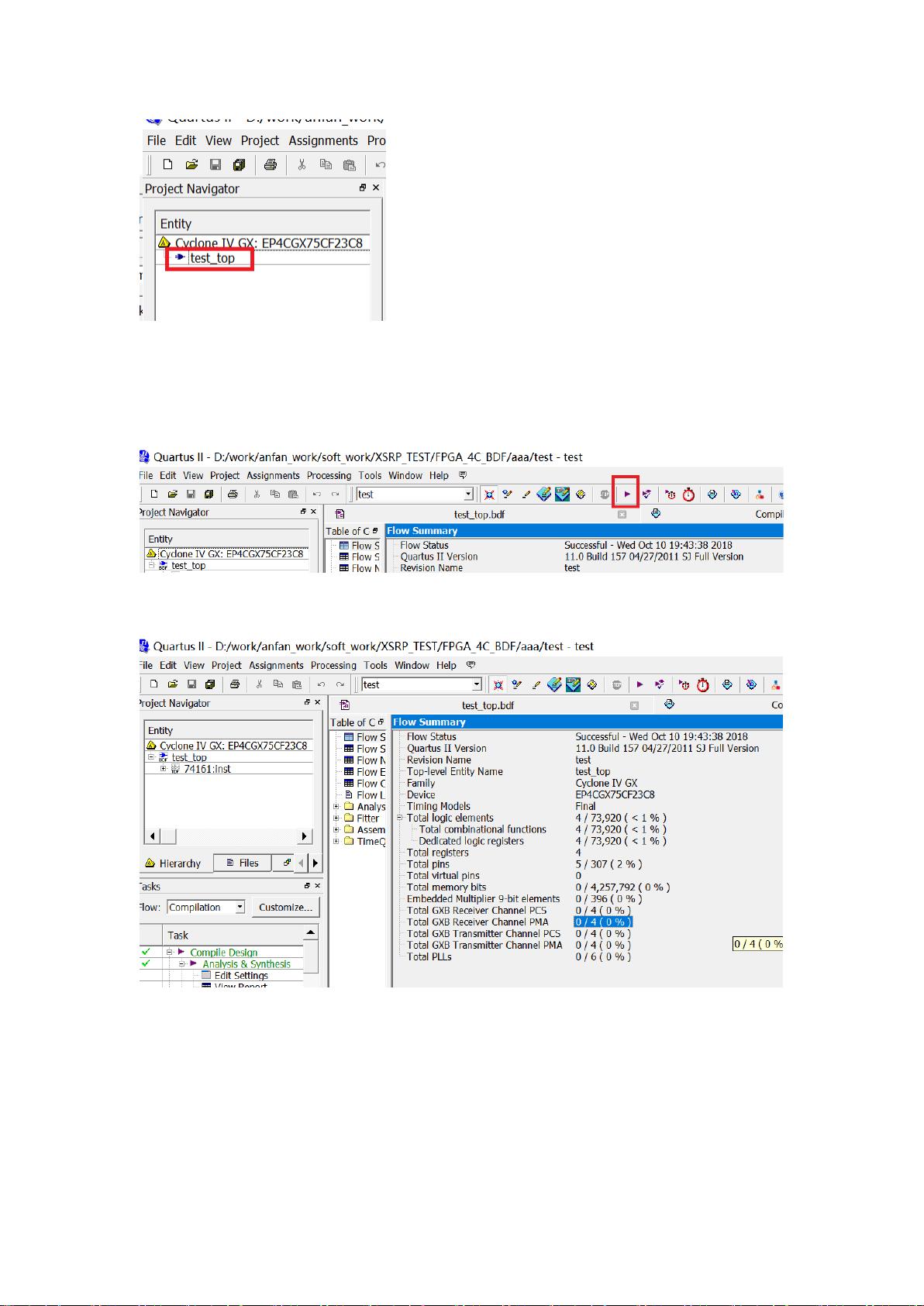

1. **工程建立过程**

- 首先,打开Quartus的工程建立向导,按照提示进行操作。

- 选择工程存放的文件夹,确保文件夹路径、工程名和文件名都是全英文字符,避免中文字符导致的问题。

- 在向导中不添加任何文件,直接选择下一步。

- 接下来,选择你要使用的FPGA器件型号,例如EP4CGX75CF23C8或EP3C25E144C8。

- 最后,确认设置并完成工程创建。

2. **建立顶层文件**

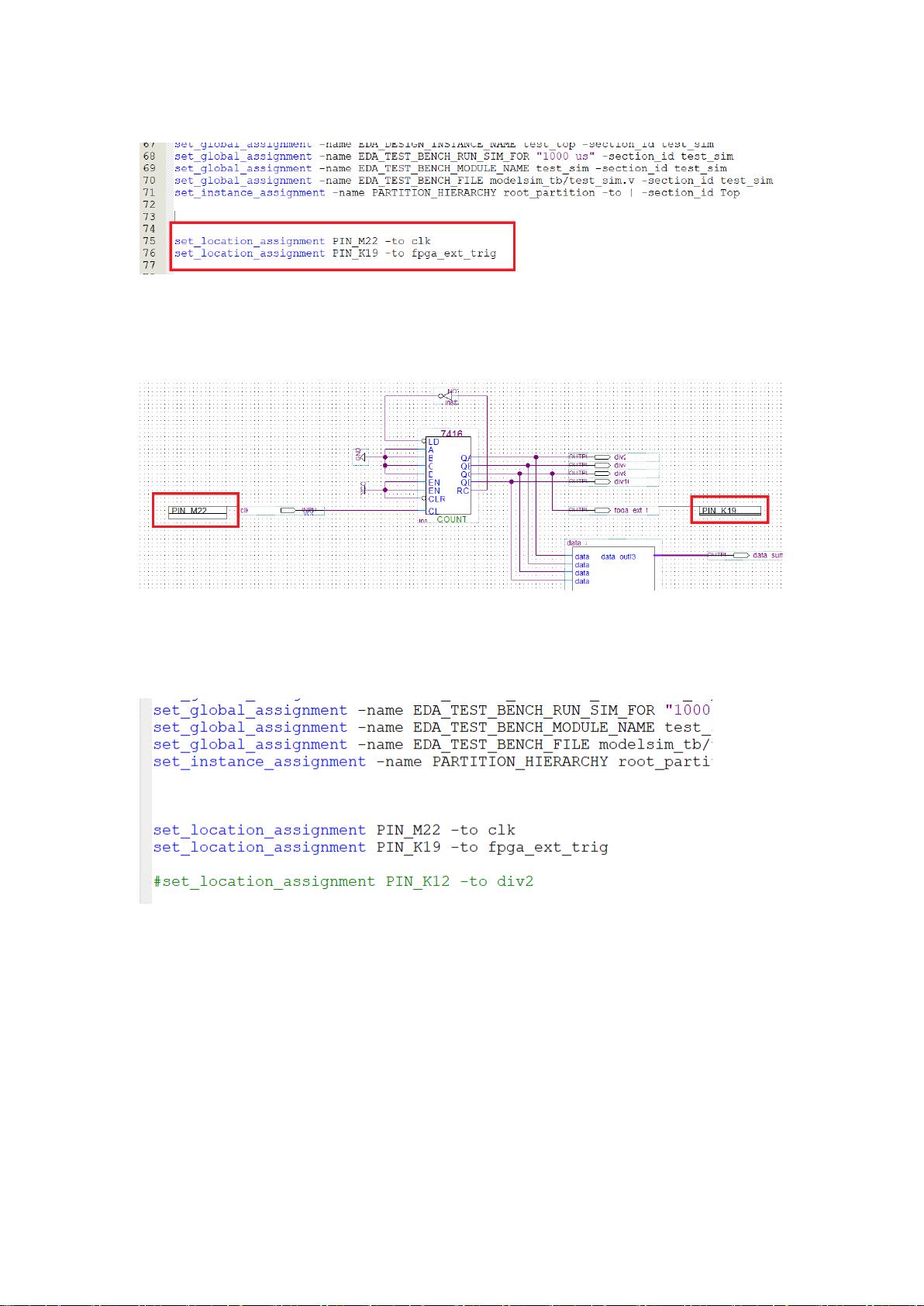

- 顶层文件是FPGA设计的核心,可以是电路原理图(Block Diagram/Schematic File)或者Verilog代码(Verilog HDL File)。

- **原理图设计**:

- 新建一个BDF文件,如`test_top.bdf`,保存在工程文件夹内。

- 在原理图中添加输入输出信号,如双击工作区放置。

- 定义输入信号、输出信号以及所需逻辑电路,如74161等。

- 使用"Properties"设置信号名称,如"div2"。

- 编辑完成后,保存文件,并将其设置为工程的顶层文件。

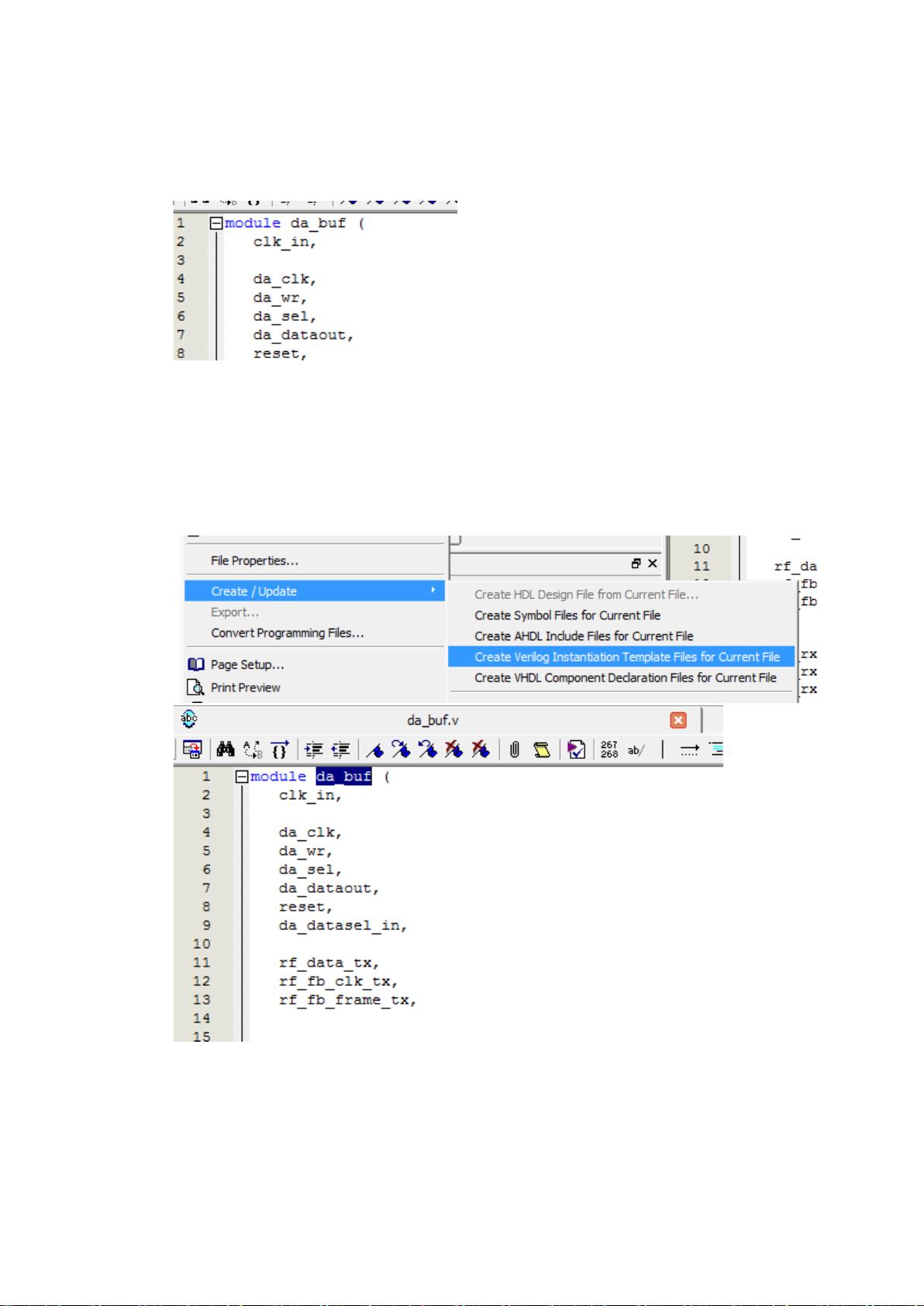

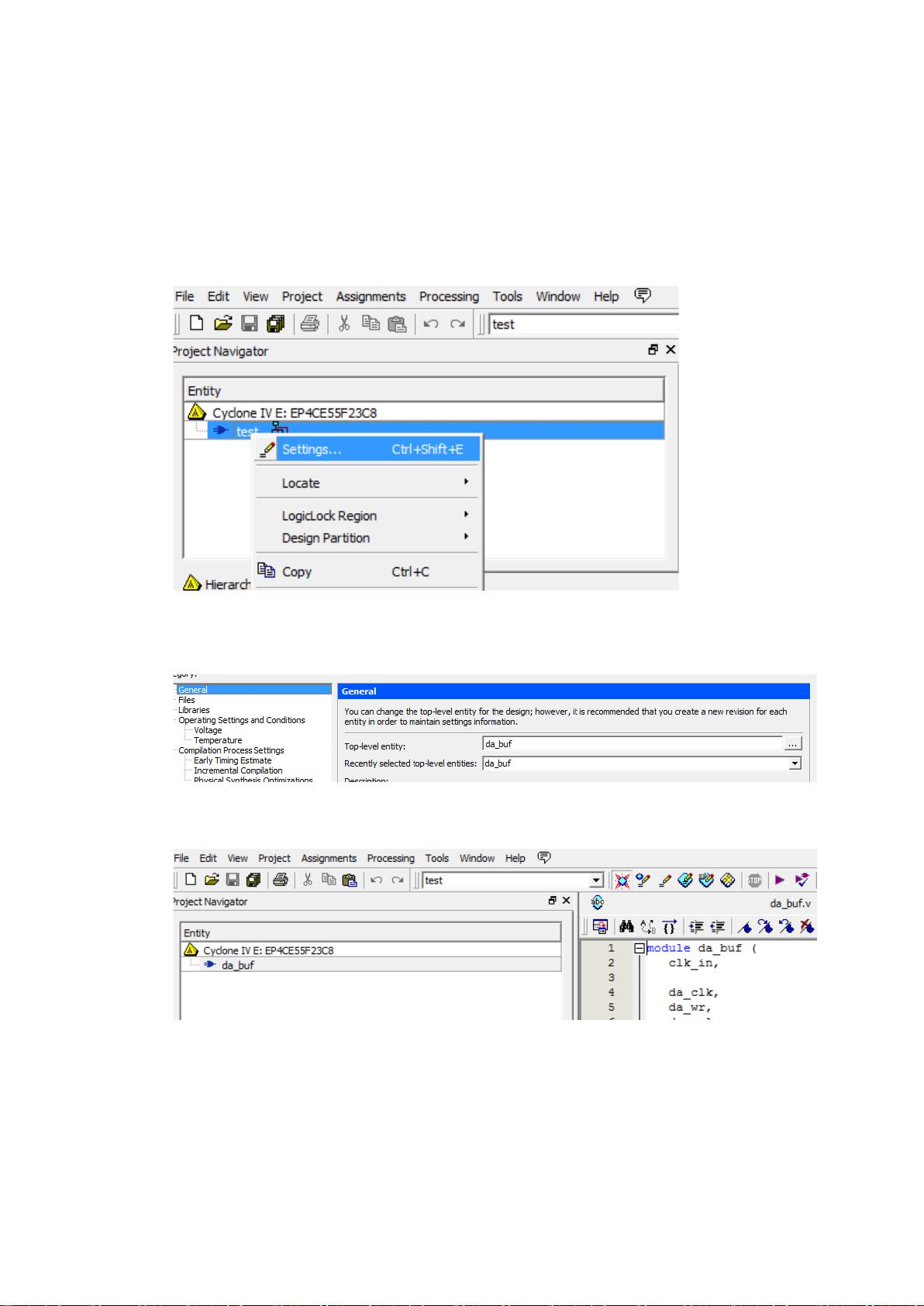

- **Verilog设计**:

- 创建一个新的Verilog文件,文件名与模块名相同,如`test.v`。

- 编写Verilog代码来描述电路逻辑,包括输入、输出及内部逻辑。

- 将此文件设置为顶层文件。

3. **编译工程**

- 在设置完顶层文件后,进行工程编译。点击编译按钮,Quartus将对设计进行逻辑综合、映射、布局布线等一系列处理。

- 编译完成后,会显示FPGA资源的使用情况,如逻辑单元、查找表、存储器等。

- 若编译过程中出现错误,需根据错误提示进行修正。

4. **错误检查与优化**

- 在编译过程中遇到的错误或警告,必须仔细分析并解决,以确保设计的正确性。

- 可通过调整代码结构、优化逻辑或更改器件资源分配等方式进行优化。

5. **下载与验证**

- 一旦设计编译无误,可以生成编程文件,使用JTAG或SPI等接口将设计烧录到FPGA芯片中。

- 使用硬件设备或仿真工具对设计进行功能验证,确保其符合预期行为。

6. **调试与测试**

- 对于复杂的设计,可能需要进行调试以找出潜在问题。Quartus提供了波形查看器、信号探针等工具帮助调试。

- 通过测试平台或自定义的测试激励对设计进行测试,确保所有功能都能正常工作。

FPGA开发涉及多个阶段,包括设计、综合、布局布线、编程和验证,每个步骤都至关重要,需要细心处理。在Quartus环境下,用户可以通过直观的图形界面和强大的工具集,高效地完成FPGA设计任务。

2021-01-21 上传

2023-02-20 上传

2022-06-14 上传

2022-04-22 上传

2022-11-02 上传

2023-04-04 上传

2019-07-09 上传

2023-03-01 上传

2021-05-14 上传

超威橘猫

- 粉丝: 126

- 资源: 35

最新资源

- 人工智能导论-拼音输入法.zip

- 协同测距matlab程序和数据.rar

- CPP.rar_人物传记/成功经验_Visual_C++_

- sslpod

- matlab拟合差值代码-PSCFit:Matlab代码,包括GUI,用于分析相和强直突触后电流(PSC)

- postman-twitter-ads-api:Twitter Ads API的Postman集合

- Cactu-Love_my-first-project

- 中英文手机网站源代码

- PscdPack:SEGA Genesis Classics ROM包装机

- 人工智能大作业-无人机图像目标检测.zip

- Advanced Image Upload and Manager Script-开源

- 00.rar_棋牌游戏_Visual_C++_

- INJECT digital creativity for journalists-crx插件

- bert_models

- HTP_SeleniumSmokeTest

- Remote Torrent Adder-crx插件