华为内部Verilog HDL入门教程详解

需积分: 44 66 浏览量

更新于2024-07-30

收藏 281KB PDF 举报

本篇Verilog HDL入门教程是华为内部资料,针对Verilog Hardware Description Language (HDL)进行深入讲解,共41页,主要涵盖了Verilog语言的基础知识和基本语法。教程内容分为以下几个部分:

1. **章节1 - 定义与概述**

- 开篇介绍了Verilog HDL的简介,包括其在硬件描述设计中的作用、历史以及设计方法学的基本概念。

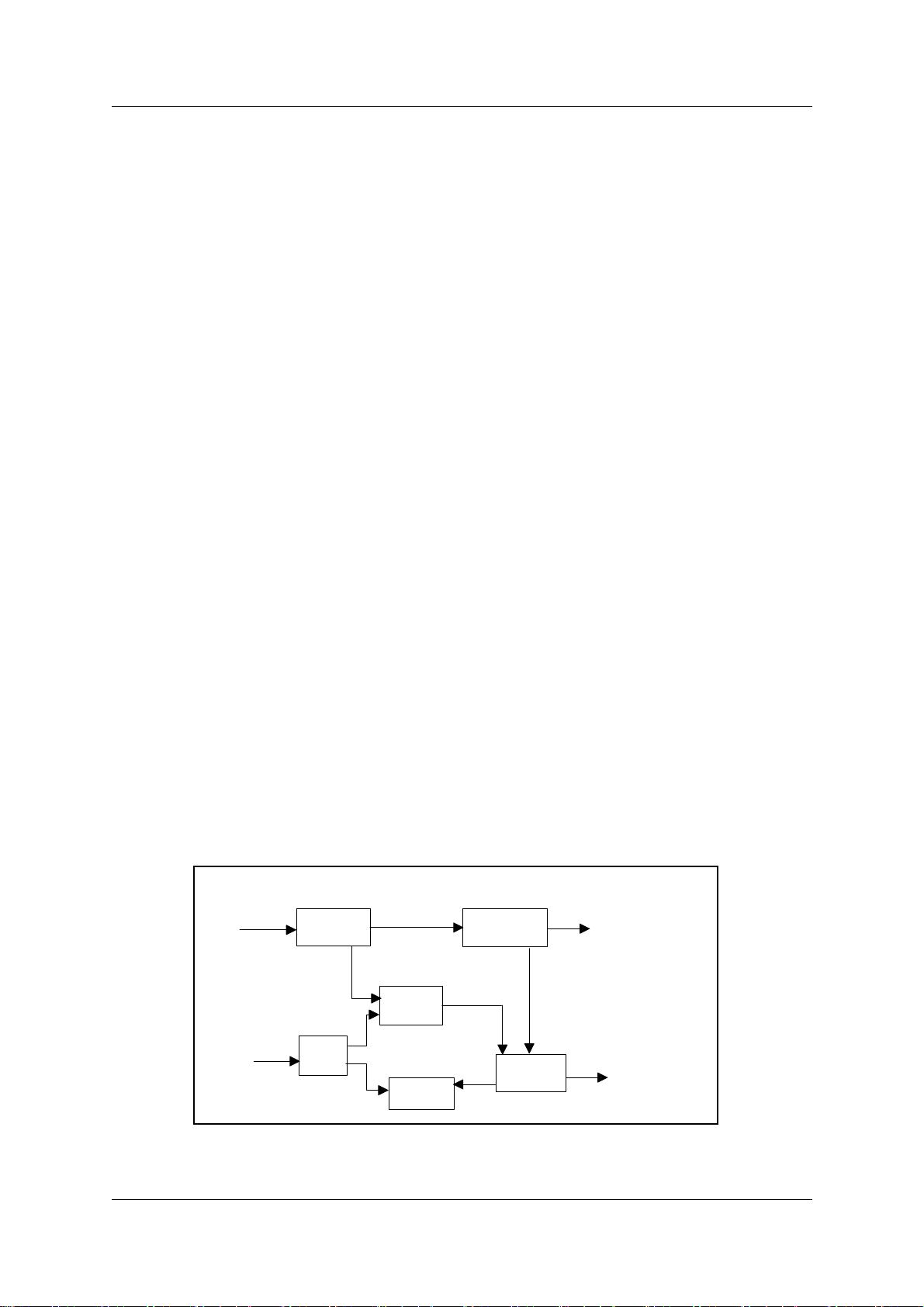

- 详细解释了Verilog的三种建模方式:结构化描述(模块)、数据流描述和行为描述。

2. **章节2 - Verilog基本语法**

- 介绍了模块语法,包括模块的结构和简单示例,以及如何定义标识符和使用关键字。

- 讲述了数值类型(如线网类型和寄存器类型)、数据类型(常量、值集合和数字值集合),以及运算符(算术运算符、关系运算符、逻辑运算符等)的使用。

3. **章节3 - 模块与时延**

- 着重于模块的创建和语法,强调了模块在系统中的功能划分和接口定义。

- 提到了时延的概念,这对于理解和设计同步电路非常重要。

4. **章节4 - 结构建模与条件语句**

- 详细解释了case语句和条件语句的使用,以及连接和条件运算符在构建复杂逻辑结构中的作用。

5. **章节5 - 行为建模**

- 包括过程赋值语句、顺序语句块和行为建模的具体实例,这些都是实现动态控制和数据处理的关键部分。

- 通过实例演示了如何利用这些语句来描述系统的状态变化和行为。

6. **附录A - 保留字**

- 提供了Verilog语言中的保留字列表,确保编程时避免与关键字冲突。

7. **习题与实践**

- 通过练习题的形式,帮助读者巩固所学知识,并提供了一个实际操作的平台。

8. **其他方面**

- 虽然这部分没有具体列出,但可能涉及高级主题,如混合设计描述或与其他HDL语言的比较等。

这是一份全面的Verilog HDL入门教程,适合初学者理解该语言的基本概念、语法和应用技巧,以及如何在实际项目中进行有效的硬件描述设计。

点击了解资源详情

点击了解资源详情

103 浏览量

103 浏览量

271 浏览量

178 浏览量

点击了解资源详情

260 浏览量

flcyl

- 粉丝: 0

最新资源

- iOS自定义TabBar中间按钮的设计与实现

- STM32 F103利用SPI接口读写RFID标签的方法示例

- 局域网简单配置教程:使用交换机与路由器

- Jstl在JavaWeb开发中提高效率的应用

- 使用Spring Boot和AngularJS开发简单地址簿Web应用

- Chrome扩展:快速搜索最新运动成绩

- 将电子书签转换为纸质书签的实用工具

- cte v1.4发布:新增电阻串联功能的源码

- iOS数据存储管理:NSCoding类的使用示例

- 掌握分销商管理系统DRP的实战应用

- 天津大学匿名课程评价系统实现与应用

- AliExpress图片搜索Chrome扩展:一键式产品定位

- Java实现的歌曲推荐系统:算法与文件处理

- 2020年韩国人工智能竞赛:A7问题解决方案分析

- 解决Vue.js调试问题:页签不显示的两大原因与解决方案

- iOS开发:CoreData封装实现数据管理