MC9S08QE128 MCU Series Reference Manual, Rev. 1.0 Draft D

16 NON-DISCLOSURE AGREEMENT REQUIRED Freescale Semiconductor

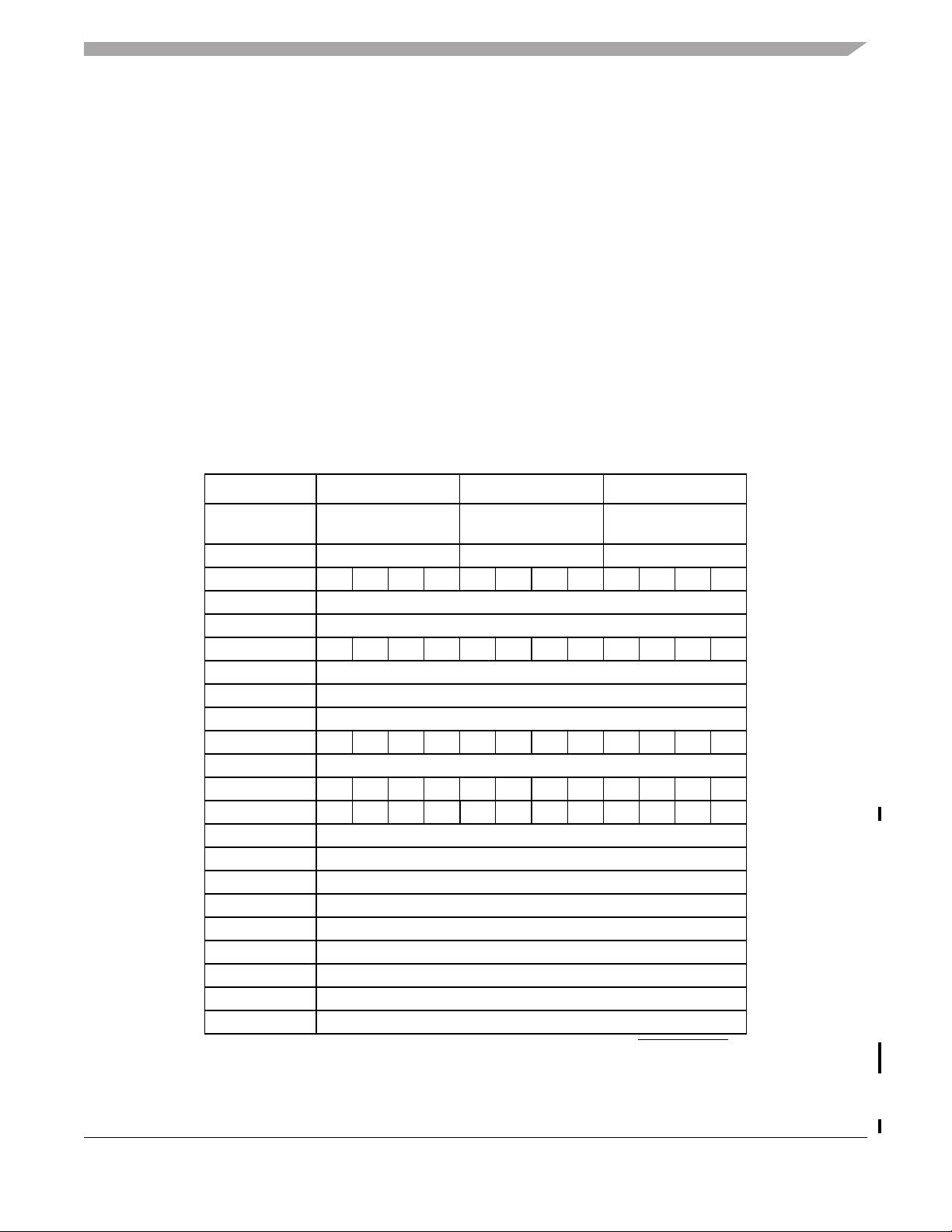

Section Number Title Page

15.1.1 SPI Clock Gating ............................................................................................................271

15.1.2 Features ...........................................................................................................................273

15.1.3 Block Diagrams ..............................................................................................................274

15.1.4 SPI Baud Rate Generation ..............................................................................................275

15.2 External Signal Description ..........................................................................................................276

15.2.1 SPSCK — SPI Serial Clock ............................................................................................276

15.2.2 MOSI — Master Data Out, Slave Data In ......................................................................276

15.2.3 MISO — Master Data In, Slave Data Out ......................................................................276

15.2.4

SS — Slave Select ...........................................................................................................276

15.3 Modes of Operation .......................................................................................................................277

15.3.1 SPI in Stop Modes ..........................................................................................................277

15.4 Register Definition ........................................................................................................................277

15.4.1 SPI Control Register 1 (SPIxC1) ....................................................................................277

15.4.2 SPI Control Register 2 (SPIxC2) ....................................................................................278

15.4.3 SPI Baud Rate Register (SPIxBR) ..................................................................................279

15.4.4 SPI Status Register (SPIxS) ............................................................................................280

15.4.5 SPI Data Register (SPIxD) ..............................................................................................281

15.5 Functional Description ..................................................................................................................282

15.5.1 SPI Clock Formats ..........................................................................................................282

15.5.2 SPI Interrupts ..................................................................................................................285

15.5.3 Mode Fault Detection .....................................................................................................285

15.6 Initialization/Application Information ..........................................................................................285

15.6.1 SPI Module Initialization Example .................................................................................285

Chapter 16

Timer/Pulse-Width Modulator (S08TPMV2)

16.1 Introduction ...................................................................................................................................289

16.1.1 ACMP/TPM Configuration Information .........................................................................289

16.1.2 TPM Clock Gating ..........................................................................................................289

16.1.3 Features ...........................................................................................................................291

16.1.4 Block Diagram ................................................................................................................291

16.2 External Signal Description ..........................................................................................................293

16.2.1 External TPM Clock Sources ..........................................................................................293

16.2.2 TPMxCHn — TPMx Channel n I/O Pins .......................................................................293

16.3 Register Definition ........................................................................................................................293

16.3.1 Timer Status and Control Register (TPMxSC) ...............................................................294

16.3.2 Timer Counter Registers (TPMxCNTH:TPMxCNTL) ...................................................295

16.3.3 Timer Counter Modulo Registers (TPMxMODH:TPMxMODL) ..................................296

16.3.4 Timer Channel n Status and Control Register (TPMxCnSC) .........................................297

16.3.5 Timer Channel Value Registers (TPMxCnVH:TPMxCnVL) .........................................298

16.4 Functional Description ..................................................................................................................299

16.4.1 Counter ............................................................................................................................299