5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

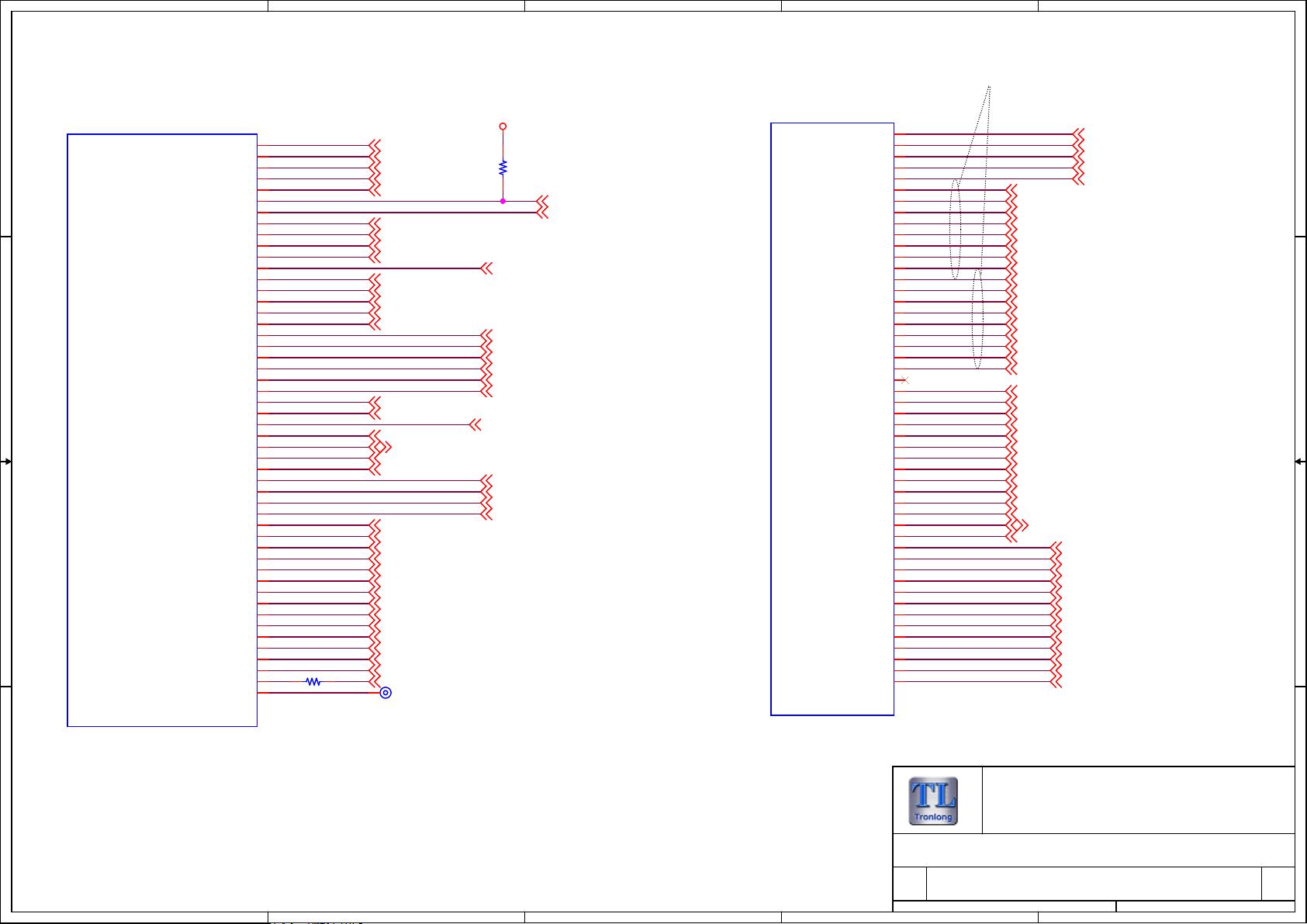

PHY_TXD[0:7] ; PHY_TXD[0:7] Routing by group.

3.3V IO LEVEL

2.5V IO LEVEL

BANK 14 & BANK 16

VDD_3V3_FPGA

FPGA_SPI_D3 3

FPGA_SPI_CS 3

FPGA_SPI_D1 3

FPGA_SPI_D0 3

FPGA_SPI_D2 3

FPGA_EMCCLK 16

PCIE_WAKEn_R 11

PCIE_RESET 11

FPGA_SCL 11,12,13

FPGA_SDA 11,12,13

PHY_TXD0 15

PHY_TXD7 15

PHY_TXD1 15

PHY_TXD2 15

PHY_TXD3 15

PHY_TXD4 15

PHY_TXD5 15

PHY_TXD6 15

PHY_RXD0 15

PHY_RXD1 15

PHY_RXD2 15

PHY_RXD3 15

PHY_RXD4 15

PHY_RXD5 15

PHY_RXD6 15

PHY_RXD7 15

PHY_GTXCLK 15

PHY_TXCLK 15

PHY_TXEN_TXCTL 15

PHY_TXER 15

PHY_RXCLK 15

PHY_RXDV_RXCTL 15

PHY_RXER 15

PHY_CRS 15

PHY_COL 15

PHY_MDIO 15

PHY_MDC 15

PHY_INTn 15

PHY_RESETn 15

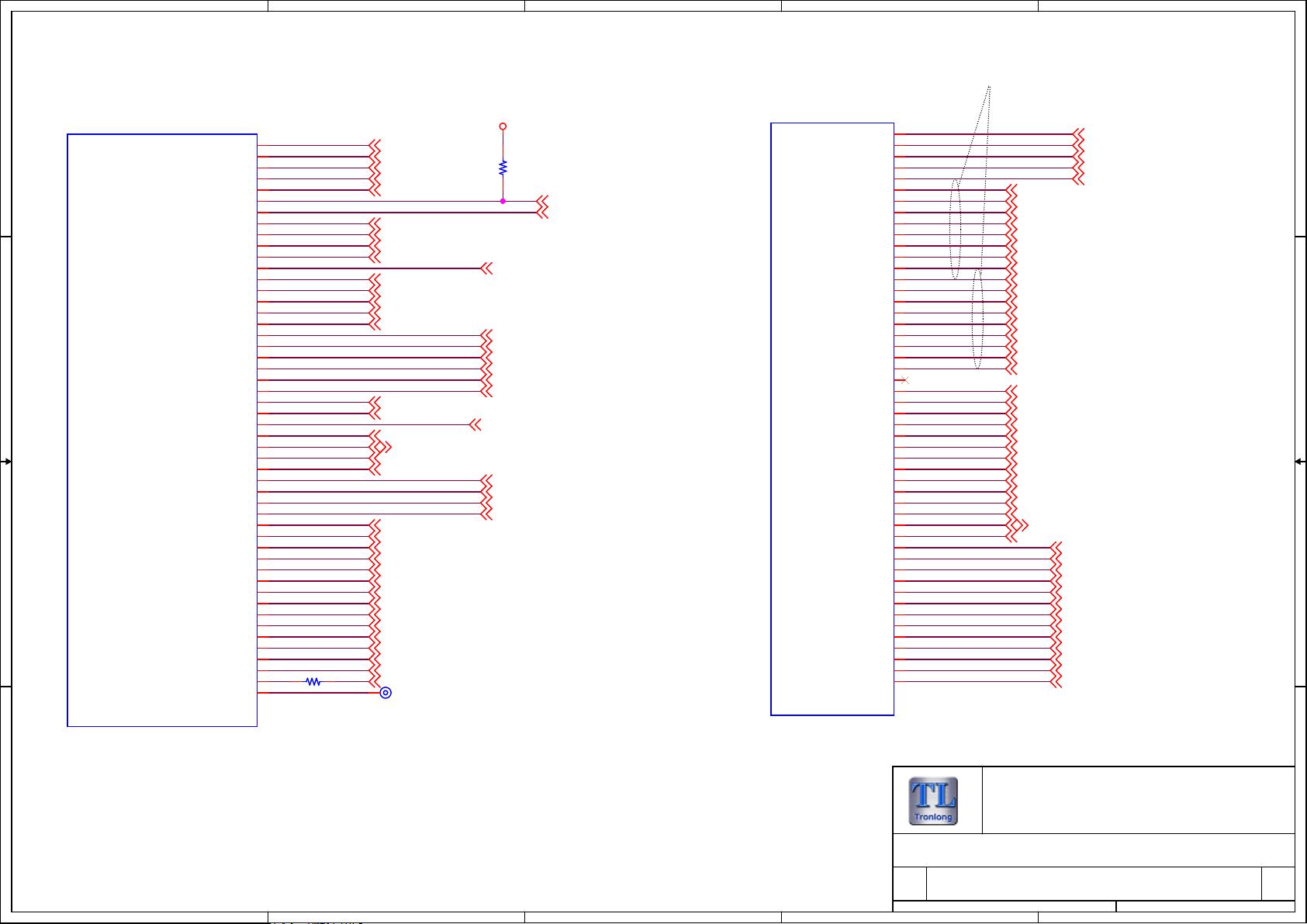

DAC_D0 18

DAC_D1 18

DAC_D2 18

DAC_D3 18

DAC_D4 18

DAC_D5 18

DAC_D6 18

DAC_D7 18

DAC_D8 18

DAC_D9 18

DAC_D10 18

DAC_D11 18

DAC_RSVD1 18

DAC_RSVD0 18

DAC_CLK- 18

DAC_CLK+ 18

DAC_MODE/SDIO 18

DAC_CMODE/SCLK 18

DAC_SPI/PIN 18

DAC_SLEEP/CSB 18

SYS_RESET 13,16

MAIN_CLK 21

PHY_CLK125 15

PHY_FREQ 15

CLK_GEN_nRSET 21

CLK_GEN_OD0 21

CLK_GEN_OD1 21

CLK_GEN_OD2 21

CLK_GEN_PR0 21

CLK_GEN_PR1 21

IO_0_14 16

IO_L9N_T1_DQS_D13_14 16

IO_L10P_T1_D14_14 16

IO_L10N_T1_D15_14 16

IO_L11P_T1_SRCC_14 16

IO_L11N_T1_SRCC_14 16

IO_L16P_T2_CSI_B_14 16

IO_L16N_T2_A15_D31_14 16

IO_L17P_T2_A14_D30_14 16

IO_0_16_2V5 16

IO_L2N_T0_16_2V5 16

IO_L2P_T0_16_2V5 16

IO_L19P_T3_16_2V5 16

IO_L19N_T3_VREF_16_2V5 16

IO_L20N_T3_16_2V5 16

IO_L20P_T3_16_2V5 16

IO_L21P_T3_DQS_16_2V5 16

IO_L21N_T3_DQS_16_2V5 16

IO_L22P_T3_16_2V5 16

IO_L22N_T3_16_2V5 16

IO_L23N_T3_16_2V5 16

IO_L23P_T3_16_2V5 16

IO_L24P_T3_16_2V5 16

IO_L24N_T3_16_2V5 16

IO_25_16_2V5 16

FPGA_UTX 14

FPGA_URX 14

IO_L9P_T1_DQS_14 16

IO_L15N_T2_DQS_DOUT_CSO_B_14 16

Title

Size

Document Number Re v

Date: Sheet o f

TL-A7HSAD A1

FPGA BANK14/15

Guangzhou Tronlong Technology Co., Ltd

A4

5 21Thursday, December 24, 2015

Title

Size

Document Number Re v

Date: Sheet o f

TL-A7HSAD A1

FPGA BANK14/15

Guangzhou Tronlong Technology Co., Ltd

A4

5 21Thursday, December 24, 2015

Title

Size

Document Number Re v

Date: Sheet o f

TL-A7HSAD A1

FPGA BANK14/15

Guangzhou Tronlong Technology Co., Ltd

A4

5 21Thursday, December 24, 2015

R14

0R

TP17

R224

1K_1%

XC7A50/75/100T-2FGG484I

U30-5

IO_0_16

F15

IO_L1P_T0_16

F13

IO_L1N_T0_16

F14

IO_L2P_T0_16

F16

IO_L2N_T0_16

E17

IO_L3P_T0_DQS_16

C14

IO_L3N_T0_DQS_16

C15

IO_L4P_T0_16

E13

IO_L4N_T0_16

E14

IO_L5P_T0_16

E16

IO_L5N_T0_16

D16

IO_L6P_T0_16

D14

IO_L6N_T0_VREF_16

D15

IO_L7P_T1_16

B15

IO_L7N_T1_16

B16

IO_L8P_T1_16

C13

IO_L8N_T1_16

B13

IO_L9P_T1_DQS_16

A15

IO_L9N_T1_DQS_16

A16

IO_L10P_T1_16

A13

IO_L10N_T1_16

A14

IO_L11P_T1_SRCC_16

B17

IO_L11N_T1_SRCC_16

B18

IO_L12P_T1_MRCC_16

D17

IO_L12N_T1_MRCC_16

C17

IO_L13P_T2_MRCC_16

C18

IO_L13N_T2_MRCC_16

C19

IO_L14P_T2_SRCC_16

E19

IO_L14N_T2_SRCC_16

D19

IO_L15P_T2_DQS_16

F18

IO_L15N_T2_DQS_16

E18

IO_L16P_T2_16

B20

IO_L16N_T2_16

A20

IO_L17P_T2_16

A18

IO_L17N_T2_16

A19

IO_L18P_T2_16

F19

IO_L18N_T2_16

F20

IO_L19P_T3_16

D20

IO_L19N_T3_VREF_16

C20

IO_L20P_T3_16

C22

IO_L20N_T3_16

B22

IO_L21P_T3_DQS_16

B21

IO_L21N_T3_DQS_16

A21

IO_L22P_T3_16

E22

IO_L22N_T3_16

D22

IO_L23P_T3_16

E21

IO_L23N_T3_16

D21

IO_L24P_T3_16

G21

IO_L24N_T3_16

G22

IO_25_16

F21

XC7A50/75/100T-2FGG484I

U30-3

IO_0_14

P20

IO_L1P_T0_D00_MOSI_14

P22

IO_L1N_T0_D01_DIN_14

R22

IO_L2P_T0_D02_14

P21

IO_L2N_T0_D03_14

R21

IO_L3P_T0_DQS_PUDC_B_14

U22

IO_L3N_T0_DQS_EMCCLK_14

V22

IO_L4P_T0_D04_14

T21

IO_L4N_T0_D05_14

U21

IO_L5P_T0_D06_14

P19

IO_L5N_T0_D07_14

R19

IO_L6P_T0_FCS_B_14

T19

IO_L6N_T0_D08_VREF_14

T20

IO_L7P_T1_D09_14

W21

IO_L7N_T1_D10_14

W22

IO_L8P_T1_D11_14

AA20

IO_L8N_T1_D12_14

AA21

IO_L9P_T1_DQS_14

Y21

IO_L9N_T1_DQS_D13_14

Y22

IO_L10P_T1_D14_14

AB21

IO_L10N_T1_D15_14

AB22

IO_L11P_T1_SRCC_14

U20

IO_L11N_T1_SRCC_14

V20

IO_L12P_T1_MRCC_14

W19

IO_L12N_T1_MRCC_14

W20

IO_L13P_T2_MRCC_14

Y18

IO_L13N_T2_MRCC_14

Y19

IO_L14P_T2_SRCC_14

V18

IO_L14N_T2_SRCC_14

V19

IO_L15P_T2_DQS_RDWR_B_14

AA19

IO_L15N_T2_DQS_DOUT_CSO_B_14

AB20

IO_L16P_T2_CSI_B_14

V17

IO_L16N_T2_A15_D31_14

W17

IO_L17P_T2_A14_D30_14

AA18

IO_L17N_T2_A13_D29_14

AB18

IO_L18P_T2_A12_D28_14

U17

IO_L18N_T2_A11_D27_14

U18

IO_L19P_T3_A10_D26_14

P14

IO_L19N_T3_A09_D25_VREF_14

R14

IO_L20P_T3_A08_D24_14

R18

IO_L20N_T3_A07_D23_14

T18

IO_L21P_T3_DQS_14

N17

IO_L21N_T3_DQS_A06_D22_14

P17

IO_L22P_T3_A05_D21_14

P15

IO_L22N_T3_A04_D20_14

R16

IO_L23P_T3_A03_D19_14

N13

IO_L23N_T3_A02_D18_14

N14

IO_L24P_T3_A01_D17_14

P16

IO_L24N_T3_A00_D16_14

R17

IO_25_14

N15