出租车计费系统VHDL实现详解与模块设计

在本篇VHDL代码中,我们将实现一个出租车收费系统的设计,它旨在模拟出租车的计费过程,包括起步价、行车里程计费和等待时间计费。这个项目的目标是通过三个主要模块:计程模块、计时模块和计费模块,配合分频模块和显示控制模块,来完成计费功能并显示结果。

首先,实验背景来自中科大的《复杂数字系统设计》课程,学生需完成出租车计费器的设计,以三位数码管显示总金额,最大值为99.9元,起步价5元,超出3km后每公里加收1元,等待时间以每分钟0.1元计费。在实际硬件环境中,考虑到实验板的限制,计费最大值和显示的最大里程数被调整为15.9元和15.9km,计程和计时的单位也相应调整。

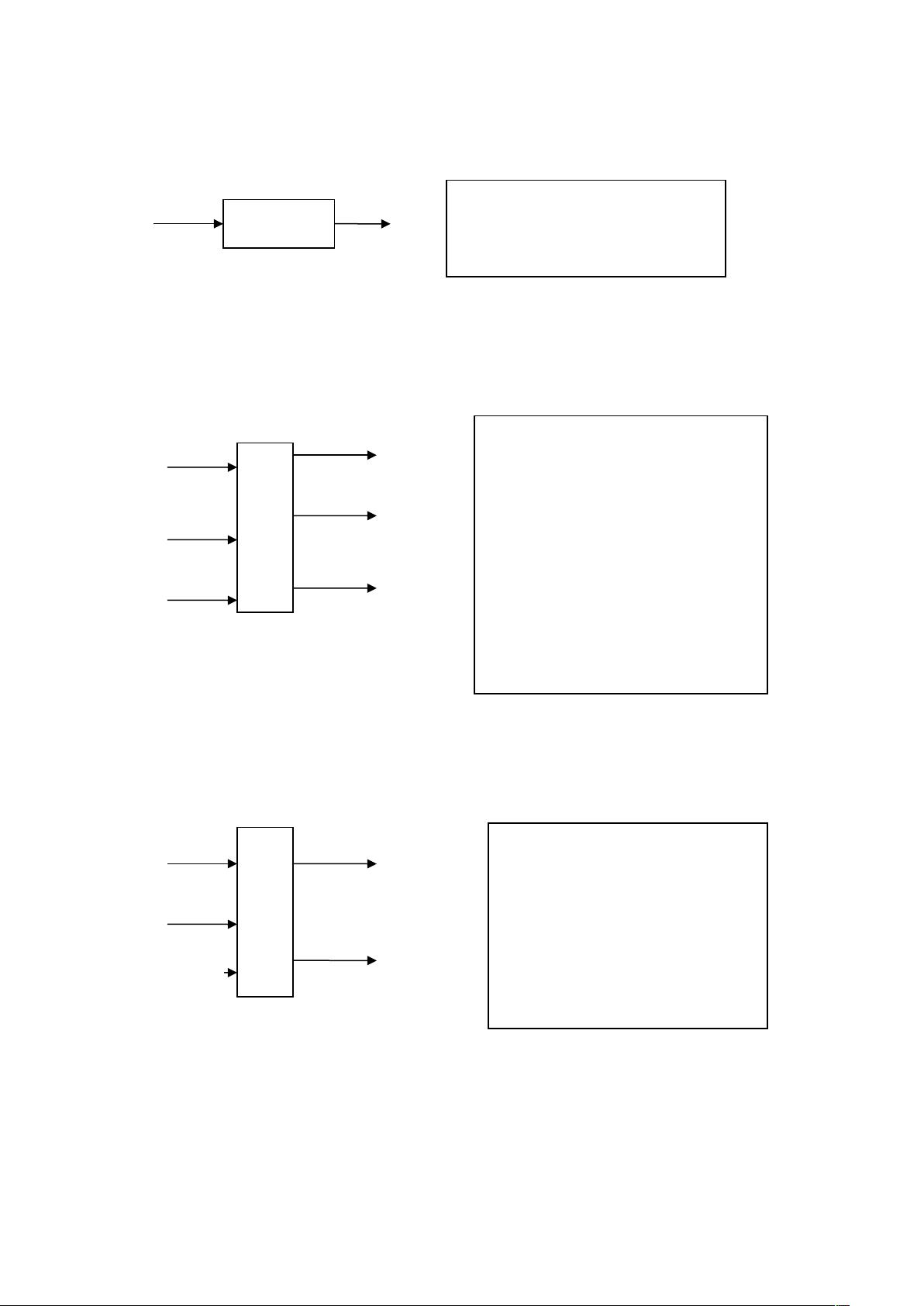

模块划分方面,整个系统分为六个模块:分频模块、计程模块、计时模块、计费脉冲生成模块、计费模块和显示控制模块。分频模块的作用是将实验板提供的50MHz脉冲降频到50Hz,以便于后续计程和计时的处理。计程模块接收分频后的脉冲,当接收到有效控制信号时,每50个脉冲累计0.1km的里程,并将里程数据传递给显示控制模块和计费脉冲生成模块。计时模块同样基于分频脉冲,每50个脉冲增加1分钟,输出等待时间。

计费脉冲生成模块根据行车里程和停车时间生成计费脉冲,确保计费的准确性。显示控制模块则负责根据显示控制开关的选择,将里程、时间和费用中的部分数据输出到八个LED灯上,以简化显示信息。

整个系统的实现不仅注重理论知识的应用,还强调了硬件与软件的结合,以及模块间的协同工作。对于新手学习VHDL编程或理解数字系统设计原理,这篇代码提供了很好的实战案例和实践经验。通过阅读和理解这份代码,用户可以深入掌握VHDL语言的运用,以及如何设计和实现一个实际应用中的计费系统。

2009-06-12 上传

2012-04-14 上传

2023-05-23 上传

2023-03-10 上传

2023-12-20 上传

2023-06-07 上传

2023-04-05 上传

2023-05-01 上传

tsrjtmx

- 粉丝: 0

- 资源: 4

最新资源

- Postman安装与功能详解:适用于API测试与HTTP请求

- Dart打造简易Web服务器教程:simple-server-dart

- FFmpeg 4.4 快速搭建与环境变量配置教程

- 牛顿井在围棋中的应用:利用牛顿多项式求根技术

- SpringBoot结合MySQL实现MQTT消息持久化教程

- C语言实现水仙花数输出方法详解

- Avatar_Utils库1.0.10版本发布,Python开发者必备工具

- Python爬虫实现漫画榜单数据处理与可视化分析

- 解压缩教材程序文件的正确方法

- 快速搭建Spring Boot Web项目实战指南

- Avatar Utils 1.8.1 工具包的安装与使用指南

- GatewayWorker扩展包压缩文件的下载与使用指南

- 实现饮食目标的开源Visual Basic编码程序

- 打造个性化O'RLY动物封面生成器

- Avatar_Utils库打包文件安装与使用指南

- Python端口扫描工具的设计与实现要点解析