掌握顺序脉冲发生器设计与Verilog实现

需积分: 49 190 浏览量

更新于2024-08-29

1

收藏 385KB DOCX 举报

实验3:顺序脉冲发生器实验是一个针对EDA(电子设计自动化)技术实践的重要环节,主要涉及Verilog HDL(Hardware Description Language,硬件描述语言)编程在实际应用中的教学。该实验旨在帮助学生深入理解并掌握顺序脉冲发生器的工作原理及其在数字系统中的作用。

首先,实验目标明确,学生将通过此实验学习和巩固以下关键知识点:

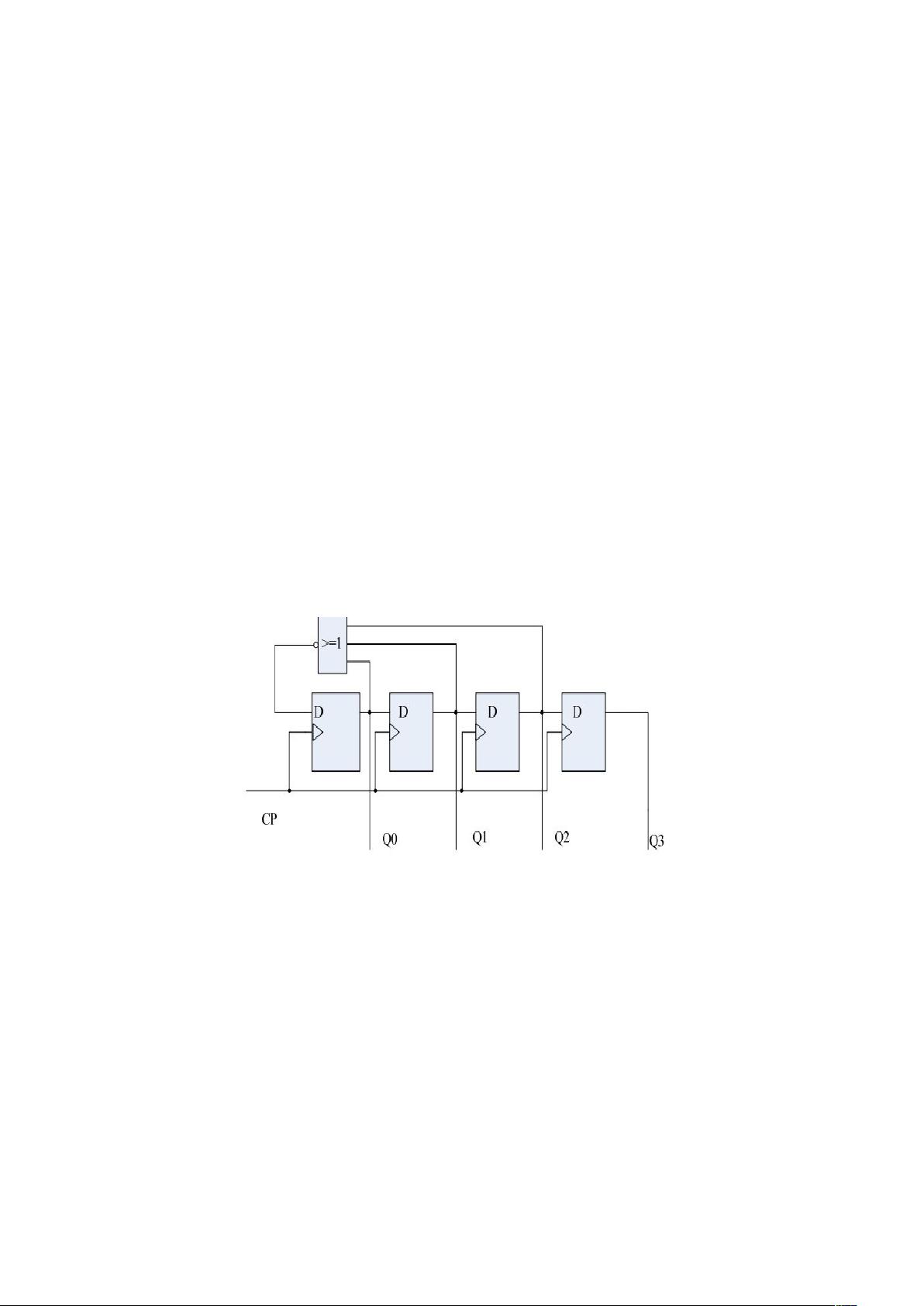

1. 顺序脉冲发生器原理:顺序脉冲发生器是数字系统中用于控制设备按照特定顺序执行操作的关键组件。它利用环形计数器,当输入连续脉冲时,产生一系列按特定序列输出的脉冲信号。当环形计数器处于每个状态仅有一个1的状态时,它就具备顺序脉冲发生器的功能。电路图示例显示了这一机制,包括Q0至Q3的输出信号和自启动的反馈逻辑电路。

2. Verilog语言编程:在实验中,学生会编写Verilog代码来实现顺序脉冲发生器。代码模块`pulgene`定义了输入时钟`clk`和复位信号`rst`,以及输出的4位波形信号`waveout`。使用`always @(posedge clk or posedge rst)`语句处理时钟上升沿和复位事件,实现了一个简单的移位寄存器结构,通过递归更新`waveout`变量生成顺序脉冲。

3. 电路设计与仿真:实验步骤包括创建新工程,编写并编译Verilog源代码,设置并配置矢量波形文件,然后编译整个工程。学生需手动或通过工具栏进行仿真,观察输出波形以验证设计的正确性。图2.1、图2.2和图2.3分别展示了这些步骤中的关键界面和仿真结果。

通过这个实验,学生不仅可以加深对顺序脉冲发生器的理解,还能提升他们的逻辑设计能力、Verilog编程技能以及使用Quartus II等EDA工具进行实际设计和模拟的能力。在后续的学习和工作中,这种基础的硬件描述和逻辑设计能力对于设计和优化复杂的数字系统至关重要。

2022-05-29 上传

2021-07-18 上传

2022-11-28 上传

2022-06-16 上传

2022-06-12 上传

2022-11-07 上传

2022-07-11 上传

2022-07-14 上传

2022-06-16 上传

barelank

- 粉丝: 14

- 资源: 11

最新资源

- Raspberry Pi OpenCL驱动程序安装与QEMU仿真指南

- Apache RocketMQ Go客户端:全面支持与消息处理功能

- WStage平台:无线传感器网络阶段数据交互技术

- 基于Java SpringBoot和微信小程序的ssm智能仓储系统开发

- CorrectMe项目:自动更正与建议API的开发与应用

- IdeaBiz请求处理程序JAVA:自动化API调用与令牌管理

- 墨西哥面包店研讨会:介绍关键业绩指标(KPI)与评估标准

- 2014年Android音乐播放器源码学习分享

- CleverRecyclerView扩展库:滑动效果与特性增强

- 利用Python和SURF特征识别斑点猫图像

- Wurpr开源PHP MySQL包装器:安全易用且高效

- Scratch少儿编程:Kanon妹系闹钟音效素材包

- 食品分享社交应用的开发教程与功能介绍

- Cookies by lfj.io: 浏览数据智能管理与同步工具

- 掌握SSH框架与SpringMVC Hibernate集成教程

- C语言实现FFT算法及互相关性能优化指南