Quartus II 软件使用:ChipPlanner深度教程

“Quartus II 使用教程,包括Chip Planner的详细使用方法以及Quartus II软件的介绍。”

在本文档中,我们将深入探讨Quartus II软件中的Chip Planner功能,这是一个强大的工具,用于实现FPGA(现场可编程门阵列)设计的可视化布局和资源分析。Chip Planner提供了设备资源的直观展示,帮助用户理解设备架构中资源原子的排列方式。通过这个集成平台,用户可以进行设计分析、工程变更订单(ECOs)等操作。

首先,Chip Planner的主要目标是让用户能够执行设计分析,了解设计在硬件上的实际占用情况。这包括对逻辑资源、I/O接口、时序和其他关键性能指标的评估。通过设计分析,用户可以优化设计以满足特定的性能需求。

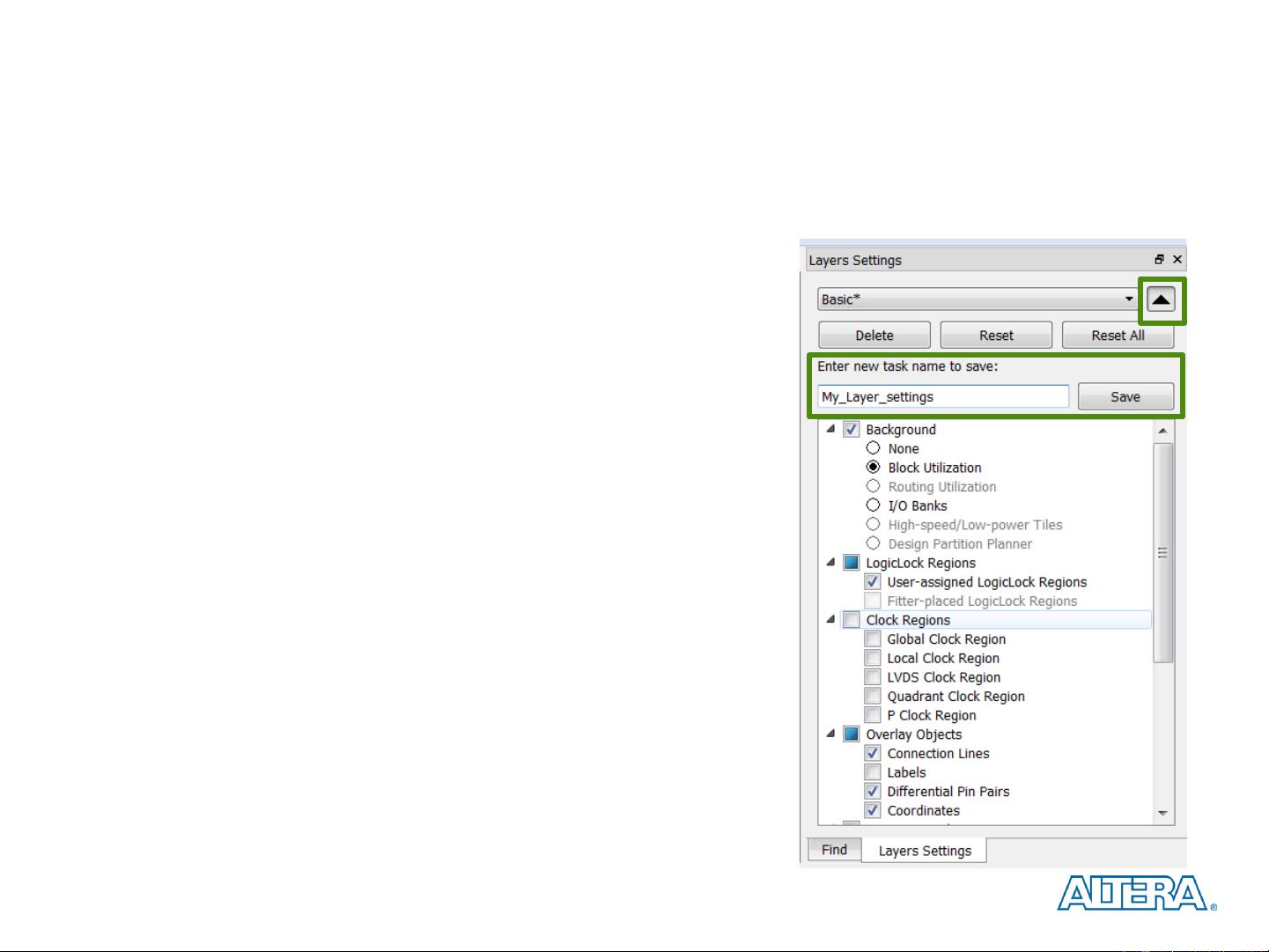

接下来,我们来看Chip Planner的使用。该工具可以通过Quartus II的工具菜单或工具栏轻松打开。一旦启动,它将显示当前设计在FPGA芯片上的布局,包括逻辑单元、存储器块、I/O端口等。

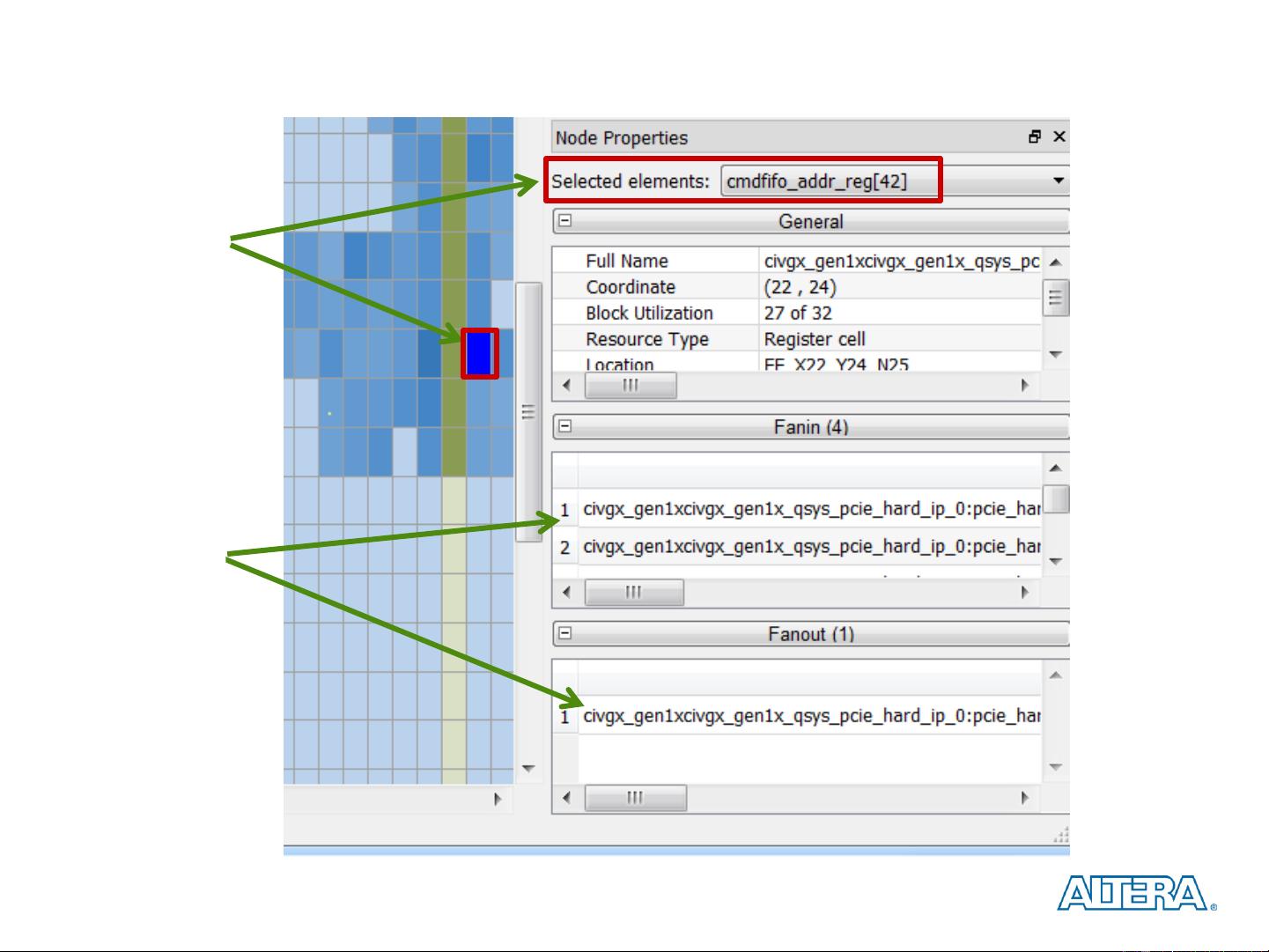

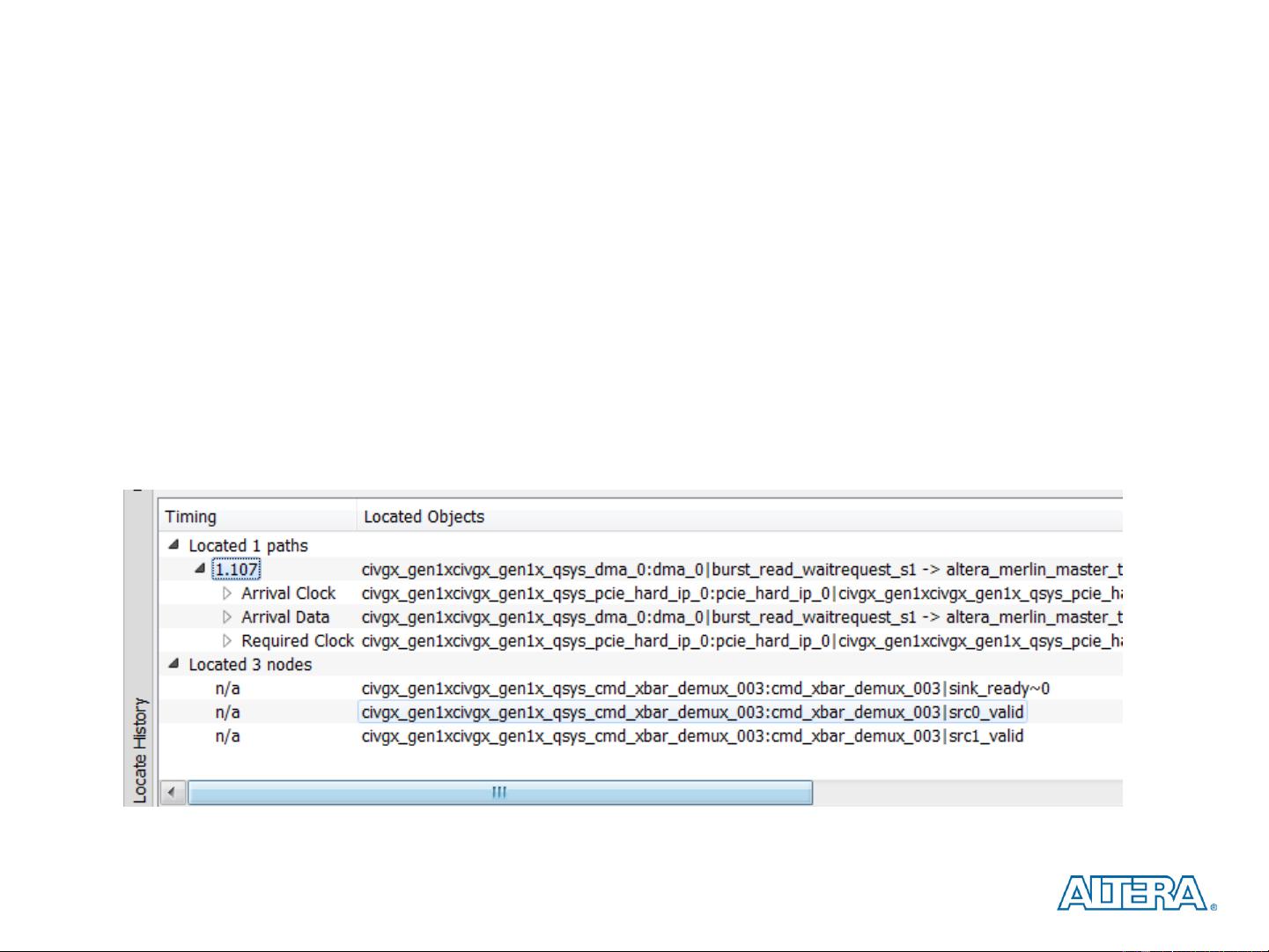

Chip Planner的一个重要特性是其交叉探针功能。这意味着用户可以从项目导航器、设计文件、设计分区规划器、编译报告、逻辑锁定区域、网表查看器、消息窗口甚至TimeQuest定时分析器右键点击,然后选择“在Chip Planner中定位”。这种功能极大地提高了设计调试和问题定位的效率。

在设计分析部分,用户可以查看设计占用的资源,例如查找未使用的逻辑资源,或者识别可能导致时序约束问题的区域。通过这种方式,设计师可以对设计进行微调,以达到最佳的性能和资源利用率。

对于工程变更订单(ECOs),Chip Planner提供了一种高效的方法来处理设计修改。ECOs允许用户在不重新进行完整设计流程的情况下,对已有的布局进行局部更改。这在设计迭代和后期设计优化中非常有用,因为它减少了整体的周转时间。

在处理逻辑锁定区域时,Chip Planner可以帮助用户确保某些特定逻辑在物理实现中保持固定位置。这对于需要保留某些功能不变或满足特定物理布局要求的设计至关重要。

Quartus II的Chip Planner是一个强大的工具,它结合了设计分析和工程变更管理,使得FPGA设计过程更加直观和高效。通过熟练掌握Chip Planner的使用,设计师可以更好地理解和优化他们的设计,从而提高FPGA设计的质量和性能。

相关推荐

qq_40762414

- 粉丝: 0

- 资源: 1

最新资源

- 小波功率谱用于降水、气温等的周期分析

- MPC模型预测控制-欠驱动船舶.zip

- torch_sparse-0.6.4-cp36-cp36m-linux_x86_64whl.zip

- vitamincalculator:给出不同维生素的计算器限制并计算您的每日剂量

- SteamAuth:NodeJS Steam身份验证器,登录和交易确认

- dkreutter.github.io

- Implementation-of-Graph-kernels:阅读有关图核的调查而编写的代码

- labelImgPackage.rar

- 公司营业室主任行为规范考评表

- torch_cluster-1.5.5-cp38-cp38-linux_x86_64whl.zip

- postnet-version-1.1B

- beavisbot:适用于plug.dj和dubtrack.fm的由node.js驱动的机器人

- FSDI103PROJECT2

- 导航菜单可拖动

- 编译so文件 Unity调用so文件样例

- 行政支援课课长