Cadence Virtuoso 使用指南:版图设计与验证

"Cadence Virtuoso 讲义涵盖了在Cadence环境中使用Virtuoso进行集成电路(IC)设计的方法,包括版图设计、验证工具的使用等。"

在IC设计领域,Cadence Virtuoso是一款广泛使用的高级混合信号设计平台,特别适合复杂的半导体器件设计。本讲义详细讲解了如何启动和配置Cadence设计系统,以及如何利用Virtuoso进行版图设计。

首先,系统启动涉及到多个配置文件的设置。`.cshrc`文件用于指定Cadence软件和许可证文件的位置,确保软件能够正确运行。`.cdsenv`文件使用SKILL语言编写,包含了Cadence软件的初始化设置,`.cdsinit`文件进一步定制工作环境。此外,`cds.lib`文件是至关重要的,它定义了设计所需的工艺参数,包括层的定义、器件符号、设计规则等。工艺文件(technology file)是设计的基础,它提供电气和物理规则,支持自动布局布线以及GDSII输出的规则定义。

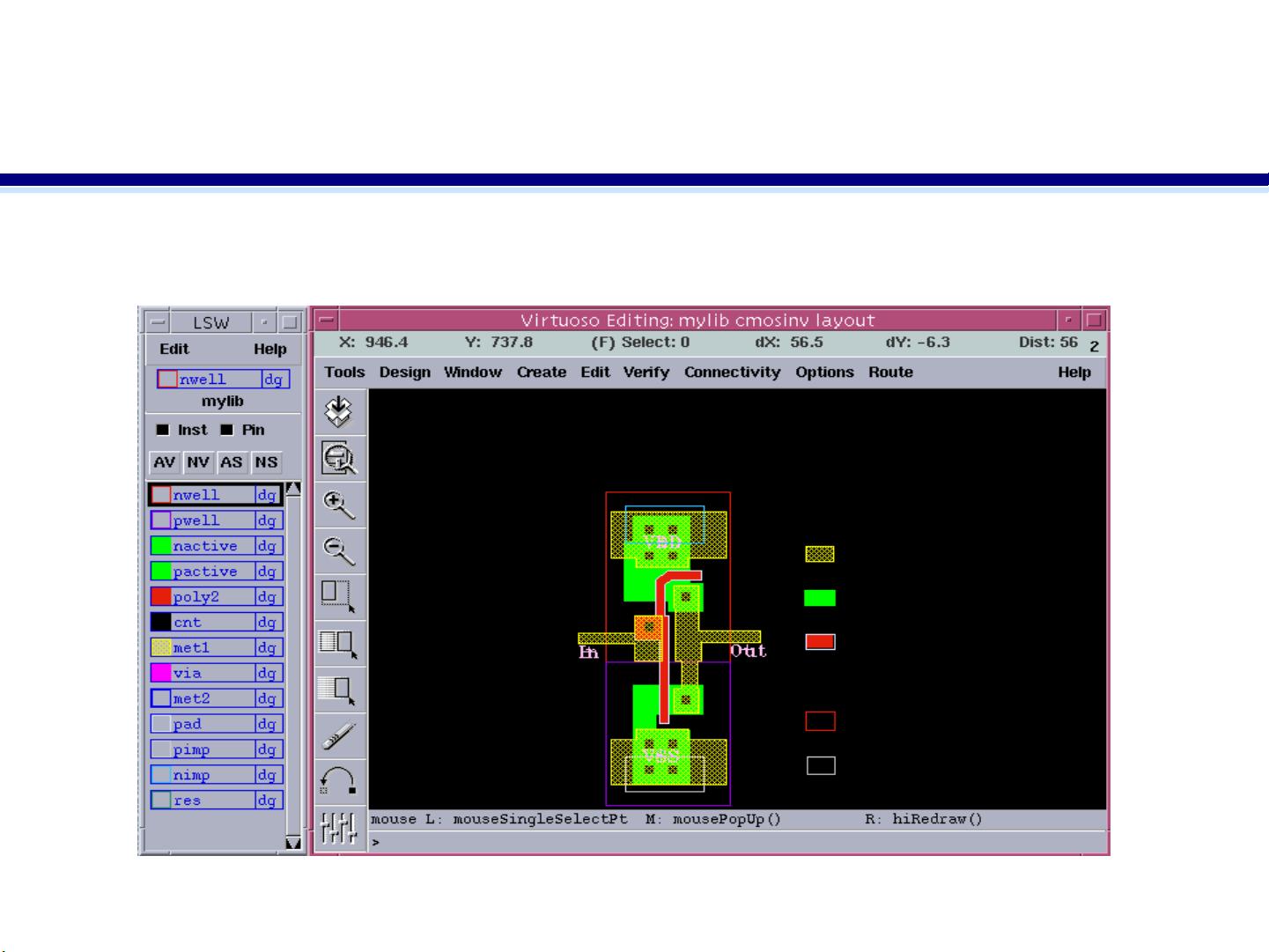

显示文件(display.drf)则用于设定图形界面的显示参数,使得设计师在进行版图设计时能有良好的视觉体验。启动版图工具时,可以根据需求选择不同的命令,如`layout s`用于基础版图设计,`layoutPlus m`提供了自动化设计和交互验证功能,而`icfb xl`则支持从前端到后端的大部分设计工具。

系统启动还涉及`Command Interpreter Window (CIW)`,这是用户与Cadence环境交互的主要界面,包括日志文件、菜单栏、窗口号、输出域和命令提示行,方便用户输入命令和查看反馈。对于新用户,可以通过两种方式获取帮助:使用`openbook`命令打开在线文档,或者直接在工具的“help”菜单中寻求帮助。

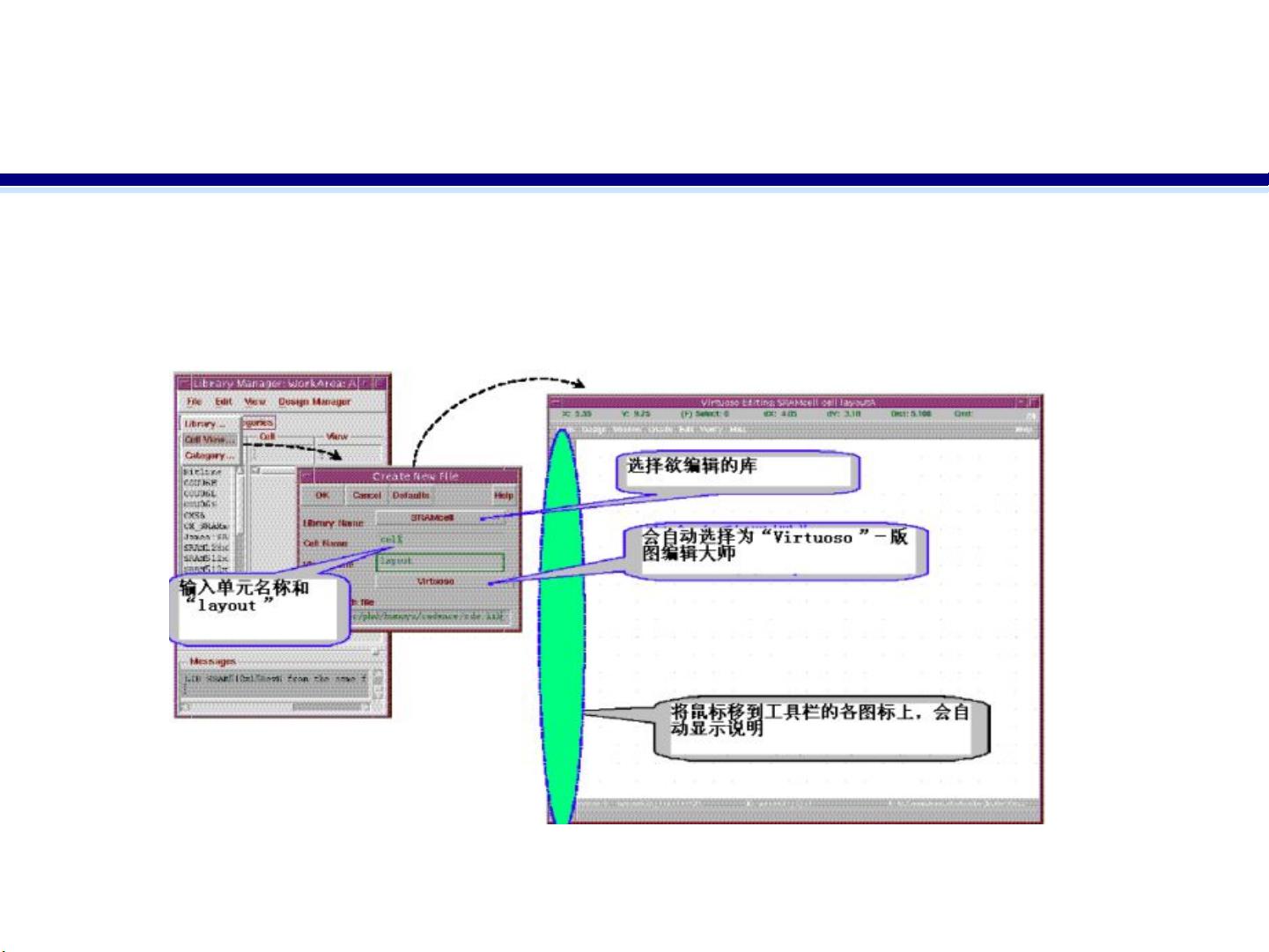

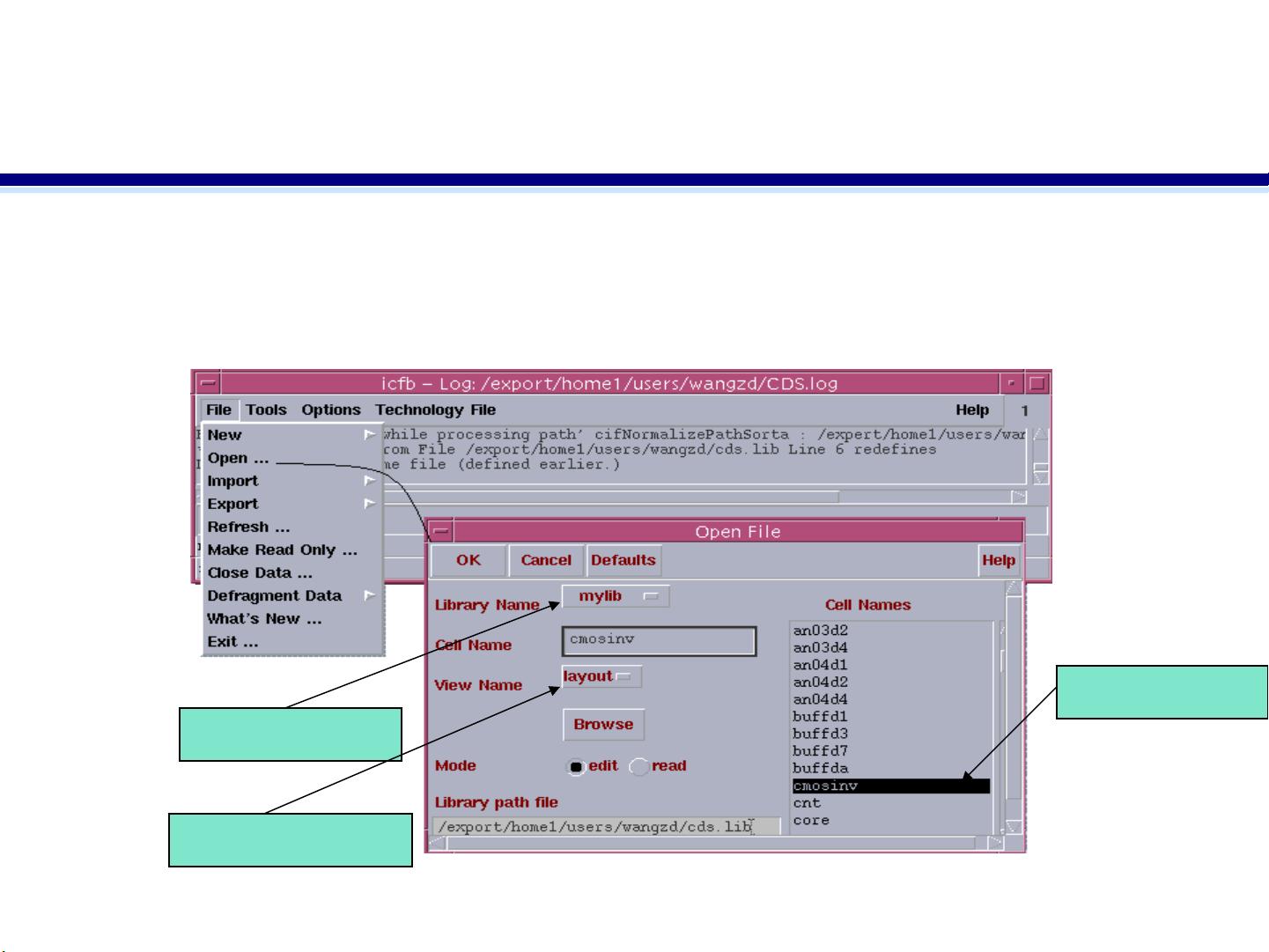

在Virtuoso LE的使用过程中,讲义详细列出了建立设计流程的步骤。首先创建库,然后指定工艺文件,接着建立版图单元,最后打开并编辑版图单元。这些步骤为设计师提供了清晰的操作指南,帮助他们逐步完成IC版图设计。

通过这个讲义,学习者将能深入理解Cadence Virtuoso的工作流程,掌握如何在实际设计中运用这款强大的工具,从而提升集成电路设计的效率和质量。

2021-10-07 上传

2011-03-14 上传

532 浏览量

2009-11-28 上传

2011-08-14 上传

123 浏览量

孤独的猿行客

- 粉丝: 10

- 资源: 3

最新资源

- 查看字符串在不同编码.zip

- springboot-swagger.zip

- schematics-go-sdk:GO SDK for IBM Cloud Schematics服务

- 2张精美3D立体的柱状图PPT模板

- SafeFlashlight

- 雷夫

- hexapdf, 面向 ruby的通用PDF创建和操作.zip

- fylo-landing-page-with-two-column-layout-master

- libspng:简单,现代的libpng替代方案

- m4l15-phan-quyen-Spring-boot-authentic

- 数控直流电源.7z数控直流电源.7z

- 粒子群算法用于解决山地路线规划问题

- install-nginx.tar.gz

- 西蒙游戏

- SanyamSwami123

- Ajax-WikiFinder.zip