MAX10嵌入式存储器用户指南详解

需积分: 5 83 浏览量

更新于2024-07-16

收藏 757KB PDF 举报

"MAX 10 嵌入式存储器用户指南"

本文档是针对Altera公司的MAX 10 FPGA系列的嵌入式存储器的用户指南,主要涵盖了该系列器件的存储器体系结构、特性、操作模式、配置以及设计考量等多个方面。MAX 10 FPGA集成了丰富的内存资源,包括RAM、ROM和移位寄存器等,为用户提供灵活的存储解决方案。

MAX 10嵌入式存储器概述:

MAX 10 FPGA的嵌入式存储器提供了一种高效、低功耗的内存解决方案,可用于各种应用。这些存储器可以被配置为单端口或双端口模式,以满足不同应用场景对读写访问的需求。

MAX 10嵌入式存储器体系结构和功能:

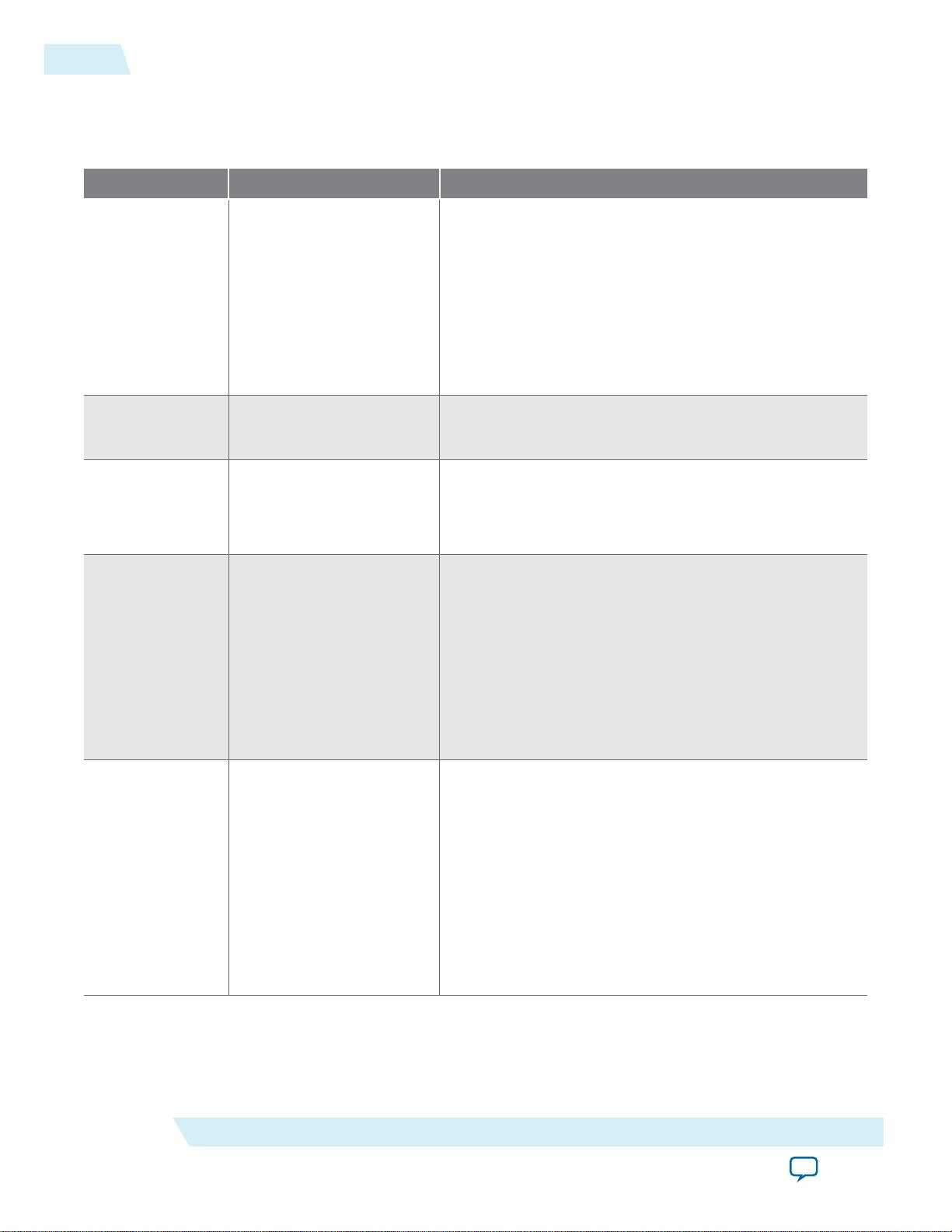

存储器的架构包括控制信号、奇偶校验位、读使能、Read-During-Write机制、字节使能、Packed模式支持、地址时钟使能支持、异步清零等功能。这些特性使得用户能够根据具体需求定制存储器的行为,如实现错误检测、优化读写速度等。

MAX 10嵌入式存储器操作模式:

支持多种操作模式,如同步、异步、带奇偶校验的模式等。这些模式的选择可以影响到读写操作的并发性、数据完整性以及功耗管理。

MAX 10嵌入式存储器时钟模式:

时钟模式的多样性允许用户在不同应用场景下选择最佳的时序方案,例如异步清零、同时读写时的输出数据处理、独立时钟使能等。

MAX 10嵌入式存储器配置:

配置选项包括端口宽度、双端口模式、最大模块深度等,这些配置决定了存储器的容量、访问速度和接口复杂度。

MAX 10嵌入式存储器设计考量:

在设计时需要考虑外部冲突解决、Read-During-Write行为定制、上电状态和存储器初始化、控制时钟以降低功耗,以及选择合适的Read-During-Write输出等关键因素,以确保系统的稳定性和效率。

IP内核参考:

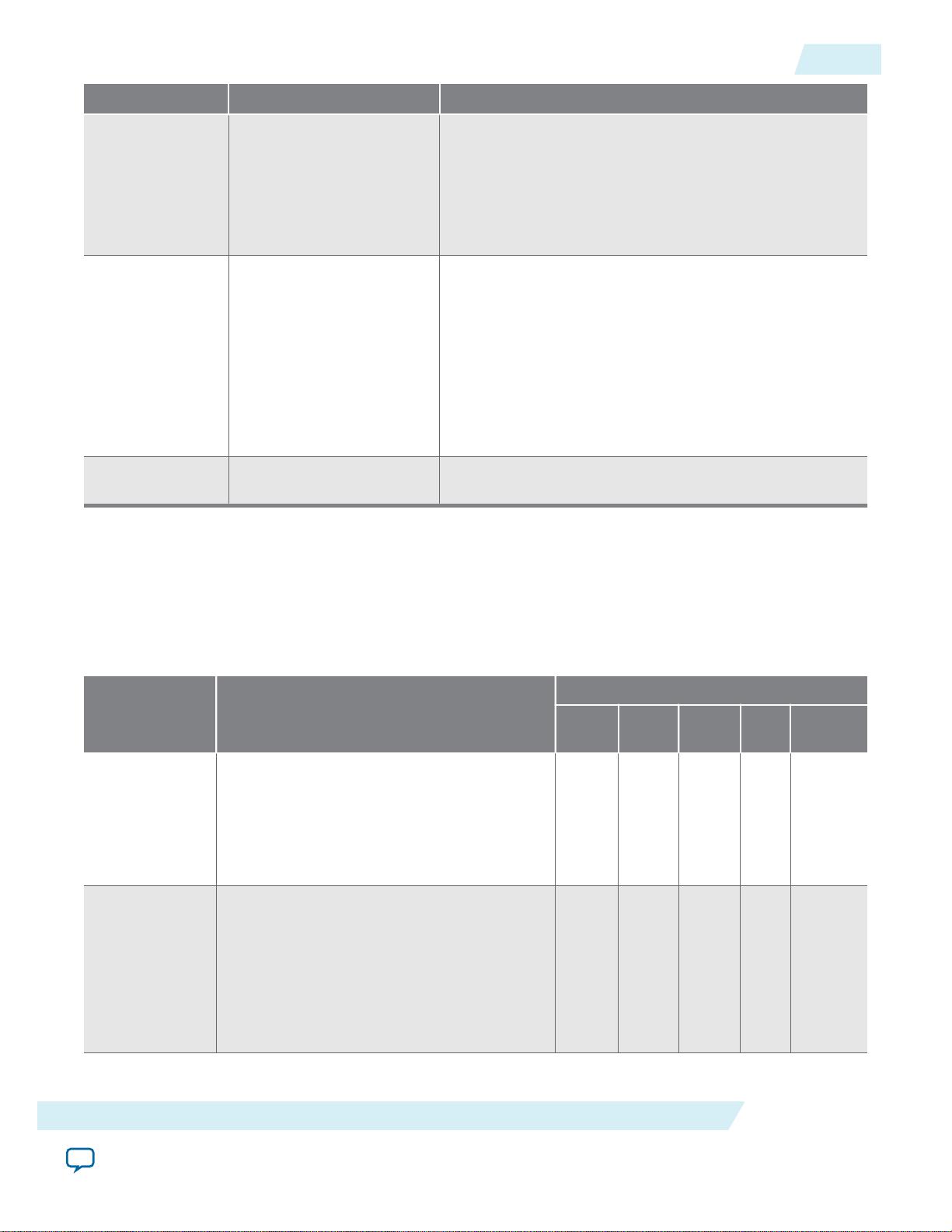

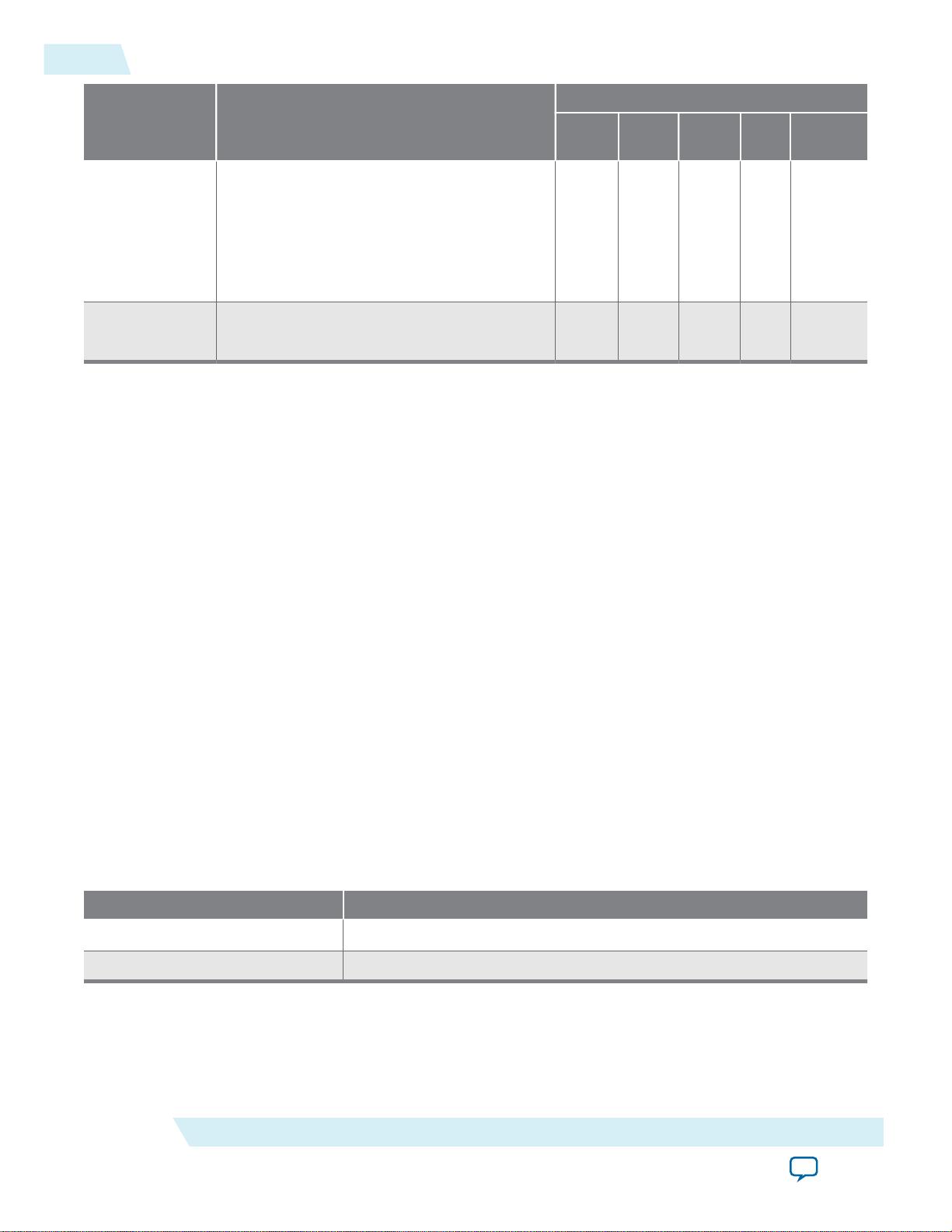

文档还提供了关于1-Port IP内核、2-Port IP内核(包括简单双端口RAM和真双端口RAM)、1-Port ROM IP内核以及2-Port ROM IP内核的详细信号和参数描述,方便用户理解和使用这些内核进行设计。

MAX 10 嵌入式存储器用户指南为开发者提供了全面的指导,帮助他们充分利用MAX 10 FPGA的内存资源,创建高效、可靠的电子系统。通过深入理解这些特性与操作,设计师能够更好地优化他们的硬件设计,满足高性能、低功耗的要求。

2017-11-17 上传

2019-09-17 上传

2016-10-08 上传

2023-10-26 上传

2023-10-05 上传

2023-05-15 上传

2024-01-03 上传

2023-10-24 上传

2024-01-14 上传

Arsery

- 粉丝: 0

- 资源: 5

最新资源

- C语言快速排序算法的实现与应用

- KityFormula 编辑器压缩包功能解析

- 离线搭建Kubernetes 1.17.0集群教程与资源包分享

- Java毕业设计教学平台完整教程与源码

- 综合数据集汇总:浏览记录与市场研究分析

- STM32智能家居控制系统:创新设计与无线通讯

- 深入浅出C++20标准:四大新特性解析

- Real-ESRGAN: 开源项目提升图像超分辨率技术

- 植物大战僵尸杂交版v2.0.88:新元素新挑战

- 掌握数据分析核心模型,预测未来不是梦

- Android平台蓝牙HC-06/08模块数据交互技巧

- Python源码分享:计算100至200之间的所有素数

- 免费视频修复利器:Digital Video Repair

- Chrome浏览器新版本Adblock Plus插件发布

- GifSplitter:Linux下GIF转BMP的核心工具

- Vue.js开发教程:全面学习资源指南