FPGA控制动态数码管:实现数字钟与模块化编程实践

需积分: 0 180 浏览量

更新于2024-08-04

收藏 2.82MB DOCX 举报

实验四:数字钟设计

本实验主要目标是让学生深入了解并实践FPGA技术在数字显示系统中的应用,特别是针对八位动态数码管的控制。以下是核心知识点的详细解析:

1. 动态数码管控制:动态数码管是一种特殊的LED阵列,它利用脉冲驱动每个段来显示数字。在FPGA环境下,你需要编写程序来控制数码管的段选和位选,使得每个数码管能够独立显示数字,通过定时器或计数器驱动数码管的动态更新,确保显示清晰无闪烁。

2. 模块化编程:实验强调模块化编程,即把复杂的问题分解成多个相互独立的模块。这包括数码管驱动模块、按键消抖模块和计数器模块等。通过模块化设计,代码组织更清晰,维护和调试也更为便捷。

3. 按键消抖:由于实际环境中按键信号可能存在短暂的抖动,通过计数器实现按键消抖是关键步骤。通过连续采样按键,如果两次按键状态在一定时间内未改变,就认为是稳定的状态,从而避免误触发。计数器在此过程中起到了延时的作用,确保了按键信号的准确性。

4. 计数器使用:计数器在数字钟中扮演重要角色,如用于定时数码管的刷新频率,或者根据按键输入调整小时、分钟和秒的计数。实验要求精确计时,这就依赖于对计数器性能的精确设置和控制。

5. 数字钟设计:实验的核心内容是设计一个简单的数字钟,除了显示当前的小时、分钟和秒,还要求具备小时翻转(12小时制或24小时制)的功能,并且能通过按键实现校时。这涉及到计数器、数码管显示和按键逻辑的综合运用。

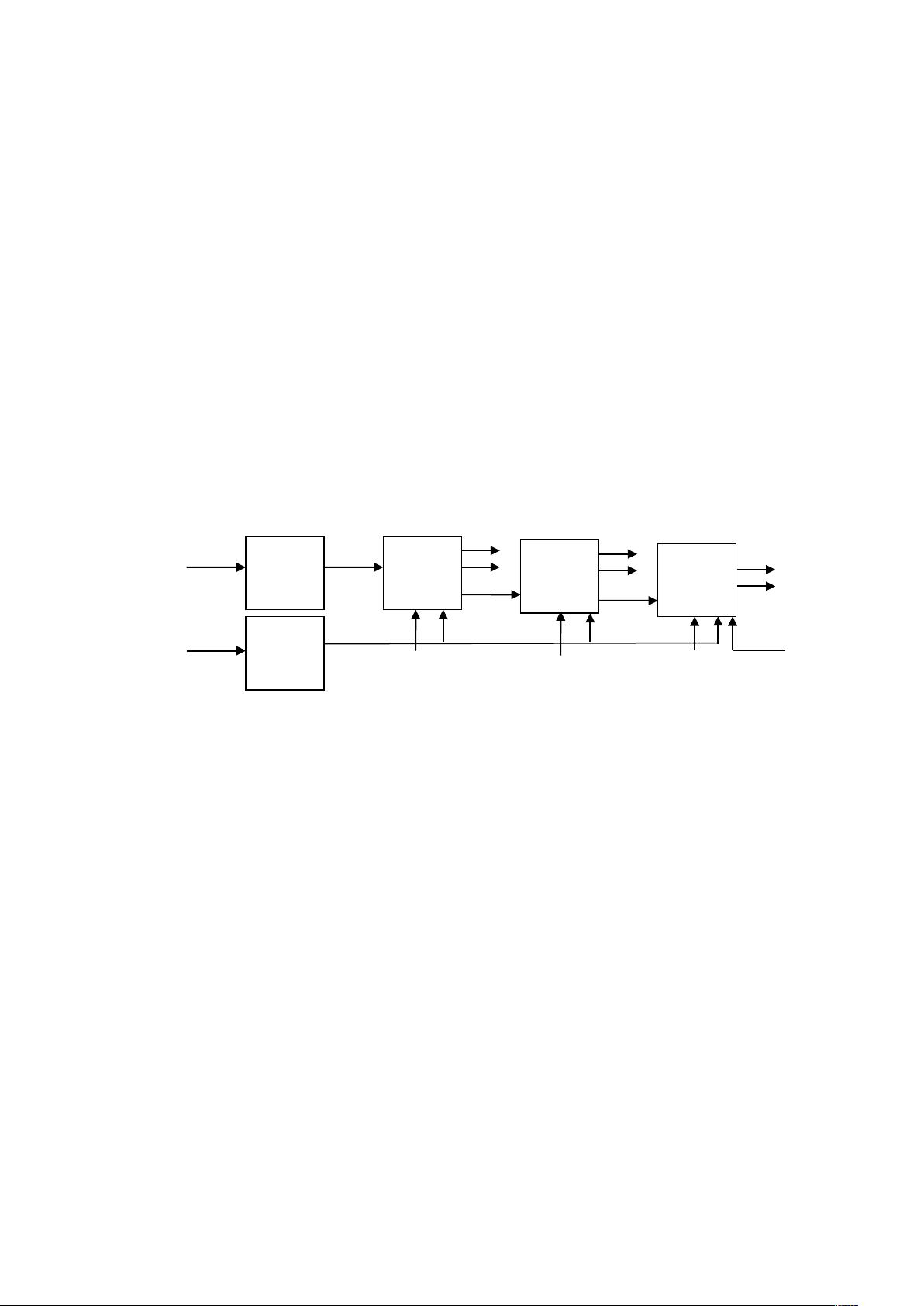

6. 实验原理图:图1展示了数字钟实现的基本架构,包括按键输入处理、消抖电路、计数器和显示控制逻辑。理解这些原理图有助于学生深入理解整个系统的运作机制。

这个实验旨在通过实际操作,让学生掌握FPGA对八位动态数码管的控制方法,熟悉模块化编程,以及理解并实现按键消抖和计数器在数字系统中的作用。通过完成本实验,学生将增强自己的硬件设计能力和软件编程能力,为后续的FPGA项目打下坚实基础。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-09-30 上传

2022-08-08 上传

174 浏览量

163 浏览量

2010-06-19 上传

2023-12-20 上传

FelaniaLiu

- 粉丝: 33

- 资源: 332

最新资源

- RCTF_2015_web500.rar

- react-my-app:学习react

- V4音效4.4.0.4全网最新版(附带安装方法和脉冲样本使用发放).zip

- 电脑软件简历模板大全.rar

- arsenio:ping问题的作者,被arsenio bot遗忘了

- WholesomeHaha.RevenantWww.gazrZ1D

- ctf500--app登录加密算法.rar

- kernelry.github.io:我的博客

- group-by-params:数组使用的简单分组功能,可按参数执行分组。 参数可以是对象键或嵌套路径

- 一个好用的http测试工具

- shortly-angular

- 电脑软件NDM下载器.rar实用

- JS在线汉字笔画练习特效特效代码

- appc-github-client:用于监控Github组织,存储库等的仪表板!

- getopts:解析CLI参数

- 盘古:这是一个演示说明