存储器PCB设计规范与SDRAM布线关键要点

需积分: 48 82 浏览量

更新于2024-07-04

1

收藏 5.62MB DOCX 举报

"存储器PCB设计规范涵盖了电路概括、典型电路设计、布局要求、阻抗要求、线宽要求和等长范围等多个方面。重点介绍了SDRAM的布线规范,包括特性阻抗、数据线组别、数据线与其他线的距离、地线隔离以及布线拓扑结构。此外,还提到了等长布线的规则和误差范围。同时,简述了只读存储器ROM的分类,如FLASH和EEPROM,包括它们的特点、布线要求和布局注意事项。"

正文:

存储器PCB设计是电子系统中至关重要的部分,它直接影响到存储器的性能和系统的稳定性。在设计过程中,需要遵循一系列严格的规范,确保信号传输的准确性和效率。

首先,电路概括涉及存储器的类型,如只读存储器ROM和随机存储器RAM,包括动态RAM (DRAM) 和静态RAM (SRAM)。这些存储器有不同的工作原理和应用场景,对PCB设计的要求也各有不同。

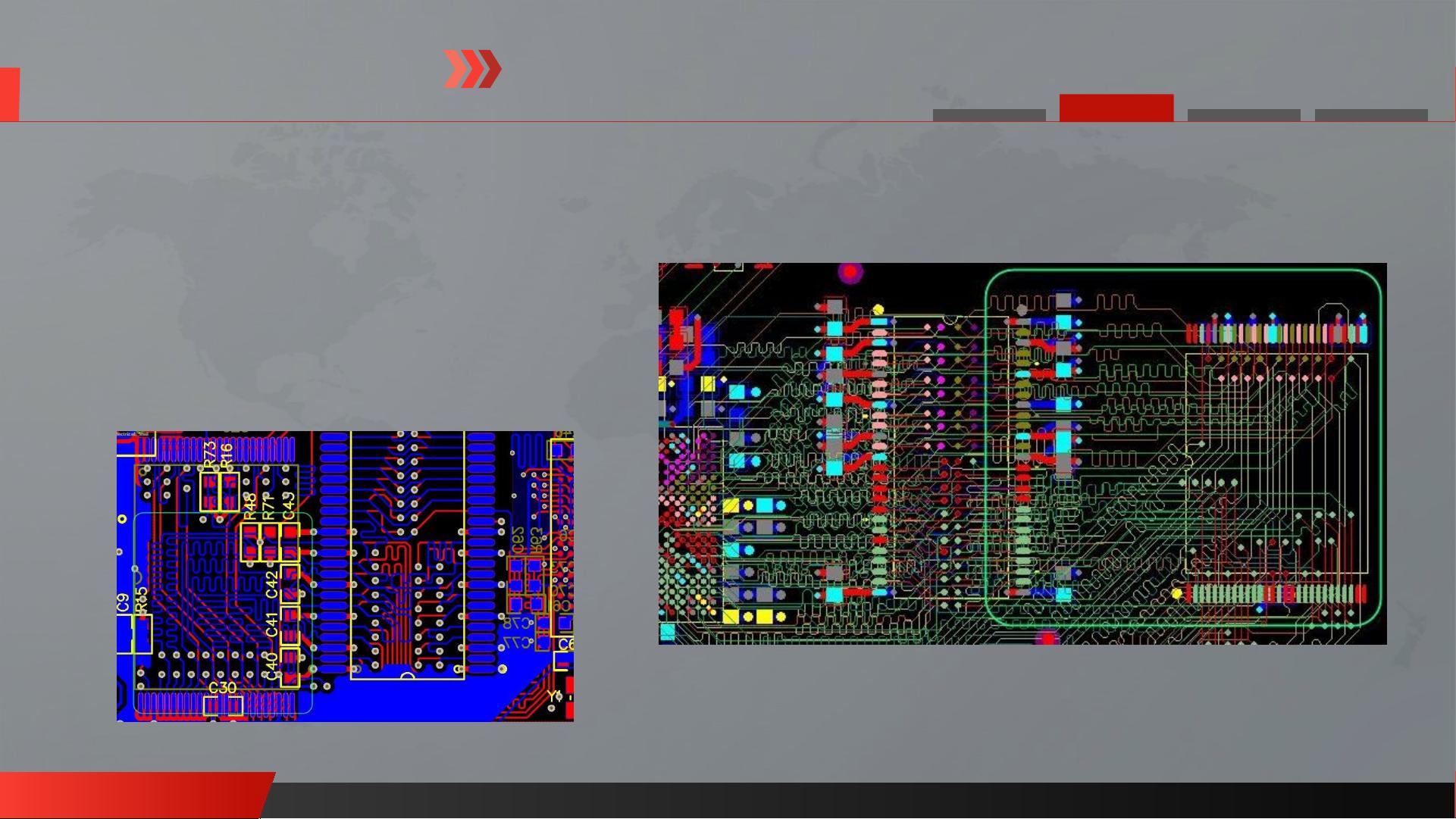

对于SDRAM的PCB设计,其特性阻抗通常设定为50欧姆,以保证信号的完整传输。数据线被分组,例如D0到D7与LDQM一组,D8到D15与HDQM一组,尽可能在同一层布线,以减少干扰。数据线、地址线、控制线和时钟线之间应保持至少20mil以上的距离,或者采用3W的间距规则,以提供足够的信号隔离。在空间允许的情况下,添加地线进行隔离可以进一步降低干扰,推荐的地线宽度在15-30mil之间。完整的参考平面有助于提高信号质量,而布线拓扑结构通常采用远端分支,T点(过孔)位于两片SDRAM之间。

SDRAM的等长布线是确保系统时序同步的关键。所有数据线被归类为sdram_data_bus,地址线、控制线和时钟线归为sdram_addr_bus。所有信号线需要参照时钟线的长度进行等长调整,数据线的误差范围控制在±50mil,地址线的误差范围控制在±100mil。

只读存储器ROM,如FLASH和EEPROM,也有特定的布线和布局要求。FLASH通常以菊花链形式布局,特性阻抗同样为50欧,线间距保持3W,等长范围为±100mil。而EEPROM,作为可擦可编程的ROM,需要靠近主芯片布局以缩短信号路径,同时需要添加去耦合电容以滤除电源噪声。它的管脚定义包括地址选择、串行数据和时钟等,其布局要求是尽量靠近主芯片以减小延迟。

存储器PCB设计规范是一个涉及多种因素的复杂过程,包括但不限于电路类型、阻抗匹配、线宽控制、地线规划和等长布线。理解并严格遵守这些规范,才能确保存储器在PCB上的高效、稳定运行。

2021-01-19 上传

2023-05-11 上传

2024-02-04 上传

2023-05-18 上传

2023-07-23 上传

2023-07-14 上传

2023-11-05 上传

Mesl·

- 粉丝: 507

- 资源: 18

最新资源

- 平尾装配工作平台运输支撑系统设计与应用

- MAX-MIN Ant System:用MATLAB解决旅行商问题

- Flutter状态管理新秀:sealed_flutter_bloc包整合seal_unions

- Pong²开源游戏:双人对战图形化的经典竞技体验

- jQuery spriteAnimator插件:创建精灵动画的利器

- 广播媒体对象传输方法与设备的技术分析

- MATLAB HDF5数据提取工具:深层结构化数据处理

- 适用于arm64的Valgrind交叉编译包发布

- 基于canvas和Java后端的小程序“飞翔的小鸟”完整示例

- 全面升级STM32F7 Discovery LCD BSP驱动程序

- React Router v4 入门教程与示例代码解析

- 下载OpenCV各版本安装包,全面覆盖2.4至4.5

- 手写笔画分割技术的新突破:智能分割方法与装置

- 基于Koplowitz & Bruckstein算法的MATLAB周长估计方法

- Modbus4j-3.0.3版本免费下载指南

- PoqetPresenter:Sharp Zaurus上的开源OpenOffice演示查看器