Vivado IDE完全指南:掌握FPGA设计利器

需积分: 10 71 浏览量

更新于2024-07-16

收藏 3.79MB PDF 举报

“这是一份关于Vivado设计套件的用户指南,特别关注了Vivado IDE的使用,包括软件的基本操作和菜单功能,适用于学习FPGA设计的初学者。文档涵盖了2017.3和2017.4两个版本的更新内容,详细介绍了Vivado IDE的各种功能和设置。”

在Vivado Design Suite中,Xilinx的Vivado是一款强大的集成开发环境(IDE),用于实现Field Programmable Gate Array(FPGA)的设计、综合、仿真和调试。这份用户指南详细阐述了如何有效地使用Vivado IDE,帮助开发者更好地理解和掌握其工作流程。

1. Vivado IDE的使用:

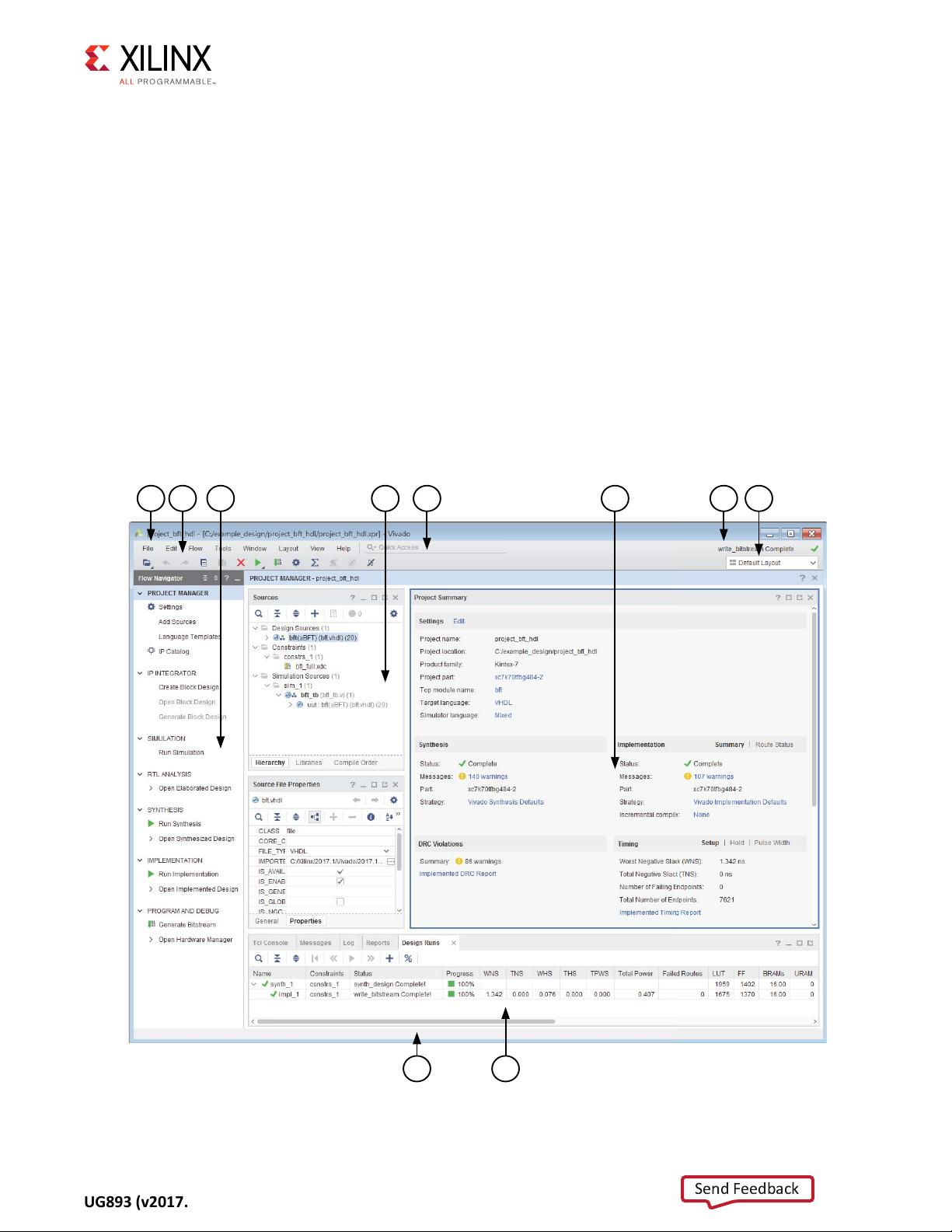

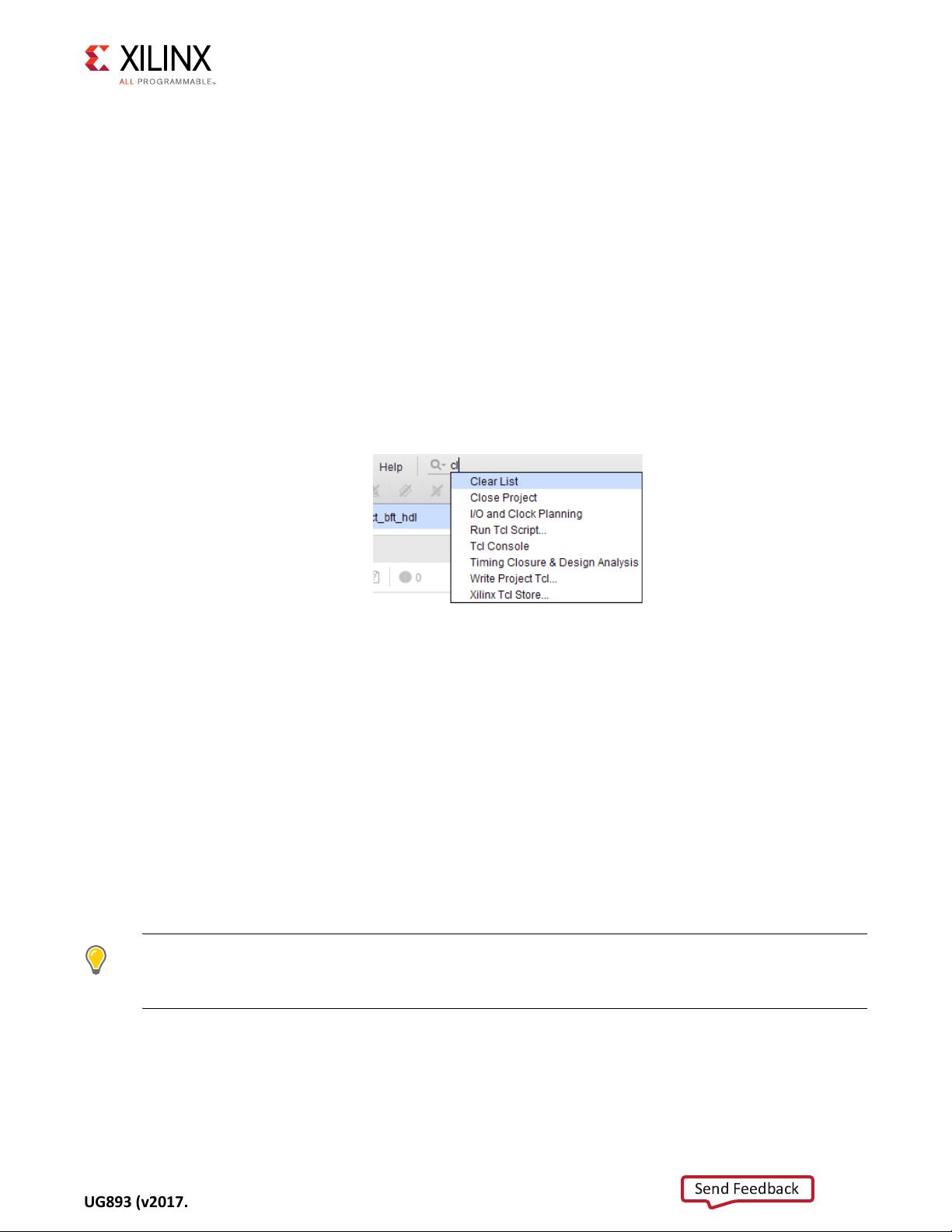

Vivado IDE提供了一个统一的界面,让用户可以进行项目管理、源代码编辑、逻辑综合、布局布线以及硬件调试。用户可以通过菜单栏访问各种功能,例如创建新项目、添加源文件、配置目标设备等。学习Vivado IDE的基本操作是FPGA设计的基础。

2. 使用Vivado IDE的窗口视图:

用户指南中提到了Window Views,这部分内容可能涉及如何定制工作空间,如切换和排列不同的工具窗口,如Sources、Hierarchy、Schematic等,以便更高效地进行设计工作。

3. Sources窗口与Syntax Error Files:

在Sources窗口中,用户可以管理项目中的所有源文件,包括Verilog或VHDL代码、约束文件等。新增的Syntax Error Files折叠项帮助用户快速定位并修复语法错误,提高设计的正确性。

4. Reports视图和报告策略:

Reports视图提供了设计流程中的各种报告,包括综合报告、时序分析报告等。了解如何设置报告策略可以帮助用户在设计的不同阶段获取所需的信息,优化设计性能。

5. Text Editor的使用:

文档更新了Text Editor的新功能,可能包括代码高亮、自动完成、查找替换等特性,这些对于编写和调试代码非常有用。此外,还介绍了如何自定义文本编辑器的设置,以满足个人的工作习惯。

6. Schematic窗口显示设置:

Schematic窗口用于查看和编辑设计的逻辑结构。新增的选项可能涉及到显示设置的改进,如元件库的选择、图层控制等,以增强可视化体验。

7. 生成额外报告:

报告busskew的介绍意味着用户可以生成关于总线延迟的报告,这对于理解和优化系统时序至关重要。

8. 环境配置:

学习如何配置环境,包括创建运行策略和报告策略,有助于用户按照特定需求定制设计流程,提高工作效率。

9. Vivado IDE的更新:

2017.1版本更新了整个IDE的外观和感觉,使得界面更加现代化。同时,更新了Getting Started页面,增加了对可配置Zynq UltraScale+ MPSoC设计的支持,反映了Vivado对高级SoC设计的支持。

10. 配置项目设置:

在“Configuring Project Settings”的Settings对话框中进行了更新,用户可以在这里设定项目的具体属性,如目标器件、编译标准等,确保设计满足特定的需求和约束。

通过深入学习这份Vivado用户指南,无论是初学者还是有经验的开发者,都能提升在FPGA设计领域的技能,熟练掌握Vivado工具,从而更有效地实现复杂的硬件设计。

239 浏览量

2022-06-25 上传

2022-09-23 上传

2022-07-13 上传

2013-07-11 上传

2019-05-27 上传

2022-05-09 上传

点击了解资源详情

点击了解资源详情

lyghit

- 粉丝: 1

- 资源: 15

最新资源

- MATLAB新功能:Multi-frame ViewRGB制作彩色图阴影

- XKCD Substitutions 3-crx插件:创新的网页文字替换工具

- Python实现8位等离子效果开源项目plasma.py解读

- 维护商店移动应用:基于PhoneGap的移动API应用

- Laravel-Admin的Redis Manager扩展使用教程

- Jekyll代理主题使用指南及文件结构解析

- cPanel中PHP多版本插件的安装与配置指南

- 深入探讨React和Typescript在Alias kopio游戏中的应用

- node.js OSC服务器实现:Gibber消息转换技术解析

- 体验最新升级版的mdbootstrap pro 6.1.0组件库

- 超市盘点过机系统实现与delphi应用

- Boogle: 探索 Python 编程的 Boggle 仿制品

- C++实现的Physics2D简易2D物理模拟

- 傅里叶级数在分数阶微分积分计算中的应用与实现

- Windows Phone与PhoneGap应用隔离存储文件访问方法

- iso8601-interval-recurrence:掌握ISO8601日期范围与重复间隔检查