32768Hz晶体振荡器驱动的数字钟与智能分频计数器设计

需积分: 9 140 浏览量

更新于2024-07-25

收藏 363KB DOC 举报

本文档主要介绍了数字钟与智能台灯的设计与实现,以数字电子技术课程设计为背景,探讨了数字钟的具体实现方案。设计目标旨在深化理解各种芯片的逻辑功能和使用,以及数字钟设计方法,包括计数器的级联应用。此外,还涉及了数字系统的设计、测试、制作和布线技能的提升。

设计要求详细规定了数字钟的功能特性,如精确显示时、分、秒,具备校时功能,能进行单独校时,整点前10秒报时,并且要求走时准确。设计过程中需要绘制电路原理图,选择合适的元器件并提供清单,同时强调实际操作和问题解决能力的培养,通过编写设计报告记录整个过程。

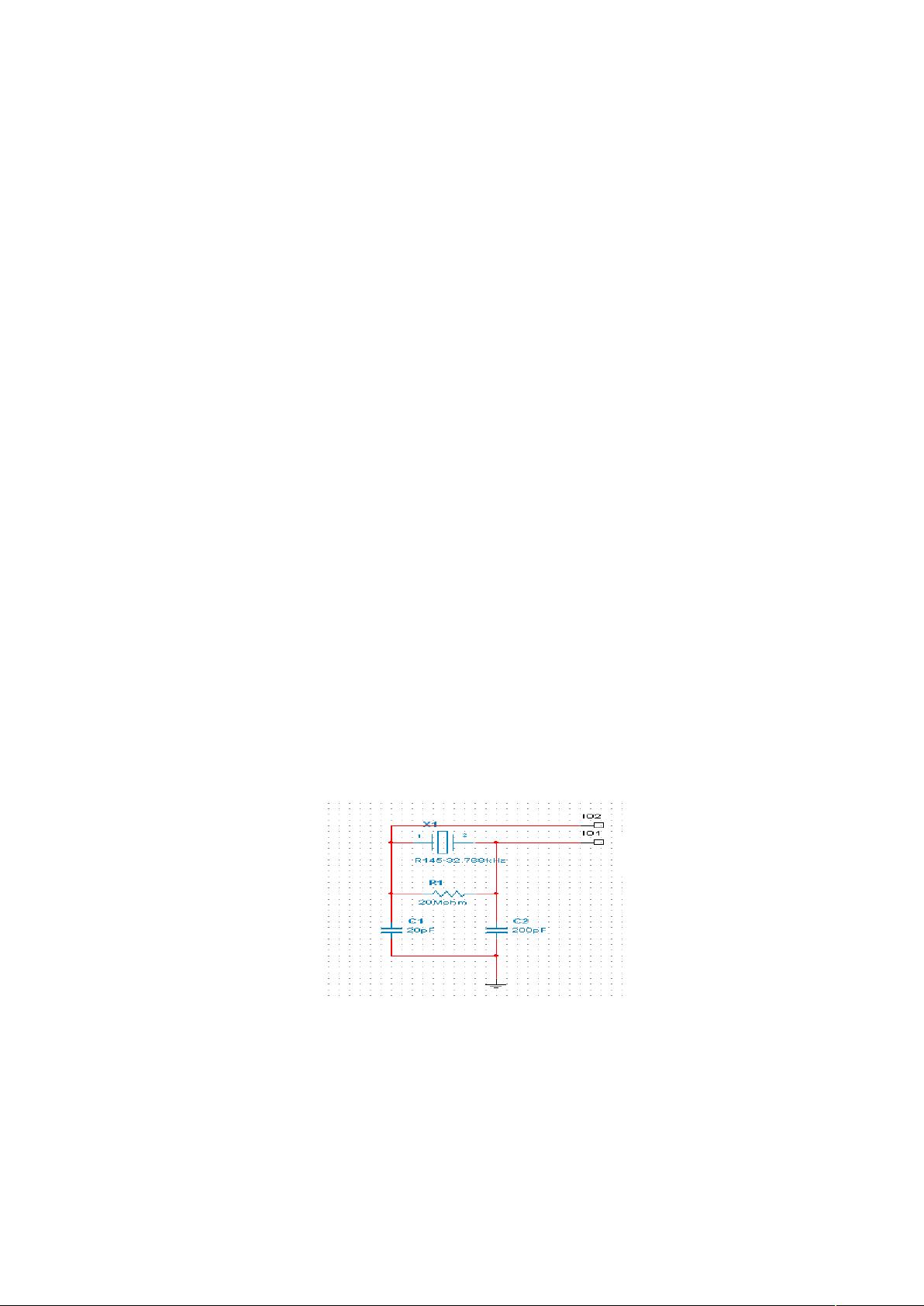

在总体设计方面,数字钟的核心是计数电路,利用石英晶体振荡器提供稳定且频率精确的32768Hz信号。这个信号经过分频器电路,如74LS4060和74LS250的二分频,将高频信号降低到1Hz,以便于秒计数器进行计数。时间计数器电路则由秒、分、时的各个位计数器组成,其中秒和分的计数器采用60进制,确保时间的准确性。

通过这些设计,不仅展示了基本的数字电路设计技巧,还涉及到了信号处理和系统集成的知识。智能台灯虽然在标题中提及,但在这篇文档中并未详细讨论,可能是在实际应用中作为辅助设备,如定时开关或照明控制等功能,与数字钟形成一个完整的智能家居解决方案。

本设计项目深入浅出地涵盖了从理论到实践的各个环节,是一次宝贵的学习和实践机会,对于提高学生的电子设计和调试能力有着重要意义。

720 浏览量

点击了解资源详情

点击了解资源详情

2023-04-16 上传

330 浏览量

2022-06-03 上传

121 浏览量

810 浏览量

189 浏览量

u010849604

- 粉丝: 0

- 资源: 1

最新资源

- 基于ADO数据访问技术的等边角钢参数化设计.doc

- 如何实现无刷新的DropdownList联动效果

- 网络工程投标书样本2009

- VS2005(c#)项目调试问题解决方案集锦(五)

- VS2005(c#)项目调试问题解决方案集锦(四)

- 《python核心笔记》

- H.264_中英文对照翻译(AVS264 V1.0)

- java cook book

- PHP在Web开发领域的优势

- Spring 入门书籍

- 《微内核工作流引擎体系结构与部分解决方案参考》

- PHP初学者头疼问题总结

- ArcObjects+GIS应用开发——基于C#.NET

- 工作流引擎核心调度算法与PetriNet_胡长城.pdf

- 《工作流模型分析》胡长城

- c8051f020文档资料