Verilog基础教程:模块、数据类型与变量解析

需积分: 38 13 浏览量

更新于2024-07-15

收藏 1.53MB PDF 举报

"这篇文档是关于Verilog语言的基础模块介绍,涵盖了Verilog中的基本概念,如数据类型、运算符和组合逻辑,对于FPGA初学者非常有帮助。文档由芯驿电子科技(上海)有限公司发布,来自黑金动力社区。"

在Verilog编程中,理解和掌握基础模块是非常重要的,它构成了设计复杂FPGA系统的基石。首先,让我们深入探讨数据类型:

1. **数据类型**:

- **常量**:Verilog提供了多种表示常量的方式,包括整数(使用b, o, d, h前缀),X和Z值(分别代表不定和高阻状态),以及下划线(用于分隔位数,提高代码可读性)。例如,8’b00001111表示一个8位的二进制整数,4’ha表示4位的十六进制整数。

- **参数(parameter)**:parameter用于定义模块级别的常量,可以提高代码的可读性和可维护性。它们可以在模块调用时传递,如`module rom #(parameter depth = 15, parameter width = 8) ...`,并能在实例化时修改。

- **局部参数(localparam)**:与parameter类似,但localparam仅限于定义它的模块内部使用,不用于参数传递,常用于状态机的状态定义。

2. **变量**:

- **Wire型**:Wire变量代表逻辑信号,用于表示硬件元素间的连接,不能存储数据,只能反映输入的最新值。例如,`wire [width-1:0] data`定义了一个宽度为width的Wire型变量。

接下来是运算符和组合逻辑部分:

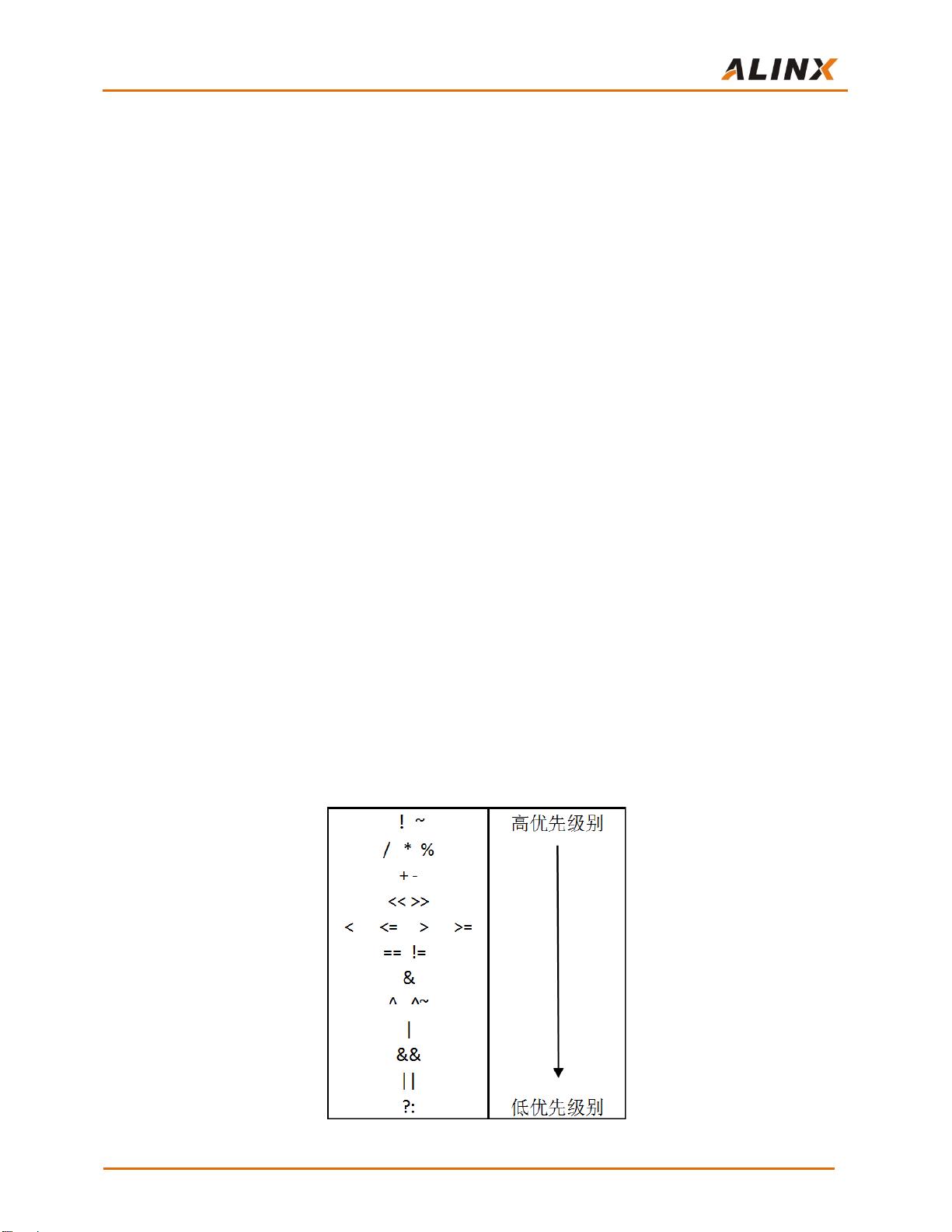

2.2.2 **运算符**:Verilog支持多种运算符,包括算术、逻辑、比较和位操作等。这些运算符用于组合逻辑电路的设计,如加法、减法、逻辑非、逻辑与、逻辑或、位移等操作。

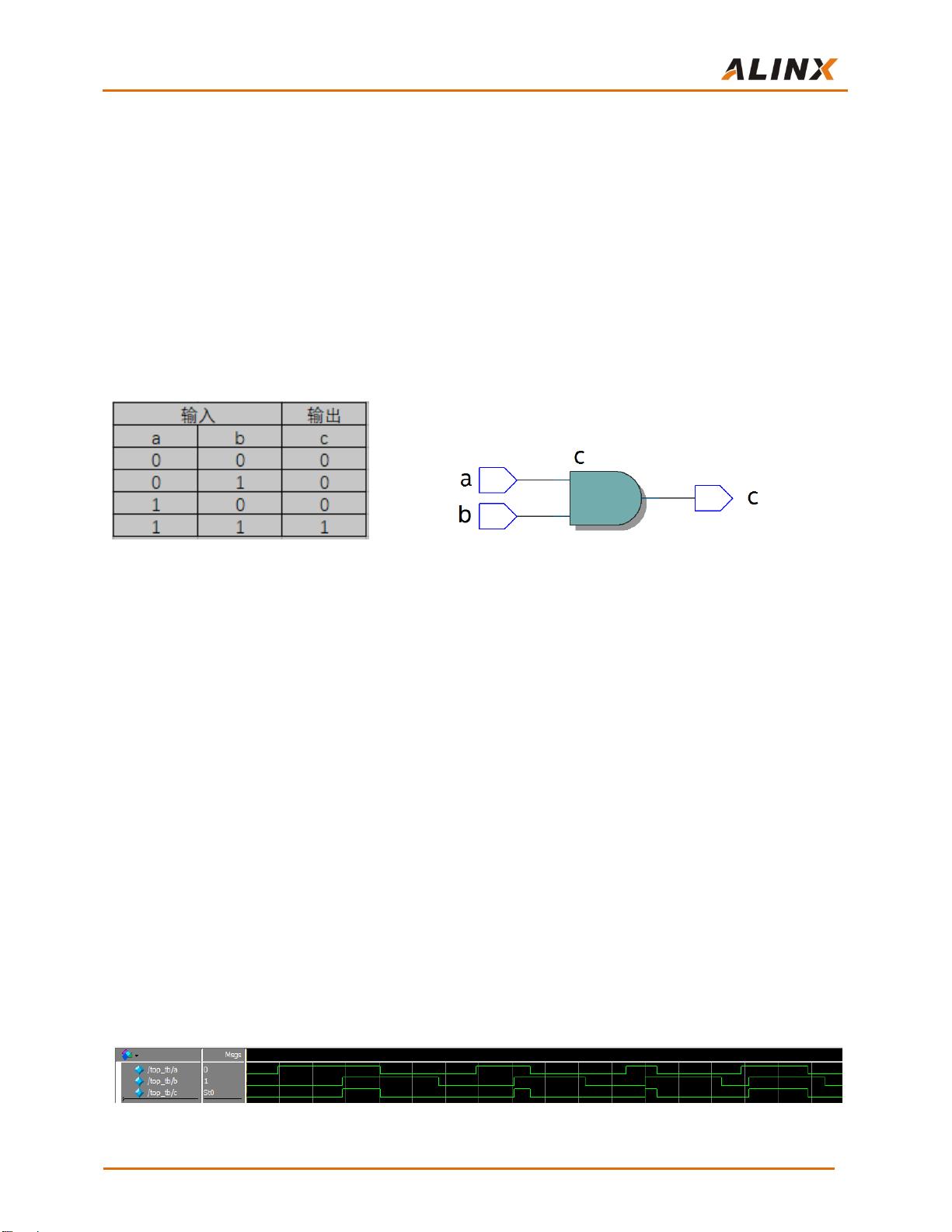

3. **组合逻辑**:在Verilog中,通过运算符和逻辑表达式可以构建复杂的组合逻辑电路。例如,可以使用`assign`语句定义即时赋值,实现组合逻辑的功能。

在实际设计中,理解并熟练运用这些基础模块是至关重要的,它们可以帮助你构建出各种功能的数字系统。在深入学习FPGA设计时,必须扎实地掌握这些基础知识,以便更好地实现逻辑电路的功能。通过阅读这篇文档,你将能够开始编写基本的Verilog代码,为后续的FPGA设计打下坚实的基础。

2021-09-29 上传

2021-03-31 上传

2021-10-12 上传

2019-07-30 上传

2021-09-27 上传

2021-09-14 上传

2019-08-16 上传

2019-05-21 上传

2008-09-28 上传