Functional Description

DS312-2 (v3.4) November 9, 2006 www.xilinx.com 19

Product Specification

R

These differences are outlined for each package, such as

pins that are unconnected on one device but connected on

another in the same package or pins that are dedicated

inputs on one package but full I/O on another. When design-

ing the printed circuit board (PCB), plan for potential future

upgrades and package migration.

The Spartan-3E family is not pin-compatible with any previ-

ous Xilinx FPGA family.

Dedicated Inputs

Dedicated Inputs are IOBs used only as inputs. Pin names

designate a Dedicated Input if the name starts with IP, for

example, IP or IP_Lxxx_x. Dedicated inputs retain the full

functionality of the IOB for input functions with a single

exception for differential inputs (IP_Lxxx_x). For the differ-

ential Dedicated Inputs, the on-chip differential termination

is not available. To replace the on-chip differential termina-

tion, choose a differential pair that supports outputs

(IO_Lxxx_x) or use an external 100Ω termination resistor on

the board.

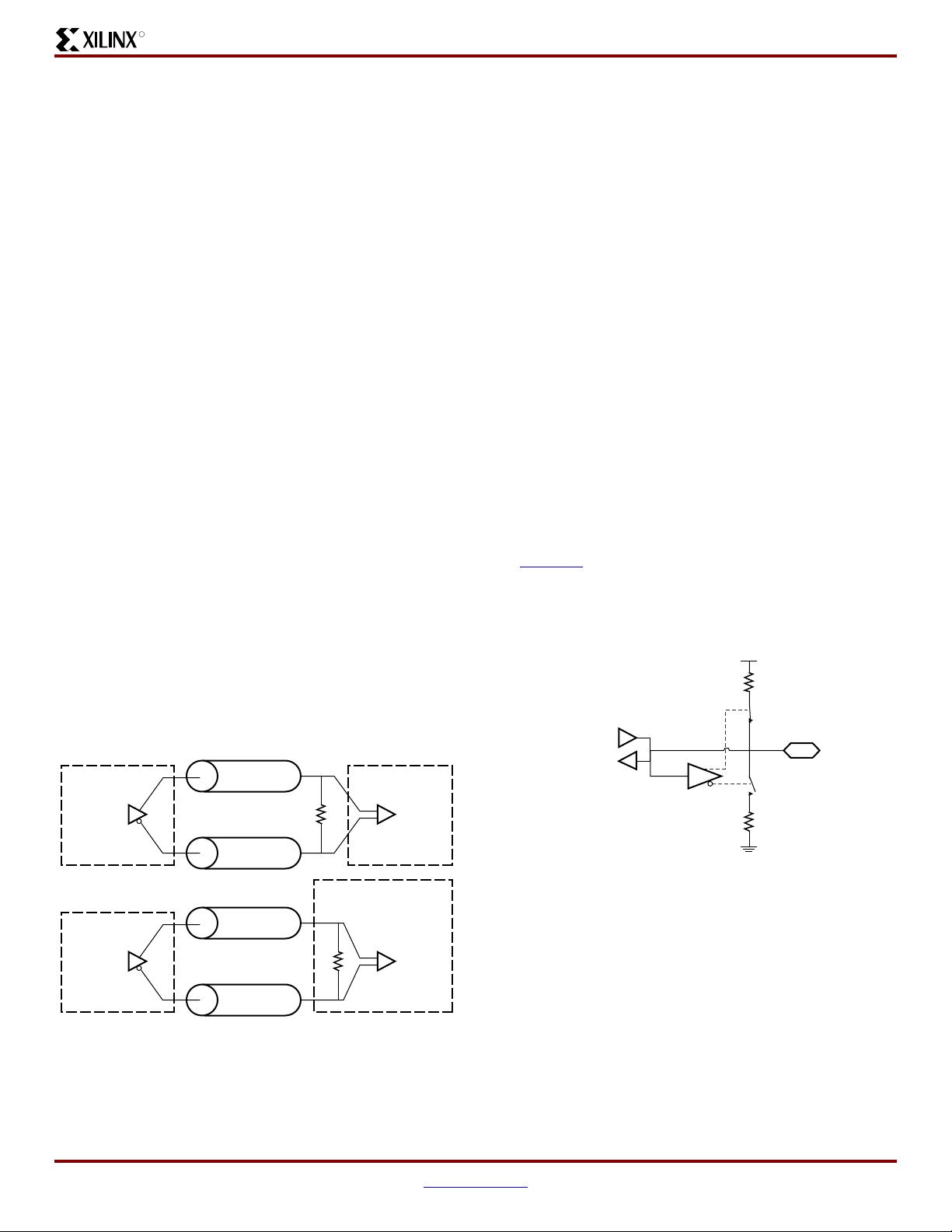

ESD Protection

Clamp diodes protect all device pads against damage from

Electro-Static Discharge (ESD) as well as excessive voltage

transients. Each I/O has two clamp diodes: one diode

extends P-to-N from the pad to V

CCO

and a second diode

extends N-to-P from the pad to GND. During operation,

these diodes are normally biased in the off state. These

clamp diodes are always connected to the pad, regardless

of the signal standard selected. The presence of diodes lim-

its the ability of Spartan-3E I/Os to tolerate high signal volt-

ages. The V

IN

absolute maximum rating in Tabl e 7 2 of DC

and Switching Characteristics (Module 3) specifies the

voltage range that I/Os can tolerate.

Supply Voltages for the IOBs

The IOBs are powered by three supplies:

1. The V

CCO

supplies, one for each of the FPGA’s I/O

banks, power the output drivers. The voltage on the

V

CCO

pins determines the voltage swing of the output

signal.

2. V

CCINT

is the main power supply for the FPGA’s internal

logic.

3. V

CCAUX

is an auxiliary source of power, primarily to

optimize the performance of various FPGA functions

such as I/O switching.

I/O and Input-Only Pin Behavior During

Power-On, Configuration, and User Mode

In this section, all behavior described for I/O pins also

applies to input-only pins and dual-purpose I/O pins that are

not actively involved in the currently-selected configuration

mode.

All I/O pins have ESD clamp diodes to their respective V

CCO

supply and from GND, as shown in Figure 5. The V

CCINT

(1.2V), V

CCAUX

(2.5V), and V

CCO

supplies can be applied in

any order. Before the FPGA can start its configuration pro-

cess, V

CCINT

, V

CCO

Bank 2, and V

CCAUX

must have reached

their respective minimum recommended operating levels

indicated in Tabl e 7 3 . At this time, all output drivers are in a

high-impedance state. V

CCO

Bank 2, V

CCINT

, and V

CCAUX

serve as inputs to the internal Power-On Reset circuit

(POR).

A Low level applied to the HSWAP input enables pull-up

resistors on user-I/O and input-only pins from power-on

throughout configuration. A High level on HSWAP disables

the pull-up resistors, allowing the I/Os to float. HSWAP con-

tains a weak pull-up and defaults to High if left floating. As

soon as power is applied, the FPGA begins initializing its

configuration memory. At the same time, the FPGA inter-

nally asserts the Global Set-Reset (GSR), which asynchro-

nously resets all IOB storage elements to a default Low

state. Also see Pin Behavior During Configuration.

Upon the completion of initialization and the beginning of

configuration, INIT_B goes High, sampling the M0, M1, and

M2 inputs to determine the configuration mode. Configura-

tion data is then loaded into the FPGA. The I/O drivers

remain in a high-impedance state (with or without pull-up

resistors, as determined by the HSWAP input) throughout

configuration.

At the end of configuration, the GSR net is released, placing

the IOB registers in a Low state by default, unless the

loaded design reverses the polarity of their respective SR

inputs.

The Global Three State (GTS) net is released during

Start-Up, marking the end of configuration and the begin-

ning of design operation in the User mode. After the GTS

net is released, all user I/Os go active while all unused I/Os