Quartus实现:表决器与代码转换器设计与仿真

"该文档包含了两个数字电子学实验项目,分别是使用Quartus软件实现的四人表决器和代码转换器的设计。实验中涉及到逻辑门电路、数据选择器、卡诺图化简以及数字编码器的转换。"

在这两个实验项目中,Quartus作为主要的开发工具,被用来设计和仿真数字电路。Quartus是Altera公司(现Intel FPGA)开发的一款综合、布局布线、仿真和编程的集成开发环境,广泛应用于FPGA(现场可编程门阵列)的设计。

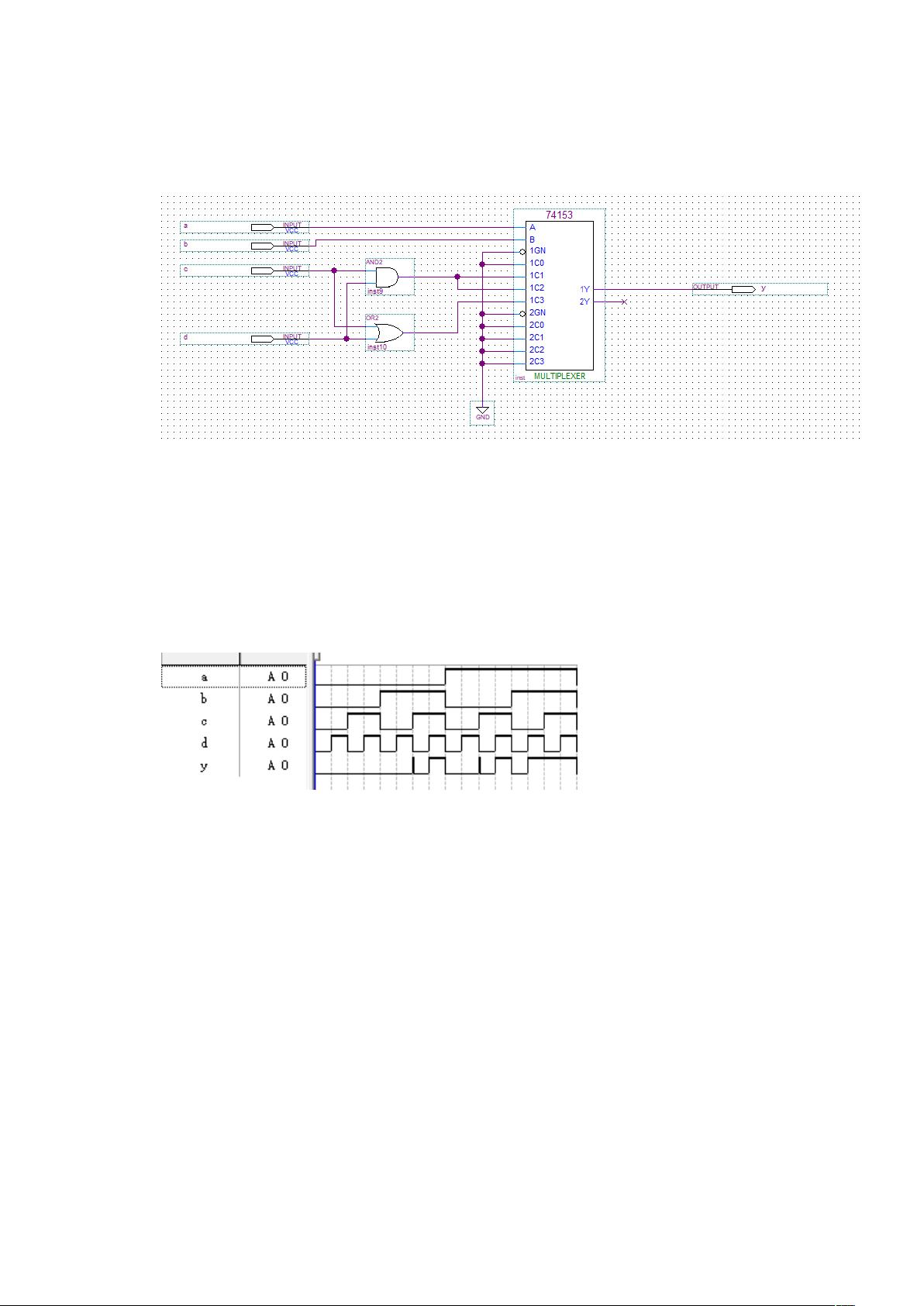

选题1是四人表决器的设计。表决器是一种能够根据输入信号的数量来决定输出状态的逻辑电路。在这个项目中,使用了74153作为数据选择器。74153是一个双四输入译码器,它可以依据两个控制输入A和B的组合,选择四个输入信号中的一个进行输出。设计者首先通过编写真值表,然后利用卡诺图化简逻辑函数,简化了电路设计。电路的逻辑功能是:当输入的四个信号中至少有三个为高电平时,输出为高电平;否则,输出为低电平。在实现过程中,利用与门和或门电路来满足不同的输入条件。

选题2是代码转换器的设计。代码转换器主要用于不同数字编码之间的转换,例如8421码、5421码和余三码。74283是一个四位二进制加法器,被用来实现这些转换。设计者通过对各种转换条件的分析,利用门电路和控制线M3M2M1实现了不同编码之间的自动转换。例如,8421码转5421码时,当输入大于等于5时,添加0011,通过控制线在特定条件下触发转换。同时,提供了各种转换模式的仿真波形图,以验证转换器的正确性。

这两个实验项目深入实践了数字逻辑设计的基本原理,包括逻辑门的使用、真值表的构建、卡诺图化简、逻辑电路的仿真和FPGA编程,这些都是数字系统设计的基础技能。通过Quartus这样的专业工具,学生能够更直观地理解和掌握数字电子学的知识,并具备实际设计和实现数字系统的初步能力。

153 浏览量

1798 浏览量

1780 浏览量

509 浏览量

153 浏览量

969 浏览量

268 浏览量

109 浏览量

m0_51955757

- 粉丝: 0

最新资源

- 小学水墨风学校网站模板设计

- 深入理解线程池的实现原理与应用

- MSP430编程代码集锦:实用例程源码分享

- 绿色大图幻灯商务响应式企业网站开发源码包

- 深入理解CSS与Web标准的专业解决方案

- Qt/C++集成Google拼音输入法演示Demo

- Apache Hive 0.13.1 版本安装包详解

- 百度地图范围标注技术及应用

- 打造个性化的Windows 8锁屏体验

- Atlantis移动应用开发深度解析

- ASP.NET实验教程:源代码详细解析与实践

- 2012年工业观察杂志完整版

- 全国综合缴费营业厅系统11.5:一站式缴费与运营管理解决方案

- JAVA原生实现HTTP请求的简易指南

- 便携PDF浏览器:随时随地快速查看文档

- VTF格式图片编辑工具:深入起源引擎贴图修改