Verilog HDL实现的数字频率计设计解析

版权申诉

"该课程设计涉及的是基于Verilog HDL的数字频率计的设计与实现,主要针对计算机与通信工程学院网络工程专业的学生进行。学生需要完成数字频率计前端信号的放大整形处理,Verilog HDL代码的设计实现,以及在CPLD/FPGA上的制作。课程目标包括理解课题背景和意义,掌握计算机组成原理的设计方法,编写课程设计报告,并展示设计和实验结果。学生需要以严谨的态度查阅文献,进行设计和实现。最终需提交课程设计报告和源程序作为成果。课程设计的评估包括创新性、内容掌握程度、完成情况、动手能力、文字表达、学习态度和规范要求等方面。"

本文档首先介绍了电子技术中频率测量的重要性,特别是电子计数器在频率测量中的作用,它能以高精度、便捷性和快速度测量频率。电子计数器有两种测量方式:直接测频法和间接测频法,分别适用于不同频率范围的信号。

接下来,文档简述了Verilog HDL语言,这是一种用于硬件描述的语言,常用于数字系统的建模和设计。学生将学习如何使用Verilog HDL来设计数字频率计。

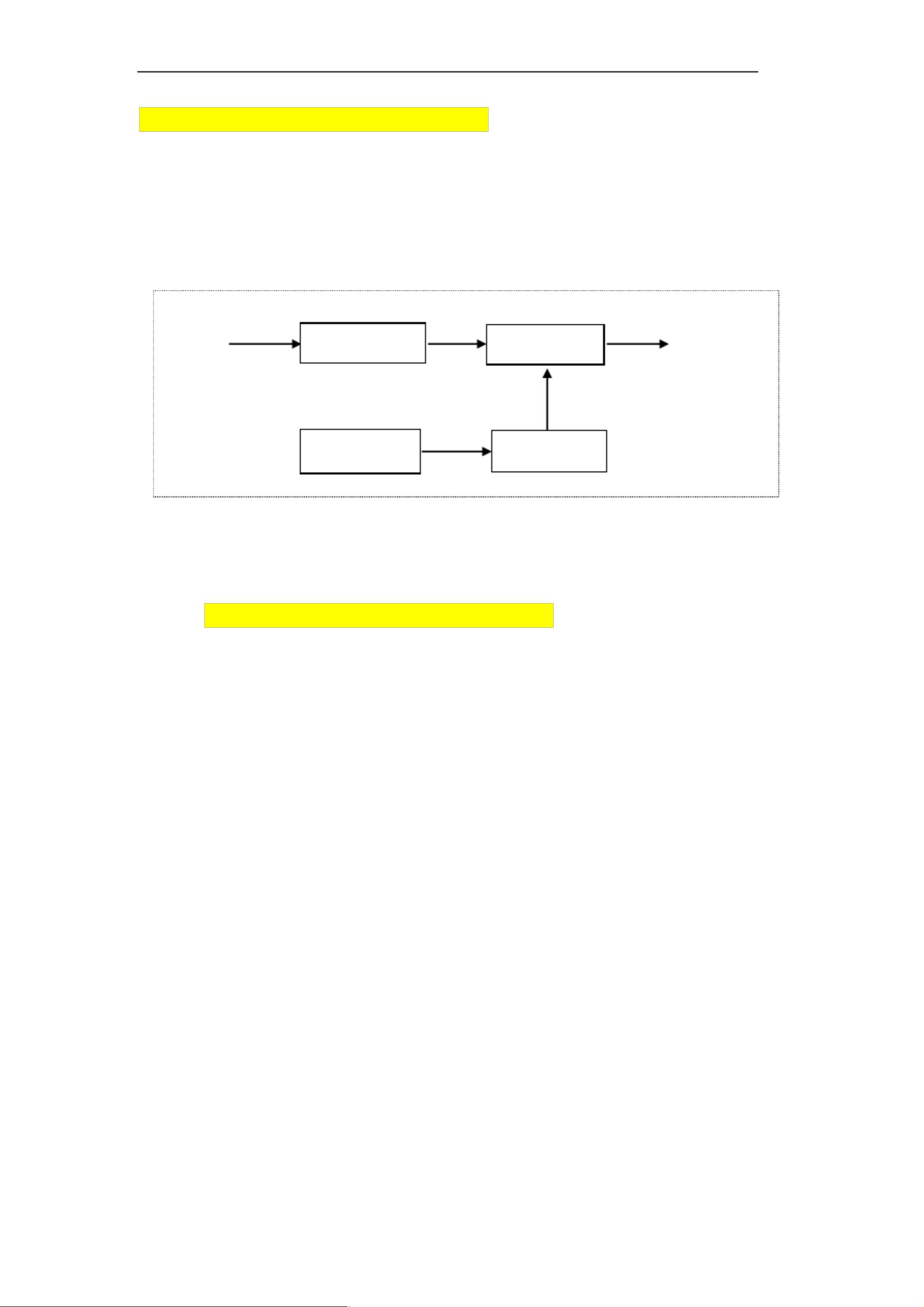

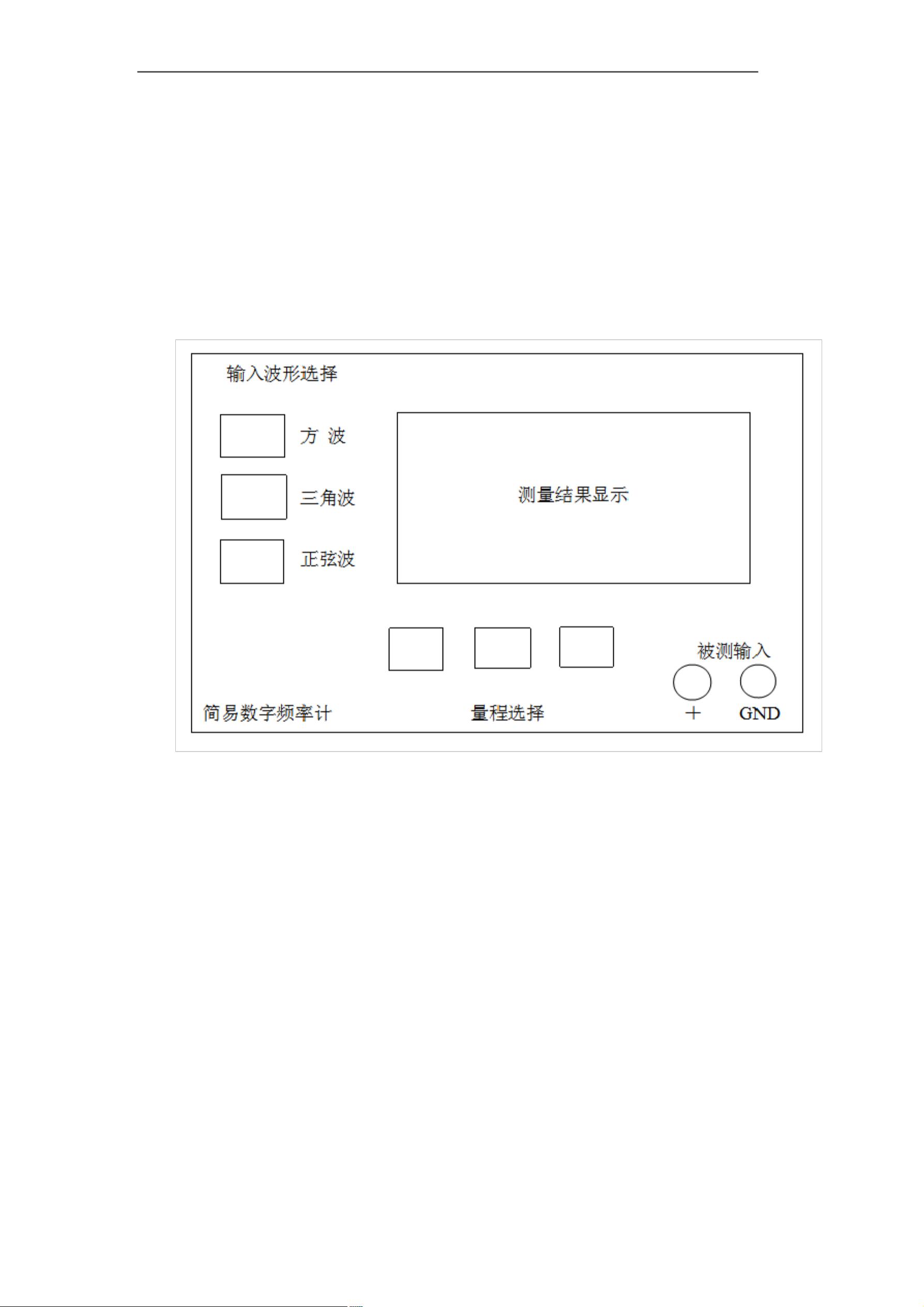

在系统设计部分,文档给出了数字频率计的系统框图,包括各个组成部分的功能介绍。系统通常包含信号输入、预处理电路(如放大整形)、计数器、时钟分频器、控制逻辑以及结果显示模块等。计数器记录在特定时间间隔内输入信号的脉冲数,通过计算脉冲数和时间间隔,可以得到信号的频率。

此外,文章可能还涵盖了Verilog HDL的基本语法和设计流程,例如模块定义、结构化编程、时序逻辑描述等。学生可能还需要进行波形仿真,验证设计的正确性,以确保频率计能够准确测量不同频率的信号。

关键词指出,设计中会涉及到周期计算、电子设计自动化工具(EDA)、数字频率计的硬件描述语言实现等关键概念。

这份课程设计涵盖了Verilog HDL的基础知识、电子计数器的工作原理,以及数字频率计的完整设计流程,旨在提升学生的硬件设计能力和实践经验。学生通过这个项目,不仅能深入理解频率测量技术,还能熟练掌握Verilog HDL语言在实际电路设计中的应用。

2022-10-14 上传

2022-06-21 上传

2021-07-13 上传

2021-07-13 上传

2022-06-19 上传

111 浏览量

2021-07-13 上传

苦茶子12138

- 粉丝: 1w+

- 资源: 7万+

最新资源

- Elasticsearch核心改进:实现Translog与索引线程分离

- 分享个人Vim与Git配置文件管理经验

- 文本动画新体验:textillate插件功能介绍

- Python图像处理库Pillow 2.5.2版本发布

- DeepClassifier:简化文本分类任务的深度学习库

- Java领域恩舒技术深度解析

- 渲染jquery-mentions的markdown-it-jquery-mention插件

- CompbuildREDUX:探索Minecraft的现实主义纹理包

- Nest框架的入门教程与部署指南

- Slack黑暗主题脚本教程:简易安装指南

- JavaScript开发进阶:探索develop-it-master项目

- SafeStbImageSharp:提升安全性与代码重构的图像处理库

- Python图像处理库Pillow 2.5.0版本发布

- mytest仓库功能测试与HTML实践

- MATLAB与Python对比分析——cw-09-jareod源代码探究

- KeyGenerator工具:自动化部署节点密钥生成