基于FPGA的16路彩灯控制器设计与实现

"基于FPGA的16路彩灯控制器设计,用于实现6种花型循环变化的彩灯效果,具备清零和速度选择功能。控制器由时序控制和显示控制两部分组成,使用VHDL语言进行源程序编写。"

在电子工程领域,FPGA(Field-Programmable Gate Array)是一种重要的可编程逻辑器件,它允许用户根据需求定制电路功能,广泛应用于各种电子系统设计中。与传统的单片机相比,FPGA具有更高的灵活性、更快的运算速度和更低的功耗,特别适合于需要高性能和快速响应的场景。

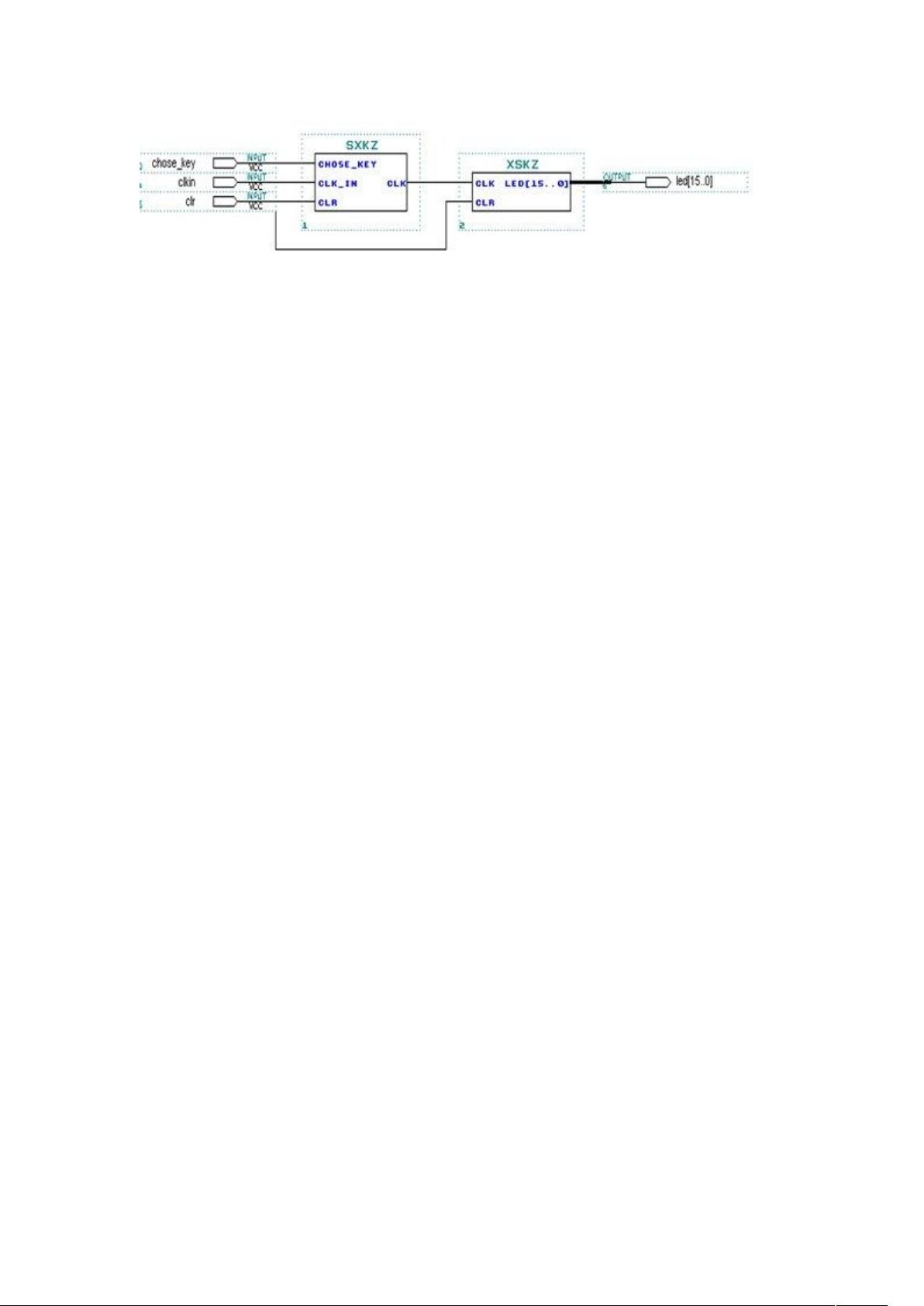

本项目是一个基于FPGA的多路彩灯控制器,旨在设计一个能够控制16路彩灯并展示6种不同花型循环变化的装置。控制器包括两个核心模块:时序控制电路(SXKZ)和显示控制电路(XSKZ)。这两个模块共同协作,根据输入信号如基准时钟CLK_IN、清零信号CLR和节奏选择开关CHOSE_KEY来决定彩灯的亮灭顺序和速度。

时序控制电路负责管理彩灯的变化节奏,它接收输入的时钟信号和清零信号,通过内部的状态机来产生控制彩灯亮灭的时序信号。状态机是一个关键的数字逻辑设计元素,它定义了系统在不同时间点的行为。在这个控制器中,状态机可能包括多个状态,每个状态对应一种特定的彩灯模式或转换动作。

显示控制电路则根据时序控制产生的信号,驱动16个输出信号LED[15..0],以控制16路彩灯的亮灭。设计者可以选择使用原理图或者文本元件例化的方式来构建这些模块,前者适合简单的系统,直观易懂,后者则适用于更复杂的设计,能够提供更清晰的模块组织。

VHDL(VHSIC Hardware Description Language)是一种硬件描述语言,常用于FPGA和CPLD的设计。在本项目中,VHDL源程序被用来描述时序控制器和显示控制器的行为,实现彩灯控制器的功能。通过编译和仿真VHDL代码,可以验证设计的正确性,然后将经过验证的设计下载到FPGA中,实现实际的硬件功能。

此外,该设计还包含了清零开关,允许用户在任何时候重置彩灯状态。同时,速度选择开关提供了快慢两种节奏,增加了系统的用户友好性和适应性。这样的设计不仅在理论上有很高的研究价值,而且在实际应用中,如节日装饰、舞台灯光、广告展示等领域,具有很大的商业潜力。

这个基于FPGA的多路彩灯控制器项目展示了如何利用现代电子设计自动化工具(EDA)和可编程逻辑器件来实现复杂且灵活的控制系统。它对于学习FPGA设计、数字逻辑和状态机实现的学生来说是一个很好的实践案例,同时在电子工程和相关领域中也有着实际的应用价值。

点击了解资源详情

点击了解资源详情

点击了解资源详情

110 浏览量

2012-01-03 上传

2012-03-31 上传

2009-05-07 上传

2020-08-14 上传

2010-01-06 上传

ljh1239789339

- 粉丝: 1

- 资源: 1

最新资源

- Elasticsearch核心改进:实现Translog与索引线程分离

- 分享个人Vim与Git配置文件管理经验

- 文本动画新体验:textillate插件功能介绍

- Python图像处理库Pillow 2.5.2版本发布

- DeepClassifier:简化文本分类任务的深度学习库

- Java领域恩舒技术深度解析

- 渲染jquery-mentions的markdown-it-jquery-mention插件

- CompbuildREDUX:探索Minecraft的现实主义纹理包

- Nest框架的入门教程与部署指南

- Slack黑暗主题脚本教程:简易安装指南

- JavaScript开发进阶:探索develop-it-master项目

- SafeStbImageSharp:提升安全性与代码重构的图像处理库

- Python图像处理库Pillow 2.5.0版本发布

- mytest仓库功能测试与HTML实践

- MATLAB与Python对比分析——cw-09-jareod源代码探究

- KeyGenerator工具:自动化部署节点密钥生成