Lattice Reveal逻辑分析仪快速入门与调试技巧

需积分: 34 2 浏览量

更新于2024-09-12

收藏 520KB PDF 举报

"Lattice Reveal逻辑分析仪使用指南"

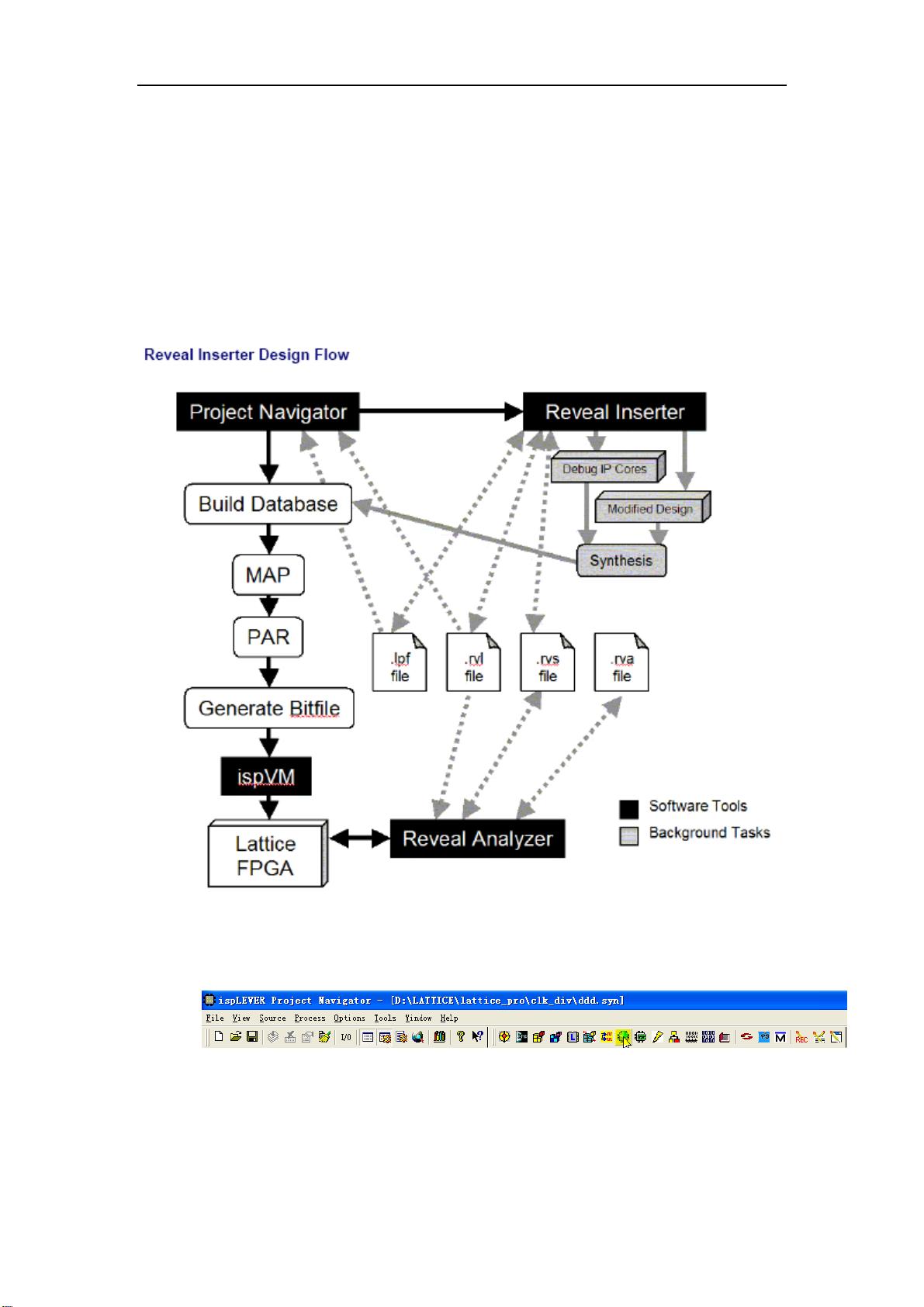

Lattice Reveal逻辑分析仪是一款专为Lattice半导体公司的可编程逻辑器件(PLD)设计的高效调试工具,尤其适用于ECP、XP、XP2、ECP2、ECP2S、ECP2M、ECP2MS、SC和SCM系列器件。其突出优势在于简化了使用流程,提高了用户体验。通过集成在Lattice的开发平台ISPLEVER 7.0中,Reveal逻辑分析仪可以帮助开发者轻松地进行FPGA设计的验证和调试。

使用Reveal逻辑分析仪的步骤大致如下:

1. 首先,你需要创建一个新的工程,这可以通过导入VHDL、VERILOG代码或EDIF网表来完成。这取决于你的设计流程,是基于RTL(寄存器传输级)还是基于网表。

2. 接下来,利用ISPLEVER工具栏上的Reveal Inserter按钮,启动逻辑分析仪的插入功能。这将把逻辑分析仪的核心插入到你的FPGA设计中,以便捕获和分析信号。

3. 在Reveal工程中,你可以创建多个数据集(CORE),每个数据集可以独立设置,最多可创建16个。数据集允许你针对不同的信号和条件进行独立的分析。

4. 在“Sample Clock”部分,你需要选择或添加一个或多个采样时钟信号。Reveal逻辑分析仪支持多时钟域调试,这意味着你可以使用不同频率的时钟来采样数据。

5. 设置数据采样深度和是否包含触发信号。这决定了你能捕获的数据量和触发事件的类型。

6. 在“Trigger Signal Setup”阶段,你可以配置触发条件。最多可以设置256个触发条件,并且支持多种操作类型,如相等、不等、大于、小于、大于等于、小于等于、上升沿、下降沿以及串行比较。

7. 特别地,Reveal逻辑分析仪提供了一种名为“TOKEN”的自定义类型,这对于调试状态机非常有用。你可以通过在触发单元中编辑radix(基数)来定义TOKEN,从而可视化状态机的转换。

编辑TOKEN类型的操作是在Inserter对话框中进行的,你可以直接从左侧的信号节点列表拖拽到触发单元列表中,然后定制相应的触发条件。

Lattice Reveal逻辑分析仪是Lattice FPGA开发过程中不可或缺的工具,它简化了调试过程,提高了设计效率,尤其是对于复杂的状态机调试和多时钟域系统,其功能尤为强大。通过熟练掌握Reveal的使用,开发者能够更快地定位和解决问题,从而加速项目的完成。

748 浏览量

点击了解资源详情

370 浏览量

748 浏览量

119 浏览量

2022-07-15 上传

2022-09-22 上传

225 浏览量

xidian340

- 粉丝: 0

- 资源: 5

最新资源

- 冰箱温度智能控制系统的设计

- MATLAB常用命令

- PLSQL渐进学习教程

- c语言编写的小游戏程序

- div css合成教材

- SQL+Server数据库设计和高级查询(SQL+Advance)2_1

- NET 数据访问架构指南

- ArcGIS平台开发框架介绍及其未来发展.pdf

- C#入门经典代码 Answers

- 模式识别(第二版)(作者:边肇祺) 习题答案

- 51单片机C语言入门教程

- 中国电信 smgp2。0协议

- excel_2003函数应用完全手册

- Software.Architecture.Design.Patterns.in.Java.pdf

- ArcEngine开发说明

- 北大青鸟 深入.NET平台和C#编程 教学资料 PPT6/9